Việc ngăn chặn sự lan truyền của các lỗi hệ thống trong quy trình từ thiết kế đến chế tạo chất bán dẫn ngày nay đòi hỏi nhiều bước xác nhận, phân tích và tối ưu hóa. Các công cụ liên quan đến quy trình này có thể bao gồm kiểm tra quy tắc thiết kế (DRC), xác minh hiệu chỉnh độ gần quang học (OPC), đo lường/kiểm tra viết mặt nạ và in wafer (để đánh giá quy trình), đo lường/kiểm tra in wafer và phân tích lỗi vật lý để xác nhận lỗi chẩn đoán. Việc trao đổi thông tin và đồng tối ưu hóa giữa các bước này là một quá trình phức tạp, với nhiều vòng lặp phản hồi chuyển tiếp và phản hồi. Giao tiếp thường bị cản trở bởi “bức tường” giữa các bộ phận khác nhau của quy trình công nghệ, làm chậm sự đổi mới. Tại hội nghị SPIE gần đây, Siemens EDA đã trình bày một bài phát biểu quan trọng đề xuất một loạt phương pháp tiếp cận nhằm phá vỡ những bức tường này nhằm cải thiện thiết kế chip cho quy trình sản xuất. Đọc tiếp để biết cách Siemens đặt mục tiêu phá bỏ các rào cản đổi mới bằng cách mở rộng hoạt động đồng tối ưu hóa công nghệ thiết kế.

Về bài phát biểu

SPIE là hiệp hội quốc tế về quang học và quang tử. Tổ chức này được thành lập từ năm 1955 và hội nghị của nó đã trở thành sự kiện hàng đầu về các chủ đề thiết kế và sản xuất tiên tiến. Tại sự kiện năm nay, Siemens đã trình bày bài phát biểu chính là chủ đề của bài đăng này. Có rất nhiều người đóng góp cho bài trình bày, trong đó có Lê Hồng, Fan Jiang, Yuansheng Ma, Srividya Jayaram, Joe Kwan, Siemens EDA (Hoa Kỳ); Doohwan Kwak, Siemens EDA (Hàn Quốc); Sankaranarayanan Paninjath Ayyappan, Siemens EDA (Ấn Độ). Tiêu đề của buổi nói chuyện là Mở rộng đồng tối ưu hóa công nghệ thiết kế từ khi ra mắt công nghệ đến HVM.

Buổi nói chuyện là một phần của phiên thảo luận về đồng tối ưu hóa công nghệ thiết kế (DTCO). Khái niệm này không phải là mới, nhưng Siemens đã xem xét ứng dụng của nó trên phạm vi rộng hơn của quy trình, từ thiết kế đến sản xuất số lượng lớn (HVM). Những ý tưởng và kết quả được trình bày có ý nghĩa quan trọng. Chúng ta hãy xem xét kỹ hơn.

Những gì đã được trình bày

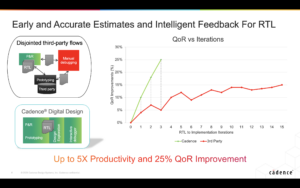

Đầu tiên, chúng tôi trình bày về hiện trạng sử dụng DTCO trên các phần chính của hệ sinh thái. Từ góc độ thiết kế, nhiều công ty tiên tiến có đội ngũ DFM đang nhận thấy những hạn chế của cách tiếp cận dựa trên mẫu. Điều thực sự cần thiết là công nghệ mới để tạo điều kiện thuận lợi cho việc học tập năng suất mà không phụ thuộc vào xưởng đúc.

Các xưởng đúc đang sử dụng các phương pháp học máy dựa trên mô hình mạnh mẽ, tốn kém nhưng không hoàn toàn hiệu quả. Họ cũng đang tìm cách khai thác thông tin hiệu quả từ dữ liệu sản xuất khổng lồ mà họ tạo ra. Các nhà cung cấp thiết bị và nhà cung cấp EDA đã hợp tác chặt chẽ hơn với nhau và đưa ra các giải pháp học máy hiệu quả hơn.

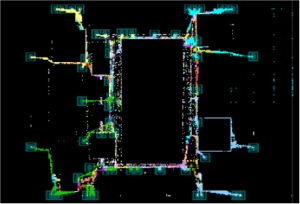

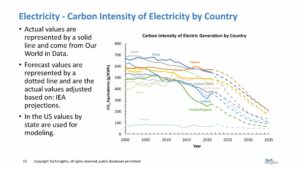

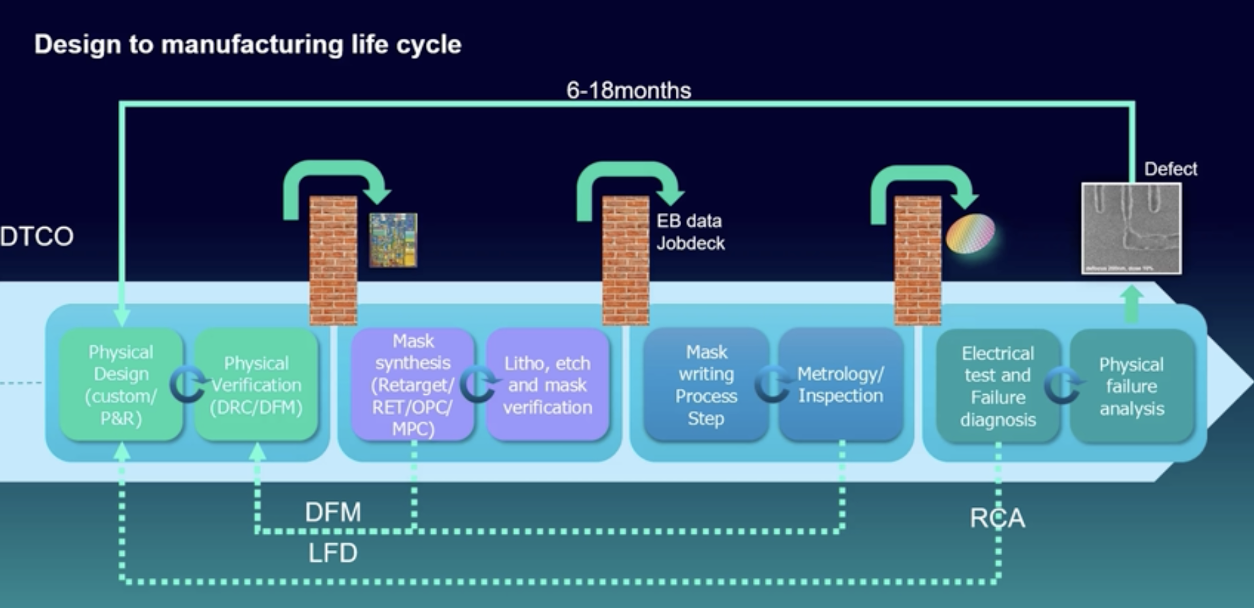

Lùi lại một chút, người ta chỉ ra rằng có những bức tường ngăn cách giữa giai đoạn thiết kế và sản xuất của quy trình. Các công ty Fabless tạo ra thiết kế, thực hiện DRC và thiết kế cho sản xuất (DFM), sau đó họ chuyển nó qua tường cho nhóm OPC/RET trong xưởng đúc hoặc IDM. Thiết kế thực hiện các nhiệm vụ như OPC và xác minh, sau đó dữ liệu được chuyển qua một bức tường khác để viết mặt nạ và đo lường/kiểm tra. Bức tường cuối cùng là để chế tạo. Tại đây, việc kiểm tra điện và phân tích lỗi sẽ được thực hiện. Vào thời điểm tìm ra được nguyên nhân gốc rễ của sự thất bại thì đã 6-18 tháng trôi qua. Đó là một vòng phản hồi rất dài. Đồ họa ở đầu bài này mô tả quá trình này.

DTCO cố gắng phá vỡ các bức tường, nhưng các phương pháp sẵn có vẫn chưa đầy đủ. DTCO truyền thống bắt đầu từ rất sớm trong quá trình phát triển quy trình. Bắt đầu với nhu cầu mở rộng quy mô, một ô tiêu chuẩn được xác định và quá trình tổng hợp, vị trí và lộ trình được thực hiện để đưa ra các mẫu cơ bản cũng như đo lường hiệu suất và công suất. Việc tạo SRAM cũng được thực hiện và dữ liệu đó sẽ quay trở lại thiết kế ô tiêu chuẩn.

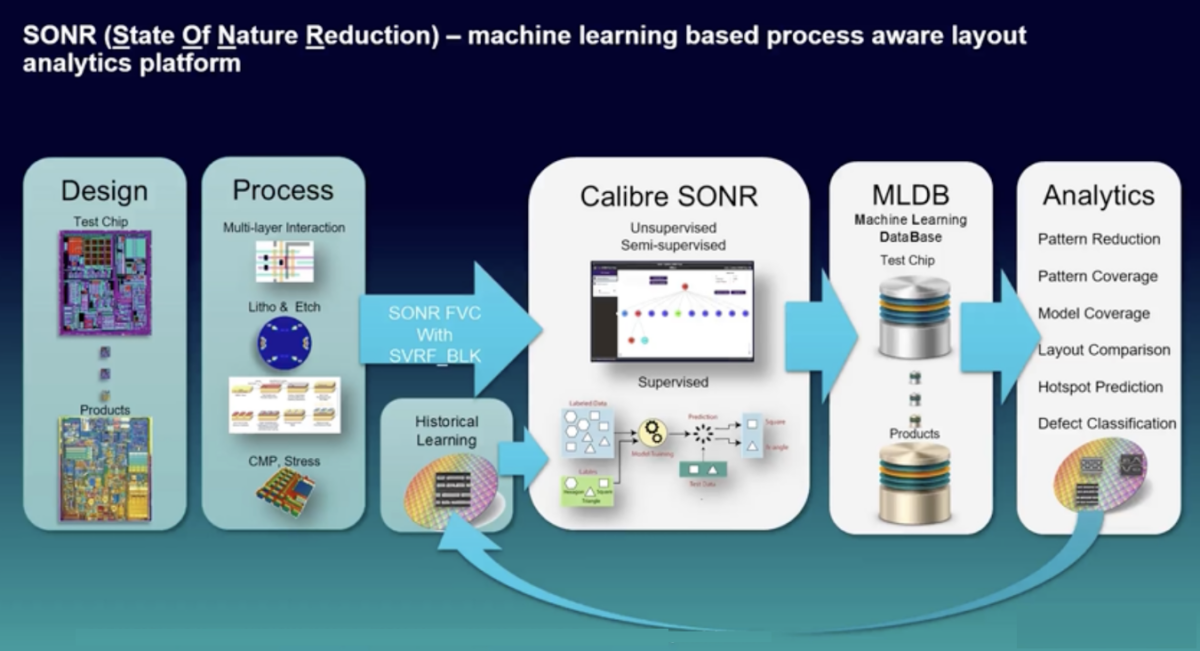

Những gì được trình bày tại bài phát biểu quan trọng của SPIE là một cách để mở rộng khái niệm đồng tối ưu hóa này cho toàn bộ quá trình từ thiết kế đến sản xuất. Cách tiếp cận này liên quan đến việc cho phép luồng thông tin dễ dàng hơn từ thiết kế đến quy trình cuối cùng và phân tích vật lý bằng cách tạo ra một kênh thông tin.

Mặc dù điều này nghe có vẻ đơn giản nhưng thực tế không phải vậy. Nhiều thách thức đã được thảo luận bằng những cách tiếp cận cụ thể để giảm thiểu vấn đề. Ví dụ: các thiết kế ban đầu có thể được tạo bằng trình tạo tổng hợp bố cục để giúp hiệu chỉnh quy trình cho các vấn đề thiết kế thực tế khi quy trình được phát triển. Điều này có thể làm giảm bớt nhiều bất ngờ hiện đang phải đối mặt với việc cắt băng quy trình ban đầu.

Xử lý khối lượng dữ liệu khổng lồ là một thách thức khác. Bằng cách sử dụng các kỹ thuật nén phức tạp mới, có thể cải thiện được 30X. Điều này cải thiện các nhiệm vụ xử lý và phân tích dữ liệu khá nhiều. Một khái niệm được gọi là AI có thể giải thích có thể giúp tìm ra nguyên nhân gốc rễ của vấn đề nhanh hơn nhiều. Khả năng đào tạo lại các mô hình AI sau này trong quá trình sản xuất mà không làm mất hiệu lực các kết quả trước đó là một lĩnh vực khác cần cải thiện. Ngoài ra, trong lĩnh vực phân tích dữ liệu còn có các kỹ thuật để xử lý “dữ liệu mất cân bằng”. Ví dụ: có thể có một điểm nóng được tìm thấy trong 100,000,000 mẫu.

Kết hợp tất cả những điều này lại với nhau có thể tạo ra một luồng thiết kế từ đầu đến cuối hiệu quả hơn nhiều, như minh họa trong hình bên dưới.

Để tìm hiểu thêm

Tác động của các phương pháp được nêu trong bài trình bày quan trọng này là rất đáng kể. Bạn có thể xem bản trình bày và truy cập sách trắng về quy trình tại đây. Có rất nhiều thông tin hữu ích có thể thu được. Và đó là cách Siemens đặt mục tiêu phá vỡ các rào cản đổi mới bằng cách mở rộng khả năng đồng tối ưu hóa công nghệ thiết kế.

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- : có

- :là

- :không phải

- $ LÊN

- 000

- 100

- 2023

- a

- có khả năng

- truy cập

- ngang qua

- địa chỉ

- tiên tiến

- AI

- Mô hình AI

- Mục tiêu

- Tất cả

- giảm bớt

- Ngoài ra

- an

- phân tích

- và

- Một

- Các Ứng Dụng

- phương pháp tiếp cận

- cách tiếp cận

- LÀ

- KHU VỰC

- AS

- At

- Nỗ lực

- có sẵn

- trở lại

- rào cản

- cơ bản

- BE

- trở nên

- được

- phía dưới

- giữa

- Một chút

- Nghỉ giải lao

- rộng hơn

- nhưng

- by

- gọi là

- CAN

- Nguyên nhân

- nguyên nhân

- pin

- thách thức

- thách thức

- Kênh

- kiểm tra

- Chip

- gần gũi hơn

- CO

- Đến

- đến

- Giao tiếp

- Các công ty

- hoàn toàn

- phức tạp

- khái niệm

- bê tông

- Hội nghị

- Xác nhận

- đóng góp

- tốn kém

- tạo

- tạo ra

- Tạo

- Current

- Tình trạng hiện tại

- Hiện nay

- dữ liệu

- phân tích dữ liệu

- Ngày

- nhiều

- xác định

- phụ thuộc

- Thiết kế

- thiết kế

- chi tiết

- phát triển

- Phát triển

- chẩn đoán

- thảo luận

- thực hiện

- xuống

- drc

- Sớm hơn

- Đầu

- dễ dàng hơn

- hệ sinh thái

- Hiệu quả

- hiệu quả

- cho phép

- Cuối cùng đến cuối

- Toàn bộ

- Trang thiết bị

- Sự kiện

- ví dụ

- Sàn giao dịch

- thêm

- mở rộng

- phải đối mặt

- tạo điều kiện

- Không

- fan hâm mộ

- nhanh hơn

- thông tin phản hồi

- Hình

- cuối cùng

- Tìm kiếm

- dòng chảy

- Trong

- tìm thấy

- Foundry

- từ

- đạt được

- đo

- máy phát điện

- đồ họa

- Xử lý

- Có

- giúp đỡ

- tại đây

- Hồng

- NÓNG BỨC

- Độ đáng tin của

- HTTPS

- ý tưởng

- Va chạm

- hàm ý

- nâng cao

- cải thiện

- cải thiện

- in

- bao gồm

- Bao gồm

- Ấn Độ

- thông tin

- sự đổi mới

- Quốc Tế

- tham gia

- liên quan đến

- các vấn đề

- IT

- ITS

- joe

- Key

- Chủ âm

- korea

- một lát sau

- phóng

- Bố trí

- LEARN

- học tập

- giới hạn

- dài

- Xem

- nhìn

- Rất nhiều

- máy

- học máy

- sản xuất

- nhiều

- mặt nạ

- lớn

- max-width

- Có thể..

- đo

- phương pháp

- Khai thác mỏ

- Giảm nhẹ

- mô hình

- tháng

- chi tiết

- hiệu quả hơn

- nhiều

- Cần

- cần thiết

- Mới

- of

- thường

- on

- ONE

- quang học

- Quang học và quang tử

- tối ưu hóa

- or

- cơ quan

- ra

- nêu

- kết thúc

- Giấy

- một phần

- các bộ phận

- thông qua

- mô hình

- thực hiện

- hiệu suất

- thực hiện

- quan điểm

- vật lý

- Nơi

- nền tảng

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- có thể

- Bài đăng

- quyền lực

- Thủ tướng

- trình bày

- trình bày

- in ấn

- vấn đề

- quá trình

- tuyên truyền

- đề xuất

- khá

- Đọc

- thực

- có thật không

- gần đây

- Cộng hòa

- đòi hỏi

- Kết quả

- nguồn gốc

- Route

- Quy tắc

- mở rộng quy mô

- phạm vi

- xem

- nhìn thấy

- tìm kiếm

- bán dẫn

- Loạt Sách

- Phiên

- thể hiện

- Siemens

- có ý nghĩa

- Chậm

- Xã hội

- Giải pháp

- tinh vi

- Spot

- Tiêu chuẩn

- Bắt đầu

- bắt đầu

- Tiểu bang

- Bang

- Các bước

- đáng kể

- như vậy

- bất ngờ

- tổng hợp

- sợi tổng hợp

- Hãy

- Thảo luận

- nhiệm vụ

- nhóm

- kỹ thuật

- Công nghệ

- thử nghiệm

- việc này

- Sản phẩm

- sau đó

- Đó

- Kia là

- họ

- điều này

- thời gian

- Yêu sách

- đến

- hôm nay

- bên nhau

- công cụ

- hàng đầu

- chủ đề

- Chủ đề

- quăng

- quăng

- truyền thống

- Kỳ

- Hoa Kỳ

- Sử dụng

- thông tin hữu ích

- sử dụng

- xác nhận

- khác nhau

- nhà cung cấp

- Xác minh

- rất

- thông qua

- khối lượng

- Tường

- là

- Đường..

- là

- Điều gì

- Là gì

- cái nào

- trắng

- giấy trắng

- sẽ

- với

- ở trong

- không có

- đang làm việc

- viết

- Năng suất

- năng suất

- bạn

- zephyrnet