Các nhà thiết kế vi mạch tương tự có thể dành quá nhiều thời gian và công sức để sử dụng lại các phương pháp lặp thủ công, cũ, quen thuộc để thiết kế mạch, chỉ vì đó là cách nó luôn được thực hiện. Tối ưu hóa mạch là một phương pháp EDA có thể tự động định cỡ tất cả các bóng bán dẫn trong một ô, bằng cách chạy mô phỏng SPICE trên các góc PVT và các biến thể xử lý, để đáp ứng các yêu cầu thiết kế tín hiệu tương tự và tín hiệu hỗn hợp. Nghe có vẻ hứa hẹn, phải không?

Vì vậy, tôi nên cân nhắc sử dụng trình tối ưu hóa mạch nào?

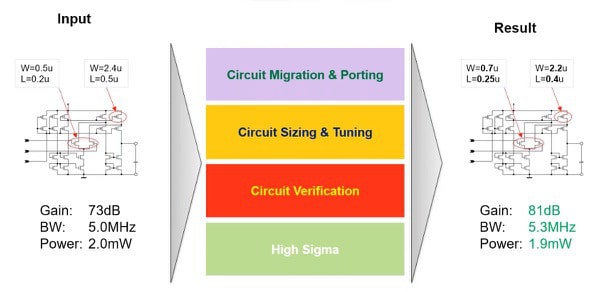

Để trả lời câu hỏi đó, sắp có một hội thảo trên web, được tổ chức bởi MunEDA, một công ty EDA bắt đầu hoạt động trở lại vào năm 2001 và tất cả là về trình tối ưu hóa mạch của họ có tên WiCkeD. Đầu vào là một danh sách mạng SPICE cùng với các yêu cầu thiết kế, như: mức tăng, băng thông và mức tiêu thụ điện năng. Đầu ra là một danh sách mạng có kích thước đáp ứng hoặc vượt quá yêu cầu thiết kế.

Điểm bí mật với WiCkeD là cách nó xây dựng mô hình Học máy (ML) để chạy Thiết kế thử nghiệm (DOE) nhằm tính toán góc PVT trong trường hợp xấu nhất, tìm độ nhạy hình học của bóng bán dẫn và thậm chí tính toán Biến thể trên chip (OCV) ) độ nhạy cảm. Cách tiếp cận này tạo và cập nhật mô hình ML nhiều chiều, phi tuyến tính từ dữ liệu mô phỏng.

Có một mô hình ML cho phép công cụ giải quyết thách thức tối ưu hóa, sau đó thực hiện xác minh cuối cùng bằng cách chạy mô phỏng SPICE. Có các lần lặp lại tự động cho đến khi tất cả các yêu cầu được đáp ứng. Điều đó nghe có vẻ nhanh hơn nhiều so với các phương pháp lặp thủ công cũ. Việc đào tạo mô hình ML hoàn toàn tự động và khá hiệu quả.

Các nhà thiết kế mạch cũng sẽ học:

- Nơi sử dụng tối ưu hóa mạch

- Những loại mạch nào là tốt để tối ưu hóa

- Tối ưu hóa mạch mang lại bao nhiêu giá trị cho quy trình thiết kế

Các kỹ sư tại STMicroelectronics đã sử dụng tính năng tối ưu hóa mạch trong WiCkeD và MunEDA nói về những kết quả cụ thể của họ trong việc tiết kiệm thời gian và cải tiến trong việc đáp ứng các yêu cầu. Công ty khuếch đại công suất Inplay Technologies đã cho thấy kết quả tối ưu hóa mạch từ hội nghị DAC 2018.

Chi tiết hội thảo trên web

Xem hội thảo trên web vào ngày 11 tháng 10, XNUMX giờ sáng PDT bởi đăng ký trực tuyến.

Blog liên quan

Chia sẻ bài đăng này qua:- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :là

- $ LÊN

- 2001

- 2018

- a

- Giới thiệu

- ngang qua

- Tất cả

- luôn luôn

- và

- trả lời

- phương pháp tiếp cận

- Tháng Tư

- LÀ

- At

- Tự động

- Tự động

- tự động

- trở lại

- Băng thông

- bởi vì

- Mang lại

- xây dựng

- by

- tính toán

- CAN

- thách thức

- Chip

- đến

- công ty

- Hội nghị

- Hãy xem xét

- tiêu thụ

- Corner

- góc

- tạo ra

- dữ liệu

- Thiết kế

- thiết kế

- DOE

- hiệu quả

- nỗ lực

- cho phép

- Ngay cả

- quá

- quen

- nhanh hơn

- cuối cùng

- Tìm kiếm

- dòng chảy

- Trong

- từ

- Thu được

- hình học

- tốt

- Có

- tổ chức

- Độ đáng tin của

- HTTPS

- i

- cải tiến

- in

- IT

- sự lặp lại

- sự lặp lại

- jpg

- LEARN

- học tập

- Lượt thích

- máy

- học máy

- nhãn hiệu

- max-width

- Gặp gỡ

- cuộc họp

- Đạt

- phương pháp

- ML

- kiểu mẫu

- Được đặt theo tên

- of

- Xưa

- on

- tối ưu hóa

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Bài đăng

- quyền lực

- quá trình

- năng suất

- hứa hẹn

- câu hỏi

- Yêu cầu

- Kết quả

- chạy

- chạy

- Tiết kiệm

- Bí mật

- nên

- mô phỏng

- Kích thước máy

- riêng

- tiêu

- gia vị

- bắt đầu

- Các cuộc đàm phán

- Công nghệ

- việc này

- Sản phẩm

- cung cấp their dịch

- thời gian

- đến

- quá

- công cụ

- Hội thảo

- loại

- Cập nhật

- sử dụng

- giá trị

- Xác minh

- thông qua

- Đường..

- webinar

- cái nào

- sẽ

- với

- zephyrnet