S2C đã dẫn đầu toàn cầu về tạo mẫu FPGA trong gần hai thập kỷ nay và các nền tảng tạo mẫu FPGA của nó đã theo dõi chặt chẽ sự sẵn có của các FPGA mới nhất – bao gồm các FPGA mới nhất của cả Xilinx và Intel. Và họ chắc chắn đang thực hiện đúng lời hứa nâng cao các giải pháp tạo mẫu của mình cho việc tạo mẫu thiết kế siêu quy mô – mở rộng quy mô khả năng và khả năng của nền tảng tạo mẫu để hỗ trợ các thiết kế nhiều tỷ cổng.

Nhìn lại đầu quý 4 năm 2020, S2C đã công bố hỗ trợ cho các FPGA Xilinx VU19P UltraScale+ mới, cung cấp các nền tảng tạo mẫu FPGA đơn, kép và bốn. Sau đó, vào tháng 2020 năm 2, S8C tiếp tục công bố dòng nền tảng tạo mẫu Prodigy Logic Matrix mật độ cao với 8 FPGA trên mỗi Ma trận Logic, 64 Ma trận Logic trên mỗi giá máy chủ (440 FPGA) và kết nối của nhiều giá đỡ máy chủ với nhau. Các lần lặp lại đầu tiên của Ma trận logic được phân phối với các FPGA Xilinx VUXNUMX (được gọi là LX1) cho những khách hàng sớm nóng lòng chờ đợi phiên bản VU19P (được mệnh danh là LX2).

Giờ đây, S2C đang đẩy mạnh trò chơi Ma trận logic của mình với LX2, giúp tăng công suất cổng có thể sử dụng nguyên mẫu lên 60% so với phiên bản VU440! Nhiều cổng có thể sử dụng hơn trên mỗi FPGA có nghĩa là ít FPGA hơn, ít kết nối FPGA hơn và hiệu suất cao hơn cho cùng một thiết kế nguyên mẫu. Với công suất cổng ước tính là 392 triệu cổng mỗi LX2, một giá đỡ máy chủ tiêu chuẩn được điền đầy đủ với 8 LX2 cho phép khả năng tạo nguyên mẫu ước tính hơn 3 tỷ cổng ASIC!

Hình 1: Ma trận Logic thần đồng LX2

| Gia đình ma trận logic thần đồng | ||

| LX1 | LX2 | |

| FPGA | XCGU440 | XCGU19P |

| Cổng ASIC ước tính (M) | 240 | 392 |

| Số lượng FPGA | 8 | 8 |

| Ô logic hệ thống (K) | 44,328 | 71,504 |

| Bộ nhớ FPGA (Mb) | 709 | 1,327.2 |

| Lát DSP | 23,040 | 30,720 |

| I/O người dùng bên ngoài | 9,216 | 10,368 |

| Bộ thu phát SerDes | Tải Tập 384 | 640 GTY |

| Kết nối thần đồng | 64 | 72 |

| Đầu nối PGT | 8 | 0 |

| Đầu nối thu phát | 80 MSAS mỗi cái có 4 GTH + 8 IO | 160 MCIO mỗi cái với 4 GTY + 8 IO |

| Hiệu suất SerDes | 16 Gbps | 28 Gbps |

Hình 2: Họ ma trận logic

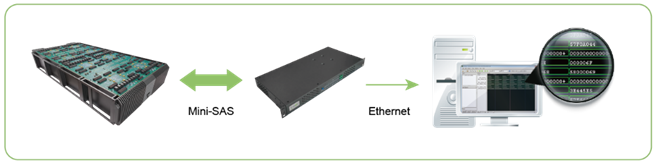

Kết nối linh hoạt, tốc độ cao là chìa khóa để tạo mẫu FPGA mật độ cao và Ma trận logic hỗ trợ chiến lược kết nối 3 cấp, phân cấp: Cầu ngắn để kết nối giữa các FPGA lân cận; liên kết hệ thống cho kết nối cáp FPGA băng thông cao, và chuyển liên kết để kết nối FPGA SerDes khoảng cách xa hơn qua cáp MCIO. Để đơn giản hóa kết nối FPGA và tối đa hóa giá trị của chuyển liên kết, Luồng phân vùng của S2C hỗ trợ Ghép kênh chân thu phát tốc độ cao (HSTPM) mới được giới thiệu của Xilinx, đơn giản hóa việc truyền tín hiệu chính xác theo chu kỳ, ghép kênh chân và kết nối FPGA SerDes có độ trễ thấp.

Để giảm thiểu thời gian tạo mẫu và tối đa hóa năng suất tạo mẫu, các công cụ năng suất tạo mẫu khác của S2C được thiết kế có tính đến Ma trận logic, bao gồm Trình phát Pro Thời gian chạy phần mềm – và các công cụ tạo mẫu S2C bổ trợ bao gồm Cầu Proto, MDM chuyên nghiệpvà S2C IP sẵn sàng cho mẫu thử nghiệm.

Trình phát Pro Thời gian chạy phần mềm được bao gồm với LX2, cung cấp các tính năng tiện lợi như quản lý đồng hồ tiên tiến, tự kiểm tra tích hợp, phát hiện bo mạch tự động, lập trình điện áp I/O, tải xuống nhiều FPGA cũng như giám sát và quản lý hệ thống từ xa. Ngoài ra còn có AXEVision, một công cụ gỡ lỗi AXI-over-Ethernet tích hợp để đơn giản hóa việc gỡ lỗi từ xa các thiết kế liên quan đến AXI.

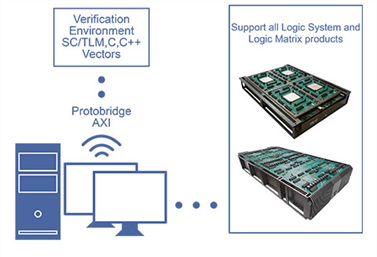

Cầu Proto hỗ trợ truyền dữ liệu thông lượng cao (lên đến 1GB/giây) giữa PC chủ và LX2 – cho phép chuyển số lượng lớn giao dịch được mô hình hóa bằng phần mềm, luồng video hoặc kích thích thử nghiệm khác để xác thực hệ thống.

Hình 3: ProtoBridge

MDM chuyên nghiệp có tính năng gỡ lỗi theo dõi sâu với các bộ kích hoạt chéo cho tối đa tám FPGA, xem theo dõi tín hiệu đa FPGA từ một cửa sổ xem duy nhất, 64GB dung lượng lưu trữ dạng sóng theo dõi bên ngoài, tốc độ lấy mẫu theo dõi lên tới 125 MHz và hỗ trợ các ngôn ngữ máy trạng thái kích hoạt để chụp dấu vết phức tạp yêu cầu.

Hình 4: MDM Pro

S2C's cũng cung cấp một thư viện phong phú về IP sẵn sàng cho mẫu thử nghiệm cho LX2 – Thẻ con gái plug-and-play – tăng tốc độ tạo môi trường nguyên mẫu xung quanh nguyên mẫu FPGA.

Hình 5: Thẻ con gái IP sẵn sàng nguyên mẫu

Thần đồng logic ma trận LX2 hiện có sẵn. Để biết thêm thông tin, vui lòng liên hệ với đại diện bán hàng S2C tại địa phương của bạn hoặc truy cập www.s2ceda.com.

Chia sẻ bài đăng này qua: Nguồn: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Add-on

- công bố

- Thông báo

- xung quanh

- ASIC

- sẵn có

- Tỷ

- bảng

- cáp

- Sức chứa

- liên quan

- Kết nối

- khách hàng

- dữ liệu

- phân phối

- Thiết kế

- Phát hiện

- khoảng cách

- Đầu

- Môi trường

- gia đình

- Tính năng

- Sung

- Tên

- dòng chảy

- fpga

- trò chơi

- Gates

- Toàn cầu

- HTTPS

- Bao gồm

- thông tin

- Intel

- IP

- Key

- Ngôn ngữ

- lớn

- mới nhất

- Thư viện

- địa phương

- quản lý

- Matrix

- triệu

- giám sát

- cung cấp

- Cung cấp

- Nền tảng khác

- PC

- hiệu suất

- nền tảng

- Nền tảng

- pro

- năng suất

- Công cụ năng suất

- Lập trình

- tạo mẫu

- Giá

- Yêu cầu

- bán hàng

- mở rộng

- Phần mềm

- Giải pháp

- Tiểu bang

- kích thích kinh tế

- là gắn

- Chiến lược

- dòng

- hỗ trợ

- Hỗ trợ

- hệ thống

- thử nghiệm

- Giao dịch

- giá trị

- Video

- chờ đợi

- CHÚNG TÔI LÀ