Trong thuật ngữ mạch tích hợp, sụt áp là hiện tượng sụt áp xảy ra trong mạch. Đây là một hiện tượng phổ biến và có thể xảy ra vì những lý do sau. Nguồn điện giảm xuống dưới phạm vi hoạt động mà chip được thiết kế dành cho đó, dẫn đến hiện tượng sụt giảm. Dòng điện được các phần tử dẫn điện tiêu thụ nhiều hơn mức thiết kế, dẫn đến hiện tượng sụt giảm. Đôi khi, nhiễu tín hiệu hoặc nhiễu trên nguồn điện cũng có thể gây ra dao động điện áp, dẫn đến sụt áp.

Sự sụt giảm có thể ảnh hưởng đến hoạt động của mạch điện. Hiệu suất của chip giảm, dẫn đến thời gian xử lý lâu hơn là một trong những tác động như vậy. Nhưng sau đây là một số tác động nghiêm trọng và/hoặc thảm khốc hơn. Con chip có thể tiêu thụ nhiều dòng điện hơn để duy trì mức hiệu suất, dẫn đến tăng mức tiêu thụ điện năng và tản nhiệt. Điều này có thể dẫn đến giảm tuổi thọ của chip và trong trường hợp nghiêm trọng, chip bị hỏng hoàn toàn do các biến thể thiết lập và lưu giữ. Dropops cũng có thể gây ra hỏng dữ liệu hoặc lỗi ở đầu ra. Đây là một vấn đề rất nghiêm trọng đối với các ứng dụng phụ thuộc vào độ chính xác và độ tin cậy của chip.

Đương nhiên, hiện tượng rớt mạng được xem xét nghiêm túc khi thiết kế chip và hệ thống. Các phương pháp phổ biến nhất để giảm thiểu tình trạng sụt nguồn là tách nguồn điện, điều chỉnh điện áp, tối ưu hóa mạch và quản lý nguồn điện ở cấp hệ thống. Các điều kiện và môi trường hoạt động mà chip sẽ hoạt động được xem xét cẩn thận khi thiết kế các giải pháp giảm thiểu hiện tượng rớt mạng.

Vấn đề thời hiện đại

Khi SoC trở nên phức tạp hơn, các vấn đề về rớt mạng cũng có thể trở nên khá phức tạp. Thiết kế của SoC cần phải được tối ưu hóa về hiệu suất, công suất, chi phí, kiểu dáng, v.v. bên cạnh việc tối ưu hóa để giảm thiểu hiện tượng rớt mạng. Đôi khi các mục tiêu tối ưu hóa này có thể cạnh tranh với nhau và phải thực hiện sự đánh đổi. Ví dụ: các kiến trúc sư SoC có thể tăng điện áp hoạt động, thêm biên độ để tránh tình trạng sụt giảm cục bộ và toàn cục, nhưng mức tăng này sẽ làm tăng công suất theo phương trình bậc hai. Ngoài ra, các nhà thiết kế có thể điều chỉnh thế hệ đồng hồ của họ để thích ứng với hiện tượng sụt giảm, điều này làm cho hiệu suất trở thành một chức năng của thời gian chuyển đổi thế hệ đồng hồ.

Do đó, các SoC lớn trong không gian điện toán trung tâm dữ liệu và AI đặc biệt dễ bị ngừng hoạt động. Khối lượng công việc của khách hàng rất đa dạng và năng động, dẫn đến những biến động đáng kể trong hoạt động chuyển đổi và mức rút hiện tại. Tất nhiên, các hệ thống không thể để các vấn đề về trạng thái ngừng hoạt động không được giải quyết. Trách nhiệm pháp lý tiềm ẩn do đầu ra không chính xác hoặc lỗi nghiêm trọng của chip là quá cao đối với các hệ thống và ứng dụng ngày nay.

Sự cố thả xuống cục bộ

Bộ tăng tốc dành riêng cho ứng dụng được sử dụng rộng rãi song song với các bộ xử lý đa năng để mang lại hiệu suất và hiệu quả sử dụng năng lượng cần thiết trong môi trường điện toán đòi hỏi khắt khe ngày nay. Nhưng những bộ tăng tốc này cũng như số lượng lõi ngày càng tăng và tính chất bất đối xứng của khối lượng công việc sẽ làm tăng nguy cơ sụt điện áp cục bộ. Những sụt giảm điện áp cục bộ này là kết quả của sự gia tăng đột ngột trong hoạt động chuyển mạch và có thể gây ra sự cố tạm thời cũng như khả năng xảy ra lỗi ở chế độ nhiệm vụ.

Khi xảy ra hiện tượng sụt giảm cục bộ, tác động có thể được giảm thiểu thông qua việc chia tần số động. Điều này đạt được bằng cách điều chỉnh thời gian của mạch bằng đồng hồ có thể lập trình. Đồng hồ có thể lập trình cho phép điều chỉnh tần số và thời gian đồng hồ một cách linh hoạt dựa trên các điều kiện hoạt động hiện tại của mạch.

Movellus giúp dễ dàng giải quyết tình trạng rớt mạng cục bộ

Movellus, nhà cung cấp IP hệ thống kỹ thuật số hàng đầu, đã phát triển dòng sản phẩm Aeonic Tạo để giải quyết tình trạng ngừng hoạt động cục bộ. Danh mục Movellus Aeonic cung cấp các giải pháp xung nhịp thích ứng mang lại khả năng phản hồi nhanh chóng. Danh mục đầu tư bao gồm hệ thống đồng hồ thích ứng. Các khối xây dựng được xây dựng bằng Verilog tổng hợp, làm cho chúng trở nên linh hoạt về bản chất. Các giải pháp này có thể cấu hình, có thể quét được và có thể xử lý linh hoạt cho nhiều ứng dụng SoC nâng cao.

Dòng sản phẩm Aeonic Generation cũng nhỏ hơn đáng kể so với các giải pháp analog truyền thống. Kết quả là, các nhà thiết kế có thể khởi tạo IP ở mức độ chi tiết cần thiết mà không có bất kỳ tác động đáng kể nào đến khu vực. Ngoài ra, khi các thiết kế chuyển sang hình học xử lý tinh tế hơn, khu vực Aeonic Generation tiếp tục mở rộng quy mô, khiến nó trở thành giải pháp lý tưởng cho các thiết kế trong tương lai.

Một vài trường hợp sử dụng

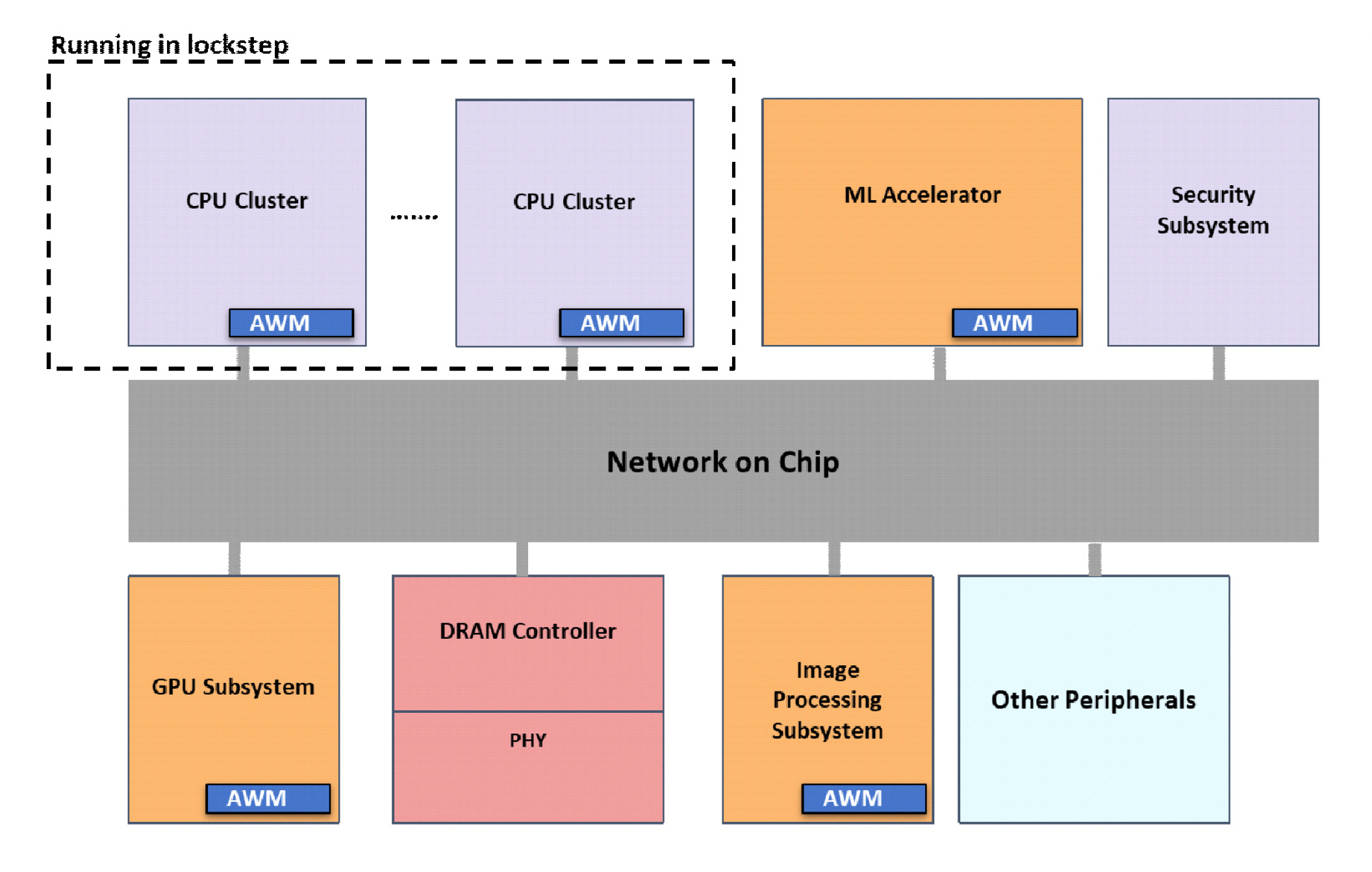

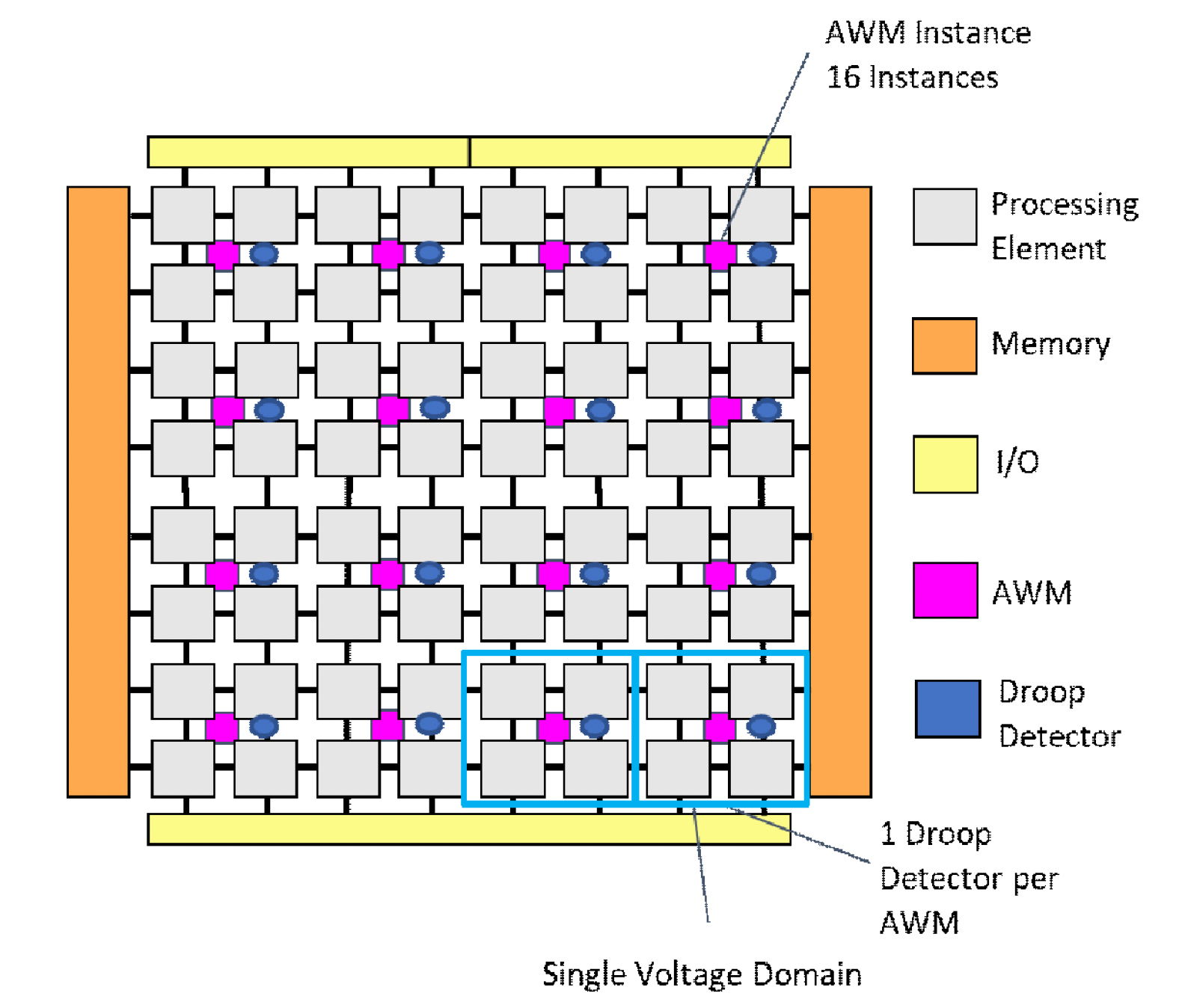

Hình sau đây của Movellus cho thấy kiến trúc ví dụ của bộ xử lý ADAS với Nền tảng Aeonic Tạo AWM để hỗ trợ giảm cục bộ. Kiến trúc sư sẽ ghép nối mô-đun AWM với một khối con hoặc bộ tăng tốc dành riêng cho ứng dụng để phản hồi tình trạng giảm cục bộ do khối lượng công việc điều khiển trong vòng năm chu kỳ xung nhịp với sự thay đổi tần số nhanh và ít trục trặc. Cách tiếp cận này cung cấp một giải pháp đáng tin cậy và hiệu quả để giải quyết các thách thức về tình trạng ngừng hoạt động cục bộ trong các thị trường mạng ADAS, 5G và trung tâm dữ liệu.

Hình sau đây của Movellus cho thấy kiến trúc mẫu của một biển bộ xử lý SoC với Aeonic Tạo để hỗ trợ giảm cục bộ. Kiến trúc sư sẽ ghép nối mô-đun Aeonic Tạo AWM với một bộ phát hiện độ sụt cho cụm bộ xử lý và miền điện áp liên quan để phản ứng nhanh chóng với tình trạng sụt giảm cục bộ do khối lượng công việc. Điều này cho phép các nhà thiết kế cung cấp phản hồi giảm cục bộ và độc lập mà không làm thay đổi hiệu suất của các cụm bộ xử lý lân cận.

Tổng kết

Hiện tượng sụt điện áp cục bộ có thể xảy ra trong các SoC không đồng nhất chứa các bộ tăng tốc dành riêng cho ứng dụng. Những sự cố này có thể dẫn đến trục trặc về thời gian, trục trặc nhất thời và lỗi ở chế độ nhiệm vụ trong ADAS, mạng trung tâm dữ liệu và các ứng dụng 5G. Kiến trúc sư hệ thống có thể triển khai đồng hồ thích ứng để ứng phó với tình trạng sụt giảm này và giảm thiểu tác động.

Dòng sản phẩm IP tạo xung nhịp hiệu suất cao Movellus™ Aeonic Tạo mô-đun khối lượng công việc thích ứng (AWM) là một phần của kiến trúc Mạng đồng hồ thông minh Aeonic™. Để biết thêm thông tin, hãy tham khảo Movellus' Trang Aeonic Generation™ AWM.

Cũng đọc:

Ưu điểm của miền xung nhịp đồng bộ quy mô lớn trong thiết kế chip AI

Đã đến lúc cho các mạng đồng hồ thông minh

Lợi ích về hiệu suất, năng lượng và diện tích (PPA) thông qua mạng đồng hồ thông minh

Chia sẻ bài đăng này qua:- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :là

- 5G

- a

- gia tốc

- máy gia tốc

- chính xác

- đạt được

- hoạt động

- thích ứng

- ADA

- Ngoài ra

- Ngoài ra

- địa chỉ

- giải quyết

- Điều chỉnh

- tiên tiến

- AI

- cho phép

- và

- các ứng dụng

- phương pháp tiếp cận

- kiến trúc

- LÀ

- KHU VỰC

- AS

- liên kết

- At

- dựa

- BE

- trở nên

- phía dưới

- Lợi ích

- Chặn

- Khối

- Xây dựng

- xây dựng

- by

- CAN

- Có thể có được

- không thể

- cẩn thận

- trường hợp

- thảm họa

- Nguyên nhân

- Trung tâm

- thách thức

- Chip

- Snacks

- Đồng hồ

- cụm

- Chung

- cạnh tranh

- hoàn thành

- phức tạp

- Tính

- máy tính

- điều kiện

- xem xét

- xem xét

- tiêu thụ

- liên tiếp

- tham nhũng

- Phí Tổn

- có thể

- Counter

- Couple

- khóa học mơ ước

- Current

- khách hàng

- chu kỳ

- dữ liệu

- Trung tâm dữ liệu

- Trung tâm dữ liệu

- ngày

- cung cấp

- yêu cầu

- Thiết kế

- thiết kế

- thiết kế

- thiết kế

- thiết kế

- phát triển

- kỹ thuật số

- phân phối

- khác nhau

- miền

- lĩnh vực

- rút ra

- Rơi

- Giọt

- năng động

- năng động

- mỗi

- hiệu quả

- hiệu quả

- các yếu tố

- Môi trường

- môi trường

- lỗi

- vv

- ví dụ

- Không

- Ngã

- gia đình

- Hình

- linh hoạt

- biến động

- tiếp theo

- Trong

- hình thức

- tần số

- từ

- chức năng

- tương lai

- mục đích chung

- tạo ra

- thế hệ

- được

- Toàn cầu

- Go

- Các mục tiêu

- xảy ra

- xảy ra

- Có

- Cao

- hiệu suất cao

- tổ chức

- HTTPS

- lý tưởng

- Va chạm

- Tác động

- thực hiện

- in

- không chính xác

- bao gồm

- Tăng lên

- tăng

- Tăng

- tăng

- độc lập

- thông tin

- tích hợp

- hội nhập

- Thông minh

- bản chất

- IP

- vấn đề

- các vấn đề

- IT

- lớn

- quy mô lớn

- dẫn

- hàng đầu

- Cấp

- trách nhiệm

- Cuộc sống

- địa phương

- còn

- thực hiện

- duy trì

- LÀM CHO

- Làm

- quản lý

- Lợi nhuận

- thị trường

- max-width

- phương pháp

- Giảm nhẹ

- giảm nhẹ

- giảm nhẹ

- mô-đun

- Modules

- chi tiết

- hầu hết

- di chuyển

- Thiên nhiên

- nhu cầu

- mạng

- mạng lưới

- Tiếng ồn

- đáng chú ý

- con số

- of

- Cung cấp

- on

- ONE

- hoạt động

- Hoạt động

- tối ưu hóa

- tối ưu hóa

- tối ưu hóa

- Nền tảng khác

- đầu ra

- một phần

- hiệu suất

- biểu diễn

- hiện tượng

- nền tảng

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- danh mục đầu tư

- Bài đăng

- tiềm năng

- quyền lực

- Điện nguồn

- quá trình

- xử lý

- Bộ xử lý

- bộ vi xử lý

- Sản phẩm

- nhà cung cấp dịch vụ

- cung cấp

- nâng cao

- phạm vi

- nhanh

- nhanh chóng

- Đọc

- thời gian thực

- lý do

- Giảm

- Quy định

- độ tin cậy

- đáng tin cậy

- cần phải

- Trả lời

- phản ứng

- kết quả

- kết quả

- Tăng lên

- Nguy cơ

- chạy

- Quy mô

- mở rộng quy mô

- SEA

- nghiêm trọng

- thiết lập

- nghiêm trọng

- Thay đổi

- Chương trình

- Tín hiệu

- có ý nghĩa

- đáng kể

- nhỏ hơn

- thông minh

- giải pháp

- Giải pháp

- một số

- Không gian

- như vậy

- đột ngột

- cung cấp

- hỗ trợ

- apt

- hệ thống

- hệ thống

- Tandem

- Công nghệ

- thuật ngữ

- việc này

- Sản phẩm

- Khu vực

- cung cấp their dịch

- Them

- Kia là

- Thông qua

- thời gian

- thời gian

- thời gian

- đến

- hôm nay

- quá

- truyền thống

- sử dụng

- rất đa dạng

- thông qua

- điện áp

- TỐT

- nổi tiếng

- cái nào

- rộng

- Phạm vi rộng

- rộng rãi

- sẽ

- với

- ở trong

- không có

- sẽ

- zephyrnet