TSMC đã cung cấp dịch vụ đúc từ năm 1987 và nút 3nm đầu tiên của họ được gọi là N3 và ra mắt vào năm 2022; bây giờ họ đã ra mắt nút 3nm nâng cao có tên là N3E. Sau đó, mỗi nút mới đều yêu cầu IP được thiết kế, mô tả và xác thực cẩn thận bằng silicon để đảm bảo rằng các thông số kỹ thuật của IP được đáp ứng và có thể được sử dụng một cách an toàn trong các thiết kế SoC. IP mới này phải bao gồm nhiều chức năng, như giao diện, bộ nhớ và logic. Synopsys có một nhóm IP lớn đã vượt qua thử thách bằng cách tạo IP mới cho nút TSMC N3E và đạt được thành công về silicon bước đầu.

Kết nối Chiplet

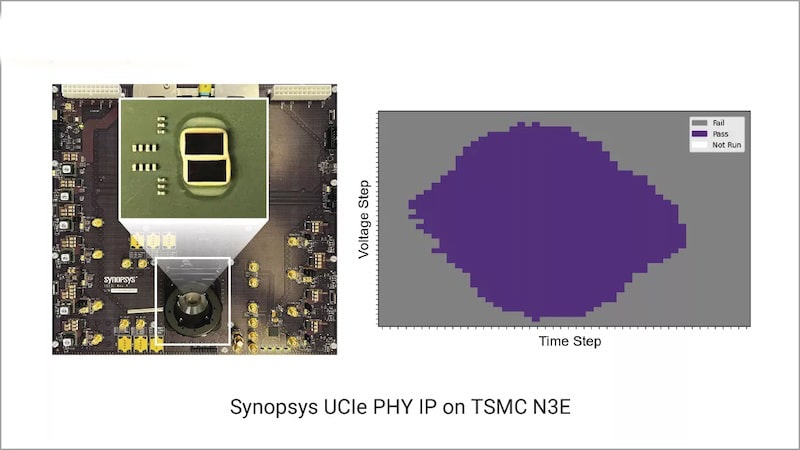

Các hệ thống được tạo thành từ các chiplet yêu cầu giao tiếp liên tục và đó là lúc tiêu chuẩn UCIe xuất hiện.ồ chơi. Synopsys là thành viên Cộng tác viên của Hiệp hội UCIevà họ cung cấp IP cho cả UCIe Ckiểm soát và UCIe PHY trong nút TSMC N3E.

Sản phẩm UCIe PHY IP có kết quả silicon đầu tiên vào tháng 2023 năm 16, cho thấy tốc độ dữ liệu là 24GB/s và có thể mở rộng lên 0.3GB/s trên mỗi kênh. Hiệu suất năng lượng ở mức XNUMX pJ/bit.

IP vật lý

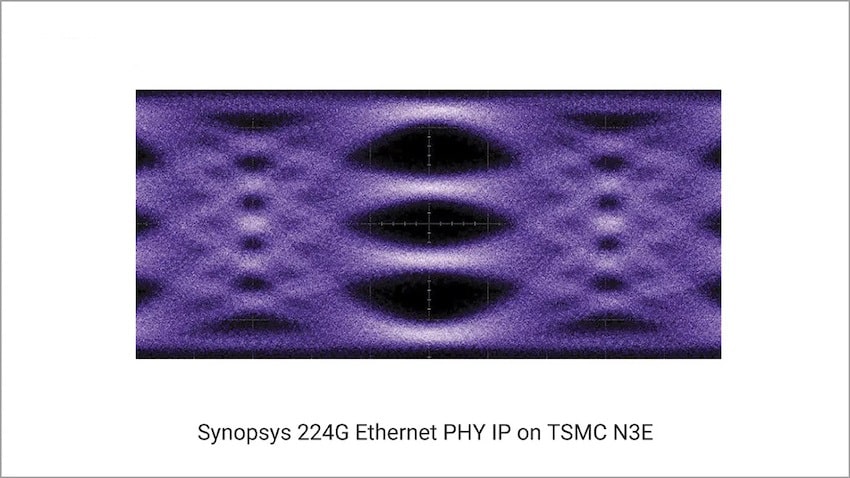

IEEE đã phê chuẩn tiêu chuẩn 802.3 cho Ethernet vào năm 1983, khá là tiêu chuẩn mở rộng, trong khi Synopsys 224G Ethernet PHY IP có thành công silicon đầu tiên trong Tháng Tám 2023. Các kỹ sư mạng nhìn vào sơ đồ mắt để thấy mã hóa PAM-4. Mức độ jitter đã vượt qua cả thông số kỹ thuật tiêu chuẩn IEEE 802.3 và OIF.

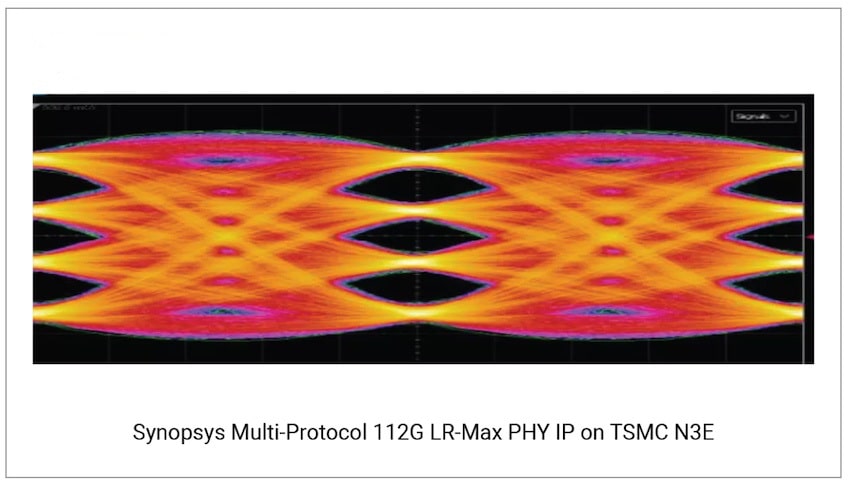

Hỗ trợ các tiêu chuẩn như PCI Express 6.0, 400G/800G Ethernet, CCIX, CXL2.0/3.0, JESD204 và CPRI có Tóm tắt IP PHY 112G đa giao thức. Các kỹ sư có thể kết hợp IP PHY này với MAC và PCS để xây dựng khối Ethernet 200G/400G/800G.

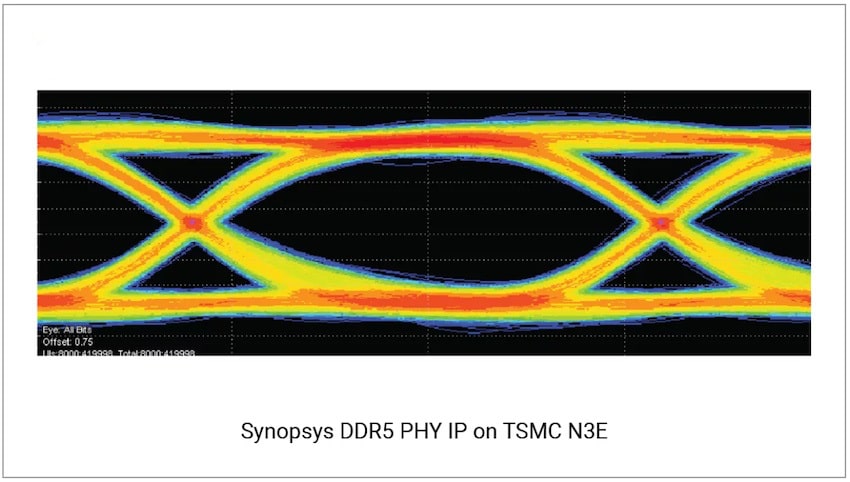

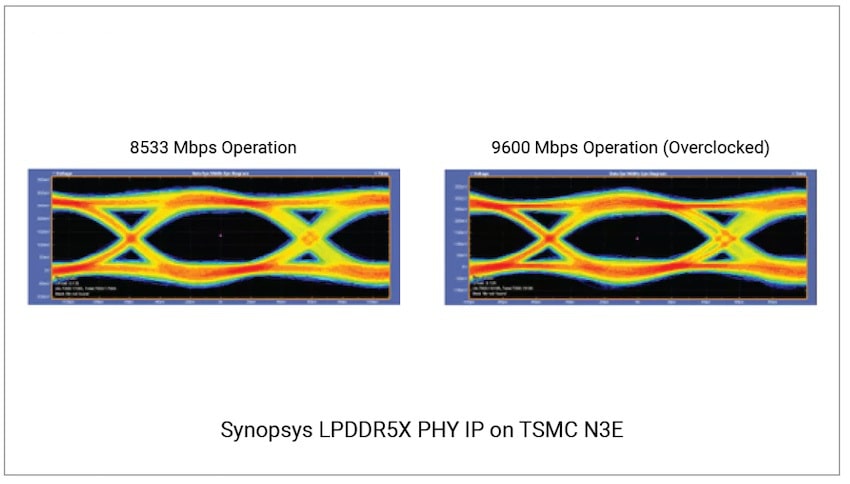

Các mô-đun SDRAM và bộ nhớ có thể sử dụng Tóm tắt DDR5 PHY IP trên TSMC N3E để đạt tốc độ truyền lên tới 8400Mbps. Bạn có thể thấy tầm nhìn rộng mở và lợi nhuận rõ ràng cho IP này hoạt động ở tốc độ nhanh.

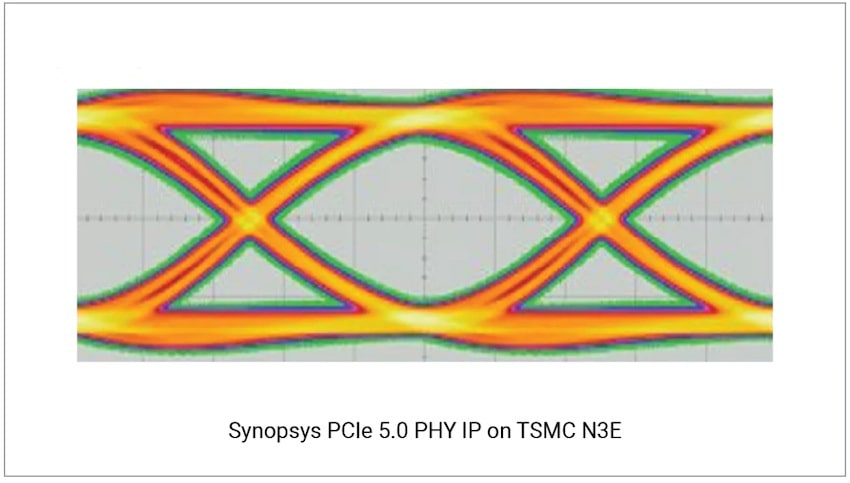

Tiêu chuẩn PCI Express bắt đầu được áp dụng vào năm 2003 và liên tục được cập nhật để đáp ứng nhu cầu ngày càng tăng về điện toán đám mây, lưu trữ và AI. PCIe 5.0 hiện được hỗ trợ bằng IP Synopsys PCIe 5.0 PHY. Silicon đầu tiên trên TSMC N3E cho thấy tốc độ hoạt động của 32 GT / svà nó đã vượt qua bài kiểm tra tuân thủ.

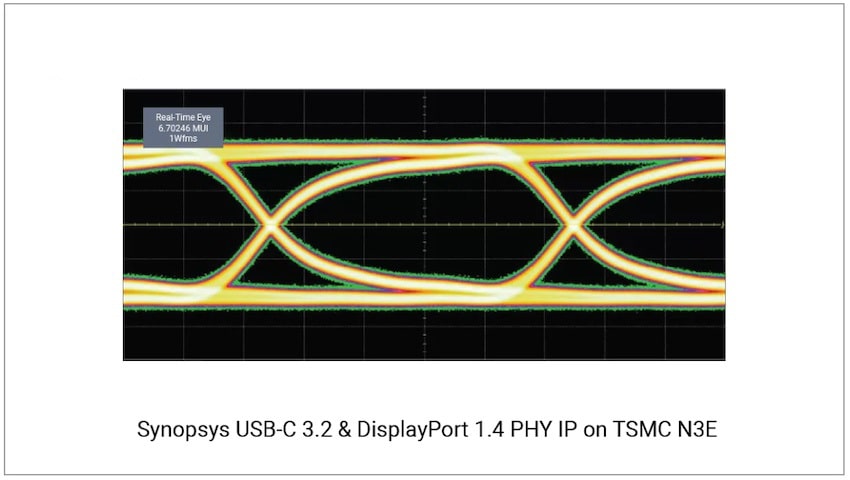

Tôi đã sử dụng USB-C trên MacBook Pro, iPad Pro và điện thoại Android trong nhiều năm nay. Bản tóm tắt hiện hỗ trợ USB-C 3.2 và DisplayPort 1.4 PHY IP trong quy trình TSMC mới nhất. Với IP này, người dùng có thể kết nối tới màn hình Độ phân giải siêu cao 8K.

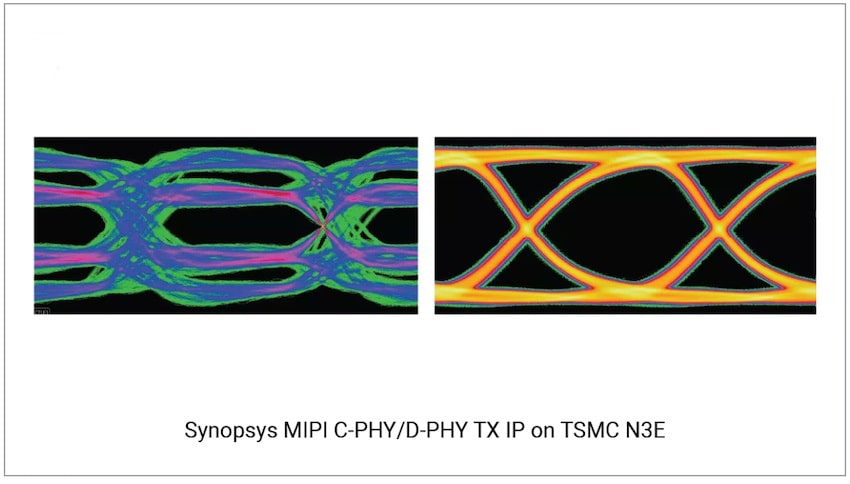

Các công ty điện thoại thông minh đã tiêu chuẩn hóa giao thức MIPI từ nhiều năm trước như một cách hiệu quả để kết nối máy ảnh và Tóm tắt MIPI C-PHY IP/D-PHY IP có thể hoạt động ở tốc độ 6.5Gb/s trên mỗi làn và 6.5Gs/s trên mỗi bộ ba. IP C-PHY hỗ trợ v2.0 và D-PHY IP2.1.

Thông số bộ điều khiển DRAM đồng bộ mới nhất là LPDDR5X, hỗ trợ tốc độ truyền dữ liệu lên tới 8533Mbps, cải thiện 33% so với bộ nhớ LPDDR5. Các Tóm tắt bộ điều khiển LPDDR5X/5/4X đã được chứng minh bằng silicon và sẵn sàng để được thiết kế.

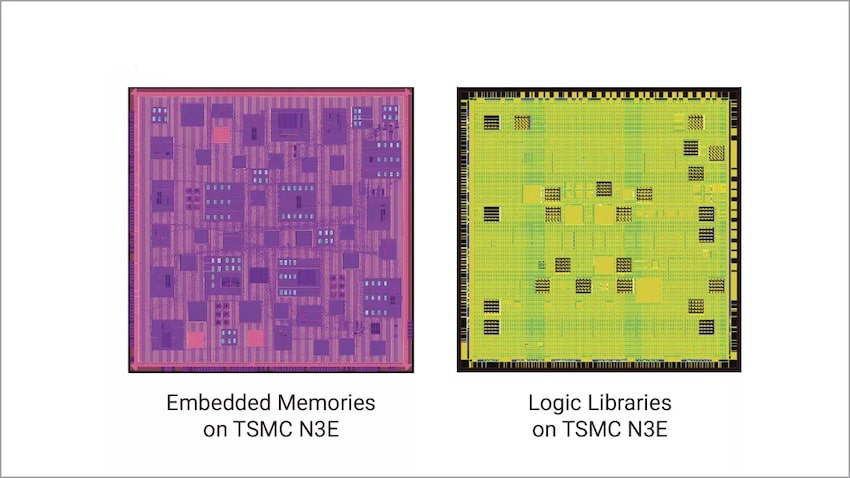

Thư viện logic và ký ức

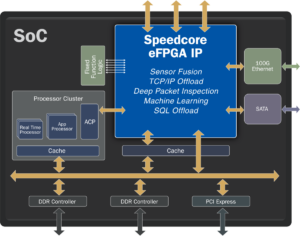

Lên đến một nửa diện tích của SoC có thể là bộ nhớ, vì vậy tin tốt là IP của tổ chức tóm tắt cho phép bạn nhanh chóng thêm các bộ nhớ và ô thư viện logic vào một thiết kế mới. Dưới đây là sơ đồ chip thử nghiệm từ Synopsys trên nút TSMC N3E dành cho bộ nhớ và thư viện logic.

Tổng kết

TSMC và Synopsys đã cộng tác khá tốt với nhau trong nhiều năm và mối quan hệ hợp tác đó hiện mở rộng đến nút N3E nơi các nhà thiết kế SoC có thể tìm thấy IP đã được thử nghiệm bằng silicon cho giao diện, bộ nhớ và logic. Sức mạnh, hiệu suất và năng suất có vẻ hấp dẫn đối với N3E, vì vậy công nghệ này sẵn sàng cho các thiết kế đòi hỏi khắt khe nhất của bạn. Bắt đầu thiết kế với N3E cũng cung cấp cho bạn một con đường nhanh hơn để chuyển sang quy trình N3P.

Thay vì tạo tất cả IP của riêng bạn từ đầu, điều này sẽ kéo dài lịch trình của bạn, đòi hỏi nhiều nguồn lực kỹ thuật hơn và tăng rủi ro, tại sao bạn không xem Synopsys cung cấp những gì trong một loạt các khối IP đã được silicon chứng minh.

Blog liên quan

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiwiki.com/ip/336595-tsmc-n3e-is-ready-for-designs-thanks-to-ip-from-synopsys/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 1

- 2022

- 2023

- 8k

- a

- Đạt được

- đạt được

- thêm vào

- cách đây

- AI

- Tất cả

- cho phép

- Ngoài ra

- an

- và

- Android

- phê duyệt

- LÀ

- KHU VỰC

- AS

- At

- hấp dẫn

- Tháng Tám

- trở lại

- BE

- được

- được

- Chặn

- Khối

- cả hai

- xây dựng

- by

- gọi là

- máy ảnh

- CAN

- cẩn thận

- Tế bào

- thách thức

- Kênh

- đặc trưng

- Chip

- trong sáng

- đám mây

- điện toán đám mây

- hợp tác

- kết hợp

- đến

- Giao tiếp

- Các công ty

- tuân thủ

- máy tính

- Kết nối

- liên tục

- người đóng góp

- điều khiển

- che

- Tạo

- dữ liệu

- Ra mắt

- định nghĩa

- yêu cầu

- nhu cầu

- Thiết kế

- thiết kế

- thiết kế

- thiết kế

- sơ đồ

- màn hình

- được mệnh danh là

- hiệu quả

- hiệu quả

- Kỹ Sư

- Kỹ sư

- nâng cao

- đảm bảo

- Mỗi

- thể hiện

- kéo dài

- mắt

- Tìm kiếm

- Tên

- Trong

- Nền tảng

- Foundry

- từ

- chức năng

- tốt

- Phát triển

- có

- Một nửa

- Có

- tại đây

- Cao

- HTML

- HTTPS

- IEEE

- cải thiện

- in

- Tăng lên

- Giao thức

- giao diện

- trong

- IP

- iPad

- IT

- jpg

- Đường nhỏ

- lớn

- mới nhất

- phát động

- niveaux

- thư viện

- Thư viện

- Lượt thích

- logic

- Xem

- tìm kiếm

- mac

- macbook

- thực hiện

- lợi nhuận

- max-width

- Gặp gỡ

- hội viên

- Memories

- Bộ nhớ

- hoàn tất

- di chuyển

- phút

- Modules

- chi tiết

- hầu hết

- phải

- my

- mạng

- Mới

- tin tức

- nút

- tại

- of

- cung cấp

- cung cấp

- on

- mở

- hoạt động

- hoạt động

- ra

- kết thúc

- riêng

- Công ty

- thông qua

- con đường

- máy tính

- mỗi

- hiệu suất

- điện thoại

- PHP

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Play

- Bài đăng

- quyền lực

- pro

- quá trình

- giao thức

- cung cấp

- nhanh hơn

- Mau

- khá

- phạm vi

- Giá

- sẵn sàng

- yêu cầu

- đòi hỏi

- Thông tin

- Kết quả

- Phục Sinh

- Nguy cơ

- một cách an toàn

- khả năng mở rộng

- lịch trình

- xước

- xem

- DỊCH VỤ

- cho thấy

- hiển thị

- Silicon

- kể từ khi

- So

- thông số kỹ thuật

- tốc độ

- tốc độ

- Tiêu chuẩn

- tiêu chuẩn

- bắt đầu

- Bắt đầu

- là gắn

- thành công

- Hỗ trợ

- Hỗ trợ

- vượt qua

- Hãy

- nhóm

- Công nghệ

- thử nghiệm

- Kiểm tra

- cảm ơn

- việc này

- Sản phẩm

- Khu vực

- cung cấp their dịch

- sau đó

- Đó

- họ

- điều này

- đến

- bên nhau

- chuyển

- ba

- tsmc

- Cực

- cập nhật

- usb

- USB-C

- sử dụng

- đã sử dụng

- Người sử dụng

- sử dụng

- xác nhận

- thông qua

- là

- Đường..

- TỐT

- Điều gì

- cái nào

- trong khi

- tại sao

- rộng

- Phạm vi rộng

- sẽ

- với

- năm

- Năng suất

- bạn

- trên màn hình

- zephyrnet