Trước đây tôi đã viết blog về Xác minh chức năng IC và ASIC, vì vậy hôm nay là lúc để làm tròn điều đó với trạng thái xác minh chức năng của FPGA. Nhóm nghiên cứu Wilson đã biên soạn báo cáo FPGA hai năm một lần kể từ năm 2018, vì vậy, đây là lần thứ ba họ tập trung vào phân khúc thiết kế này. Với giá 5.8 tỷ USD, thị trường FPGA là khá lớn và được dự báo sẽ tăng lên 8.1 tỷ USD vào năm 2025. FPGA bắt đầu hoạt động vào năm 1984 với dung lượng cổng hạn chế và hiện đã phát triển để bao gồm hàng triệu cổng, bộ xử lý và giao thức dữ liệu được tiêu chuẩn hóa.

Các ứng dụng khối lượng thấp được hưởng lợi từ NRE của các thiết bị FPGA và các kỹ sư có thể nhanh chóng tạo mẫu thiết kế của họ bằng cách xác minh và xác nhận ở tốc độ cao. FPGA hiện bao gồm các bộ xử lý, như: Xilinx Zynq UltraSCALE, Intel Stratix, Microchip SmartFusion. Từ 980 người tham gia nghiên cứu xác minh chức năng, phong cách thiết kế FPGA và SoC FPGA có thể lập trình là phổ biến nhất.

Khi kích thước của FPGA tăng lên gần đây, cơ hội phát hành sản phẩm không có lỗi đã giảm xuống chỉ còn 17%, thậm chí còn tệ hơn so với 30% của các dự án IC và ASIC đối với silicon đầu tiên. Rõ ràng, chúng ta cần xác minh chức năng tốt hơn cho các hệ thống FPGA phức tạp.

Các loại lỗi được tìm thấy trong quá trình sản xuất được chia thành một số loại:

- 53% – Logic hoặc Chức năng

- 31% – Phần sụn

- 29% – Đồng hồ

- 28% – Thời gian, đường dẫn quá chậm

- 21% – Thời gian, đường dẫn quá nhanh

- 18% – Giao diện tín hiệu hỗn hợp

- 9% – Tính năng an toàn

- 8% – Tính năng bảo mật

Phóng to loại lỗi lớn nhất, logic hoặc chức năng, có năm nguyên nhân gốc rễ.

Các dự án FGPA hầu hết không hoàn thành đúng thời hạn, một lần nữa là do kích thước lớn hơn của hệ thống, tính phức tạp của logic và thậm chí cả các phương pháp xác minh đang được sử dụng.

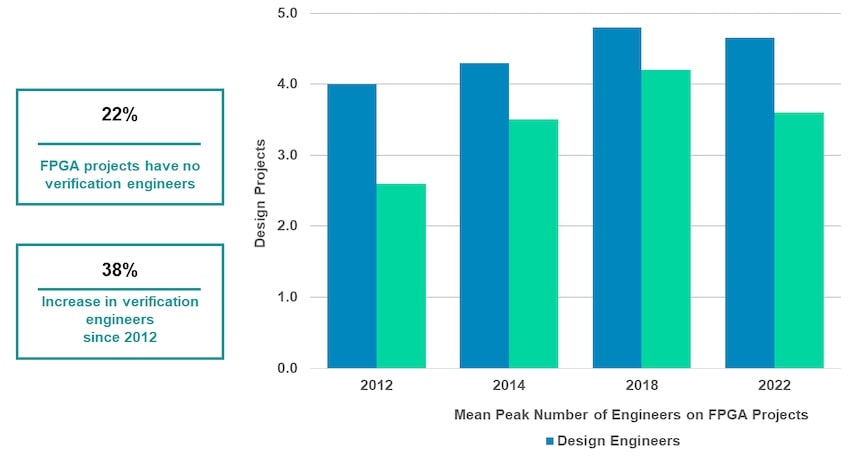

Các kỹ sư trong nhóm FPGA có thể có các chức danh riêng biệt như kỹ sư thiết kế hoặc kỹ sư xác minh, nhưng trên 22% dự án không có kỹ sư xác minh – nghĩa là các kỹ sư thiết kế đã thực hiện nhiệm vụ kép và xác minh IP của chính họ. Trong 10 năm qua, số lượng kỹ sư xác minh trong một dự án FPGA đã tăng 38%, vì vậy đó là tiến trình hướng tới sản xuất không có lỗi.

Các kỹ sư xác minh trên các dự án FPGA dành phần lớn thời gian của họ cho các tác vụ gỡ lỗi ở mức 47%:

- 47% – Gỡ lỗi

- 19% – Tạo thử nghiệm và chạy mô phỏng

- 17% – Phát triển testbench

- 11% – Lập kế hoạch kiểm tra

- 6% – Khác

Số lượng bộ xử lý nhúng đã tăng đều theo thời gian, do đó, 65% thiết kế FPGA hiện có một hoặc nhiều lõi bộ xử lý, làm tăng số lượng xác minh giữa các giao diện phần cứng, phần mềm; và quản lý các mạng trên chip.

Bộ xử lý RISC-V phổ biến chưa từng có được nhúng trong 22% FPGA và bộ tăng tốc AI được sử dụng trong 23% dự án. Có 3-4 số miền đồng hồ trung bình được sử dụng trên FPGA và chúng yêu cầu mô phỏng thời gian ở cấp độ cổng để xác minh, cộng với việc sử dụng các công cụ Kiểm tra tên miền đồng hồ tĩnh (CDC) để xác minh.

Các tính năng bảo mật được thêm vào 49% thiết kế FPGA để giữ dữ liệu nhạy cảm, cộng với 42% dự án FPGA tuân thủ các tiêu chuẩn hoặc nguyên tắc quan trọng về an toàn. Trên SemiWiki, chúng tôi thường viết blog về ISO 26262 và DO-254 tiêu chuẩn. Các nỗ lực thiết kế An toàn Chức năng (FuSa) chiếm từ 25% đến 50% tổng thời gian của dự án.

Ba ngôn ngữ xác minh hàng đầu là VHDL, SystemVerilog và Verilog; nhưng cũng lưu ý những bước nhảy gần đây trong ngôn ngữ Python và C/C++.

Các phương pháp FPGA phổ biến nhất và các thư viện testbench base-case là: Accellera UVM, OSVVM và UVVM. Dựa trên Python cocot thậm chí đã được thêm vào như một danh mục mới cho năm 2022.

Các ngôn ngữ khẳng định được dẫn đầu bởi SystemVerilog Assertions (SVA) với 45%, tiếp theo là Thư viện xác minh mở Accellera (OVL) với 13% và PSL với 11%. Các thiết kế FPGA có thể kết hợp VHDL cho thiết kế RTL cùng với SVA cho các xác nhận.

Kiểm tra thuộc tính chính thức đang phát triển giữa các dự án FPGA, đặc biệt là khi các ứng dụng chính thức tự động hơn đã được giới thiệu bởi các nhà cung cấp EDA.

Các phương pháp xác minh dựa trên mô phỏng trong 10 năm qua cho thấy việc áp dụng ổn định, được liệt kê theo thứ tự mức độ liên quan: Phạm vi mã, phạm vi chức năng, xác nhận, ngẫu nhiên bị ràng buộc.

Tổng kết

Con số thấp 17% không có lỗi đối với các dự án FPGA vào năm 2022 đã được đưa vào sản xuất là con số đáng ngạc nhiên nhất đối với tôi, vì nỗ lực thu hồi hoặc lập trình lại một thiết bị tại hiện trường rất tốn kém và mất thời gian để sửa chữa. Một phương pháp xác minh chức năng mạnh mẽ hơn sẽ dẫn đến ít lỗi thoát ra ngoài sản xuất hơn và việc chia những người tham gia nghiên cứu thành hai nhóm sẽ cho thấy lợi ích.

Đọc toàn bộ Sách trắng 18 trang tại đây.

Blog liên quan

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- Giới thiệu

- máy gia tốc

- thêm

- tham gia

- Nhận con nuôi

- AI

- giữa

- số lượng

- và

- các ứng dụng

- phương pháp tiếp cận

- cách tiếp cận

- ứng dụng

- ASIC

- Tự động

- Trung bình cộng

- được

- hưởng lợi

- Hơn

- giữa

- Tỷ

- Bug

- lỗi

- Sức chứa

- đố

- Phân loại

- Nguyên nhân

- gây ra

- nguyên nhân

- CDC

- cơ hội

- kiểm tra

- Rõ ràng

- Đồng hồ

- mã

- kết hợp

- hoàn thành

- phức tạp

- phức tạp

- bảo hiểm

- Tạo

- quan trọng

- dữ liệu

- Thiết kế

- thiết kế

- thiết bị

- Thiết bị (Devices)

- ĐÃ LÀM

- khác biệt

- miền

- lĩnh vực

- hủy bỏ

- nỗ lực

- những nỗ lực

- nhúng

- ky sư

- Kỹ sư

- đặc biệt

- Ngay cả

- Mỗi

- đắt tiền

- Không

- Rơi

- Tính năng

- lĩnh vực

- Tên

- tập trung

- sau

- chính thức

- tìm thấy

- fpga

- từ

- chức năng

- Gates

- Nhóm

- Các nhóm

- Phát triển

- Phát triển

- mới lớn

- hướng dẫn

- phần cứng

- tổ chức

- HTML

- HTTPS

- in

- bao gồm

- Tăng lên

- tăng

- tăng

- Intel

- giao diện

- giới thiệu

- IP

- IT

- nhảy

- Ngôn ngữ

- lớn hơn

- lớn nhất

- dẫn

- Led

- thư viện

- Thư viện

- Hạn chế

- Liệt kê

- Thấp

- thực hiện

- quản lý

- thị trường

- max-width

- có nghĩa là

- phương pháp

- phương pháp

- hàng triệu

- chi tiết

- hầu hết

- Phổ biến nhất

- Cần

- mạng

- Mới

- con số

- ONE

- mở

- gọi món

- tổng thể

- riêng

- Giấy

- tham gia

- qua

- con đường

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- thêm

- Phổ biến

- Bài đăng

- Bộ xử lý

- bộ vi xử lý

- Sản lượng

- Tiến độ

- dự án

- dự án

- tài sản

- giao thức

- nguyên mẫu

- Python

- Mau

- ngẫu nhiên

- gần đây

- gần đây

- phát hành

- sự liên quan

- báo cáo

- yêu cầu

- nghiên cứu

- nhóm nghiên cứu

- mạnh mẽ

- nguồn gốc

- tròn

- chạy

- Sự An Toàn

- an ninh

- phân khúc

- nhạy cảm

- một số

- nên

- hiển thị

- Chương trình

- Siemens

- Silicon

- kể từ khi

- khá lớn

- Kích thước máy

- So

- Phần mềm

- tốc độ

- tiêu

- tiêu chuẩn

- bắt đầu

- Tiểu bang

- vững chắc

- Học tập

- thật ngạc nhiên

- hệ thống

- Hãy

- nhiệm vụ

- nhóm

- kỹ thuật

- thử nghiệm

- Sản phẩm

- Nhà nước

- cung cấp their dịch

- Thứ ba

- số ba

- thời gian

- thời gian

- trò chơi

- đến

- bây giờ

- quá

- công cụ

- hàng đầu

- đối với

- loại

- sử dụng

- nhà cung cấp

- Xác minh

- xác minh

- xác minh

- thông qua

- khối lượng

- cái nào

- trắng

- giấy trắng

- Wilson

- năm

- zephyrnet