Điện trở suất của đồng phụ thuộc vào cấu trúc tinh thể, thể tích rỗng, ranh giới hạt và sự không tương thích giữa bề mặt vật liệu, điều này trở nên quan trọng hơn ở quy mô nhỏ hơn. Theo truyền thống, việc hình thành dây đồng (Cu) được thực hiện bằng cách khắc mẫu rãnh bằng silicon dioxide có hàm lượng k thấp bằng cách sử dụng quy trình khắc rãnh và sau đó lấp đầy rãnh bằng Cu thông qua dòng chảy damascene. Thật không may, phương pháp này tạo ra các cấu trúc đa tinh thể với ranh giới hạt và khoảng trống đáng kể, làm tăng điện trở của dây Cu. Vật liệu lót TaN có điện trở suất cao cũng được sử dụng trong quy trình này để ngăn chặn sự khuếch tán Cu trong quá trình ủ damascene.

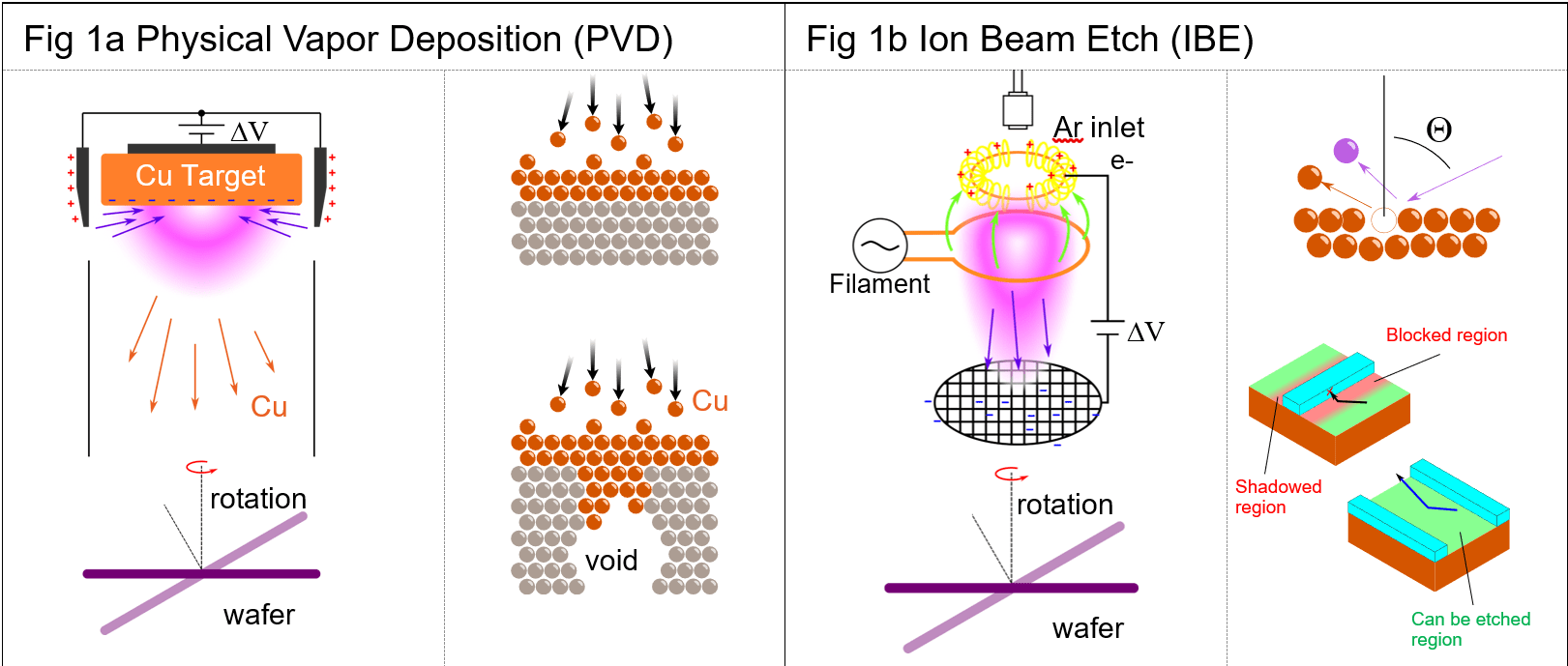

Sự lắng đọng hơi vật lý (PVD) có thể được sử dụng để lắng đọng đồng ở động năng cao (trong khoảng từ 10 đến 100 eV), tạo thành các cấu trúc tinh thể đơn dày đặc, có điện trở thấp. Một nhược điểm của PVD là sự lắng đọng PVD có tầm nhìn trải rộng và chỉ có thể được lắng đọng đồng đều trên các bề mặt phẳng. Nó không thể được sử dụng để lấp các hố sâu hoặc rãnh (hình 1a). Để tạo thành các hình dạng dây cách ly, một lớp Cu đồng nhất phải được lắng đọng trên một bề mặt phẳng và sau đó được khắc vật lý bằng chùm ion. Cu không tạo thành các hợp chất dễ bay hơi với khí phản ứng, do đó không thể sử dụng quá trình ăn mòn ion phản ứng. Các ion Ar được tăng tốc được tạo ra trong quá trình ăn mòn chùm ion (IBE) có thể loại bỏ Cu nếu góc tới rất cao. Thật không may, các vùng có thể khắc sẽ bị hạn chế do hiệu ứng tạo bóng mặt nạ. Hình 1b hiển thị các vùng (màu đỏ) nơi vật liệu không thể bị ăn mòn khi mặt nạ vuông góc với chùm ion tới. Lỗi ăn mòn này xảy ra do bị che khuất hoặc tắc nghẽn đường đi của nguyên tử bị đẩy ra. Khi mặt nạ song song với đường đi của ion, tất cả các vùng không có mặt nạ có thể bị ăn mòn. Do đó, việc khắc tia ion bị giới hạn ở việc khắc các mặt nạ có hình dạng đường có độ dài dài tùy ý.

![]()

Hình 1: (1a) Lắng đọng hơi vật lý (PVD); (1b) Khắc tia ion (IBE).

Các bước xử lý và quy trình chế tạo ảo

Để hiểu được tác động của sự lắng đọng và ăn mòn đối với điện trở đường dây, giờ đây chúng tôi lập mô hình các quy trình ăn mòn PVD và IBE bằng cách sử dụng các chức năng ăn mòn và lắng đọng khả năng hiển thị SEMulator3D. PVD được tái tạo bằng quy trình lắng đọng khả năng hiển thị trải rộng góc 30 độ trong SEMulator3D, quy trình này mô hình chính xác tính chất ngẫu nhiên của các nguyên tử Cu bị đẩy ra trong quá trình bắn phá bằng các ion AR. IBE được tái tạo trong mô hình bằng cách sử dụng một tấm khắc hiển thị với góc trải rộng 2 độ và góc nghiêng 60 độ, để phản ánh hoạt động của các ion được gia tốc lưới với độ phân kỳ chùm tia thấp. Cả hai tấm wafer đều được coi là có chuyển động quay tự do. Các bước quy trình khác đã được điều chỉnh trong quy trình chế tạo ảo để đáp ứng các ràng buộc của IBE và PVD. Hình 2 hiển thị cấu trúc tương tự được tạo bằng cách sử dụng cả quy trình điền damascene Cu (hình 2a) và quy trình PVD/IBE (hình 2b). Các bước quy trình bổ sung đã được đưa vào để kết hợp một số hạn chế nhất định của PVD/IBE và tạo ra hình dạng tương đương cho các cấu trúc cuối mong muốn của chúng tôi.

![]()

Hình 2: (2a) Chế tạo dây Cu bằng Damascene; (2b) Chế tạo dây PVD/IBE Cu.

Sau đó, chúng tôi chứng minh rằng tế bào mạch SRAM 16nm tương đương có thể được chế tạo bằng dây PVD/IBE trong khi vẫn tuân thủ các hạn chế này. Vì tất cả các lớp kim loại phía trên đầu giữa của đường dây đều được chế tạo từ một bề mặt phẳng, điều này khiến nó trở thành một ứng cử viên ý tưởng cho dây PVD/IBE, không giống như cấu trúc liên kết kết nối phức tạp thường thấy trong thiết bị finFET. Hình 3 hiển thị cấu trúc biệt lập của từng lớp kim loại và các bước cần thiết để tạo cấu trúc finFET ba lớp kim loại bằng PVD/IBE.

![]()

Hình 3: (3a) FinFET MEOL 16nm và 3 lớp kim loại; (3b) Chế tạo lớp kim loại từng bước thông qua PVD/IBE.

Kết quả kháng thuốc và kết luận

Sau đó, chúng tôi đo điện trở của dây từ lớp kim loại trên cùng xuống lỗ thông của các kênh FinFET P và N, cho cả dòng damascene và sự lắng đọng hơi vật lý. Hình 4 thể hiện điểm bắt đầu và điểm kết thúc của phép đo điện trở tại kênh P và N (tất cả các vật liệu cách điện khác đều trong suốt). Để bù cho điện trở giao diện giữa lớp lót TaN và dây đồng, điện trở suất của đồng đã được tăng lên bằng cách sử dụng hằng số phân rã hàm mũ 1 nm làm hàm của khoảng cách gần nhất đến giao diện TaN. Do sự lắng đọng Cu trong damascene được cho là không hoàn toàn kết tinh nên điện trở suất của Cu đã tăng 50%. Quá trình đồng PVD/IBE không sử dụng lớp lót TaN, do đó hàm phân rã theo cấp số nhân không được áp dụng và điện trở suất lớn của đồng đã được sử dụng trong mô hình này. Bảng điện trở suất so sánh dòng chảy Damascene với PVD được trình bày trong hình 4.

![]()

Hình 4: Điểm bắt đầu và điểm kết thúc của phép đo điện trở tại kênh P và N.

Các giá trị điện trở được tính toán từ mô hình của chúng tôi cho thấy rằng chúng tôi có thể giảm 67% điện trở bằng phương pháp chế tạo IBE/PVD so với phương pháp khắc rãnh thông thường sau đó là lắng đọng damascene. Điều này xảy ra do không cần lớp lót TaN trong IBE/PVD và có điện trở suất CU thấp hơn trong quá trình này. Kết quả của chúng tôi chỉ ra rằng có thể đạt được sự cải thiện điện trở suất bằng cách sử dụng IBE/PVD so với chất độn damascene trong quá trình hình thành dòng kim loại, với chi phí là quy trình chế tạo phức tạp hơn.

Timothy Yang

(tất cả những bài viết)

Timothy Yang là kỹ sư ứng dụng phần mềm tại Coventor, Công ty nghiên cứu của Lam. Anh làm việc trong lĩnh vực phát triển quy trình, tích hợp và cải thiện năng suất ứng dụng, với chuyên môn về công nghệ bộ nhớ. Trước khi làm việc tại Coventor, Yang đã làm việc tại Tokyo Electron để phát triển các sơ đồ ăn mòn, kỹ thuật cải tiến mẫu in thạch bản, kiểm soát dòng chảy quy trình cho các ứng dụng tạo mẫu SADP và SAQP cũng như công nghệ quang điện tử in thạch bản ngâm và EUV. Yang nhận bằng Cử nhân vật lý của UCLA, bằng Thạc sĩ Khoa học Vật liệu của Viện Công nghệ Chiba và bằng Tiến sĩ. bằng Khoa học Vật liệu của Đại học Tohoku.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- nguồn: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- : có

- :là

- ][P

- 1

- 10

- 100

- a

- ở trên

- tăng tốc

- chứa

- chính xác

- Đạt được

- đạt được

- thêm vào

- Điều chỉnh

- Tất cả

- Tất cả bài viết

- và

- có góc cạnh

- các ứng dụng

- áp dụng

- AR

- LÀ

- AS

- giả sử

- At

- nguyên tử

- BE

- Chùm tia

- trở thành

- được

- giữa

- ranh giới

- by

- tính

- CAN

- ứng cử viên

- không thể

- nhất định

- kênh

- công ty

- so

- so sánh

- phức tạp

- không thay đổi

- khó khăn

- điều khiển

- thông thường

- Copper

- Phí Tổn

- tạo

- tạo ra

- Pha lê

- dữ liệu

- giảm

- sâu

- Bằng cấp

- chứng minh

- phụ thuộc

- nạp tiền

- ký gửi

- mong muốn

- phát triển

- Phát triển

- thiết bị

- Lôi thôi

- màn hình

- khoảng cách

- Divergence

- xuống

- suốt trong

- mỗi

- hiệu lực

- hiệu ứng

- hay

- ky sư

- Tương đương

- EV

- dự kiến

- chuyên môn

- số mũ

- Không

- Hình

- điền

- bằng phẳng

- dòng chảy

- sau

- Trong

- hình thức

- hình thành

- các hình thức

- Miễn phí

- từ

- đầy đủ

- chức năng

- chức năng

- lưới

- Có

- he

- Cao

- cao

- Holes

- HTTPS

- ý tưởng

- ngâm

- cải thiện

- cải tiến

- in

- sự cố

- bao gồm

- Incoming

- kết hợp

- tăng

- Tăng

- chỉ

- Viện

- hội nhập

- Giao thức

- bị cô lập

- IT

- ITS

- jpg

- Lâm

- lớp

- lớp

- hạn chế

- Hạn chế

- Dòng

- dòng

- dài

- Thấp

- LÀM CHO

- mặt nạ

- Mặt nạ

- vật liệu

- nguyên vật liệu

- max-width

- đo

- Bộ nhớ

- kim loại

- phương pháp

- Tên đệm

- kiểu mẫu

- mô hình

- chi tiết

- Thiên nhiên

- cần thiết

- cần thiết

- of

- on

- gọi món

- Nền tảng khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- Song song

- con đường

- Họa tiết

- vật lý

- Thể chất

- Vật lý

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Điểm

- cực

- Bài đăng

- bài viết

- ngăn chặn

- Trước khi

- quá trình

- Quy trình

- ngẫu nhiên

- nhận

- đỏ

- phản ánh

- vùng

- tẩy

- nghiên cứu

- Sức đề kháng

- Kết quả

- s

- tương tự

- quy mô

- đề án

- Khoa học

- bán dẫn

- Hình dạng

- hình

- hình dạng

- Chương trình

- Thị giác

- có ý nghĩa

- Silicon

- kể từ khi

- duy nhất

- nhỏ hơn

- So

- Phần mềm

- lan tràn

- Bắt đầu

- Tiểu bang

- Bước

- Các bước

- cấu trúc

- Sau đó

- Bề mặt

- bàn

- kỹ thuật

- Công nghệ

- Công nghệ

- việc này

- Sản phẩm

- Kia là

- số ba

- thumbnail

- đến

- tokyo

- trên cùng

- theo truyền thống

- minh bạch

- ucla

- hiểu

- trường đại học

- sử dụng

- đã sử dụng

- tận dụng

- Các giá trị

- thông qua

- ảo

- khả năng hiển thị

- Dễ bay hơi

- khối lượng

- vs

- cái nào

- trong khi

- sẽ

- Dây điện

- với

- Công việc

- làm việc

- công trinh

- Năng suất

- zephyrnet