Trong thập kỷ 2010, lợi ích của định luật Moore bắt đầu giảm sút. Định luật Moore cho biết mật độ bóng bán dẫn tăng gấp đôi sau mỗi hai năm, chi phí tính toán sẽ giảm tương ứng 50%. Sự thay đổi trong định luật Moore là do sự phức tạp trong thiết kế tăng lên do sự phát triển của cấu trúc bóng bán dẫn từ các thiết bị phẳng sang Finfets. Finfet cần nhiều khuôn mẫu cho kỹ thuật in thạch bản để đạt được kích thước của thiết bị tới các nút dưới 20nm.

Vào đầu thập kỷ này, nhu cầu điện toán đã bùng nổ, chủ yếu là do sự phát triển của các trung tâm dữ liệu và do lượng dữ liệu được tạo ra và xử lý. Trên thực tế, việc áp dụng Trí tuệ nhân tạo (AI) và các kỹ thuật như Học máy (ML) hiện được sử dụng để xử lý dữ liệu ngày càng tăng và khiến các máy chủ tăng đáng kể khả năng tính toán của chúng.

Các máy chủ đã bổ sung thêm nhiều lõi CPU, tích hợp các GPU lớn hơn được sử dụng riêng cho ML, không còn được sử dụng cho đồ họa và đã nhúng bộ tăng tốc AI ASIC tùy chỉnh hoặc xử lý AI dựa trên FPGA bổ sung. Các thiết kế chip AI ban đầu được triển khai bằng cách sử dụng các SoC nguyên khối lớn hơn, một số trong số chúng đã đạt đến giới hạn kích thước do mặt kẻ ô áp đặt, khoảng 700mm2.

Tại thời điểm này, việc phân chia thành một SoC nhỏ hơn cùng với các chiplet tính toán và IO khác nhau dường như là giải pháp phù hợp. Một số nhà sản xuất chip như Intel, AMD hay Xilinx đã lựa chọn phương án này cho các sản phẩm đi vào sản xuất. Trong sách trắng xuất sắc của The Linley Group, “Chiplets được chấp nhận nhanh chóng: Tại sao chip lớn lại nhỏ”, đã chỉ ra rằng tùy chọn này dẫn đến chi phí tốt hơn so với SoC nguyên khối, do tác động đến năng suất của chip lớn hơn.

Tác động chính của xu hướng này đối với các nhà cung cấp IP chủ yếu là ở các chức năng kết nối được sử dụng để liên kết SoC và chiplets. Tại thời điểm này (quý 3 năm 2021), có một số giao thức đang được sử dụng và ngành đang cố gắng xây dựng các tiêu chuẩn chính thức cho nhiều giao thức trong số đó.

Các tiêu chuẩn D2D hàng đầu hiện nay bao gồm i) Bus giao diện nâng cao (AIB, AIB2) do Intel xác định ban đầu và hiện đã cung cấp mức sử dụng miễn phí bản quyền, ii) Bộ nhớ băng thông cao (HBM) trong đó các khuôn DRAM được xếp chồng lên nhau trên một bộ chuyển đổi silicon và được kết nối bằng TSV, iii) Nhóm con Kiến trúc dành riêng cho miền mở (ODSA), một nhóm ngành, đã xác định hai giao diện khác, Bunch of Wires (BoW) và OpenHBI.

Thiết kế chiplet không đồng nhất cho phép chúng tôi nhắm tới các ứng dụng hoặc phân khúc thị trường khác nhau bằng cách sửa đổi hoặc bổ sung thêm các chiplet có liên quan trong khi vẫn giữ nguyên phần còn lại của hệ thống. Các phát triển mới có thể được tung ra thị trường nhanh hơn với mức đầu tư thấp hơn đáng kể vì việc thiết kế lại sẽ chỉ tác động đến chất nền đóng gói được sử dụng để chứa các chiplets.

Ví dụ: chiplet điện toán có thể được thiết kế lại từ TSMC 5nm thành TSMC 3nm để tích hợp bộ nhớ đệm L1 lớn hơn hoặc các lõi CPU có hiệu suất cao hơn, trong khi vẫn giữ nguyên phần còn lại của hệ thống. Ở đầu đối diện của quang phổ, chỉ có thể thiết kế lại SerDes tích hợp chiplet để có tốc độ nhanh hơn trên các nút quy trình mới cung cấp nhiều băng thông IO hơn để định vị thị trường tốt hơn.

Intel PVC là một ví dụ hoàn hảo về tích hợp không đồng nhất (chiplet chức năng khác nhau, CPU, bộ chuyển mạch, v.v.) mà chúng ta có thể gọi là tích hợp dọc, khi cùng một nhà sản xuất chip sở hữu nhiều thành phần chiplet khác nhau (ngoại trừ các thiết bị bộ nhớ).

Nhà sản xuất chip đang phát triển SoC cho các ứng dụng cao cấp, chẳng hạn như HPC, trung tâm dữ liệu, AI hoặc mạng có thể sẽ là những người sớm áp dụng kiến trúc chiplet. Các chức năng cụ thể, như SRAM cho bộ đệm L3 lớn hơn hoặc bộ tăng tốc AI, các tiêu chuẩn Ethernet, PCIe hoặc CXL sẽ là ứng cử viên giao diện đầu tiên cho thiết kế chiplet.

Khi những người áp dụng sớm này đã chứng minh được tính hợp lệ của các bộ con không đồng nhất tận dụng nhiều mô hình kinh doanh khác nhau và rõ ràng là tính khả thi trong sản xuất đối với thử nghiệm và đóng gói, thì hệ sinh thái sẽ được tạo ra có ý nghĩa quan trọng để hỗ trợ công nghệ mới này. Tại thời điểm này, chúng ta có thể mong đợi việc áp dụng rộng rãi hơn trên thị trường, không chỉ cho các ứng dụng hiệu suất cao.

Chúng ta có thể tưởng tượng rằng các sản phẩm không đồng nhất có thể tiến xa hơn nếu một nhà sản xuất chip tung ra thị trường một hệ thống được tạo thành từ nhiều chiplet khác nhau nhắm tới chức năng tính toán và IO. Cách tiếp cận này khiến việc hội tụ trên giao thức D2D trở thành bắt buộc, vì nhà cung cấp IP cung cấp các chiplet có giao thức D2D nội bộ không hấp dẫn đối với ngành.

Một sự tương tự với điều này là tòa nhà SoC vào những năm 2000, nơi các công ty bán dẫn chuyển sang tích hợp các IP thiết kế khác nhau đến từ các nguồn khác nhau. Các nhà cung cấp IP của những năm 2000 chắc chắn sẽ trở thành nhà cung cấp chiplet của những năm 2020. Đối với một số chức năng nhất định, chẳng hạn như SerDes nâng cao hoặc các giao thức phức tạp, như PCIe, Ethernet hoặc CXL, các nhà cung cấp IP có bí quyết tốt nhất để triển khai chức năng đó trên silicon.

Đối với IP thiết kế phức tạp, ngay cả khi đã chạy xác minh mô phỏng trước khi giao cho khách hàng, nhà cung cấp vẫn phải xác thực IP trên silicon để đảm bảo hiệu suất. Đối với IP kỹ thuật số, chức năng này có thể được triển khai trong FPGA vì nó nhanh hơn và rẻ hơn nhiều so với việc tạo ra một con chip thử nghiệm. Đối với IP tín hiệu hỗn hợp, chẳng hạn như PHY dựa trên SerDes, các nhà cung cấp chọn tùy chọn Chip thử nghiệm (TC) cho phép silicon cho phép họ mô tả IP trong silicon trước khi giao cho khách hàng.

Mặc dù chiplet không chỉ đơn giản là TC vì nó sẽ được kiểm tra và đánh giá rộng rãi trước khi sử dụng trên thực tế, khối lượng công việc gia tăng mà nhà cung cấp phải thực hiện để phát triển chiplet sản xuất sẽ ít hơn nhiều. Nói cách khác, nhà cung cấp IP có vị trí tốt nhất để nhanh chóng phát hành chiplet được xây dựng từ IP của chính mình và cung cấp TTM tốt nhất có thể cũng như giảm thiểu rủi ro.

Mô hình kinh doanh dành cho việc tích hợp không đồng nhất có lợi cho nhiều chiplet khác nhau do nhà cung cấp IP có liên quan tạo ra (ví dụ: ARM cho các chiplet CPU dựa trên ARM, Si-Five cho các chiplet tính toán dựa trên Risc-V và Alphawave cho các chiplet SerDes tốc độ cao) vì họ là chủ sở hữu của IP thiết kế.

Không điều nào trong số này ngăn cản các nhà sản xuất chip thiết kế các chiplet của riêng họ và các IP thiết kế tổ hợp nguồn để bảo vệ kiến trúc độc đáo của họ hoặc triển khai các kết nối nội bộ. Tương tự như SoC Design IP vào những năm 2000, quyết định mua hay đưa ra các chiplets sẽ được cân nhắc giữa việc bảo vệ năng lực cốt lõi và tìm nguồn cung ứng các chức năng không khác biệt.

Chúng tôi đã thấy rằng sự tăng trưởng kinh doanh IP thiết kế trong lịch sử và thời hiện đại kể từ những năm 2000 đã được duy trì nhờ việc liên tục áp dụng nguồn cung ứng bên ngoài. Cả hai mô hình sẽ cùng tồn tại (chiplet được thiết kế nội bộ hoặc bởi nhà cung cấp IP) nhưng lịch sử đã chỉ ra rằng quyết định mua cuối cùng sẽ được thực hiện.

Hiện đã có sự đồng thuận trong ngành rằng sự tập trung điên cuồng vào việc đạt được định luật Moore không còn giá trị đối với các nút công nghệ tiên tiến, ví dụ: 7nm trở xuống. Việc tích hợp chip vẫn đang diễn ra, với số lượng bóng bán dẫn được thêm vào trên mỗi mm vuông ở mỗi nút công nghệ mới. Tuy nhiên, chi phí cho mỗi bóng bán dẫn cũng tăng cao hơn sau mỗi nút mới.

Công nghệ Chiplet là sáng kiến quan trọng nhằm tăng cường tích hợp cho SoC chính trong khi sử dụng các nút cũ hơn cho các chức năng khác. Chiến lược kết hợp này giúp giảm cả chi phí lẫn rủi ro thiết kế liên quan đến việc tích hợp IP thiết kế khác trực tiếp vào SoC chính.

IPnest tin rằng xu hướng này sẽ có hai tác động chính trong hoạt động kinh doanh IP giao diện, một là sự tăng trưởng mạnh mẽ của doanh thu IP D2D trong thời gian tới (2021-2025) và hai là tạo ra thị trường chiplet không đồng nhất để tăng cường silicon cao cấp thị trường IP.

Thị trường này dự kiến sẽ bao gồm các chức năng giao thức phức tạp như PCIe, CXL hoặc Ethernet. Các nhà cung cấp IP cung cấp IP giao diện được tích hợp trong SoC I/O (USB, HDMI, DP, MIPI, v.v.) có thể quyết định cung cấp các chiplet I/O thay thế.

Các danh mục IP khác bị ảnh hưởng bởi cuộc cách mạng này sẽ là nhà cung cấp IP trình biên dịch bộ nhớ SRAM, dành cho bộ nhớ đệm L3. Về bản chất, kích thước bộ đệm dự kiến sẽ thay đổi tùy thuộc vào bộ xử lý. Tuy nhiên, thiết kế chiplet bộ đệm L3 có thể là một cách để nhà cung cấp IP tăng doanh thu IP thiết kế bằng cách cung cấp một loại sản phẩm mới.

Ngoài ra, danh mục IP NVM có thể bị tác động tích cực vì IP NVM không còn được tích hợp trong các SoC được thiết kế trên các nút quy trình nâng cao. Đó sẽ là một cách để các nhà cung cấp IP NVM tạo ra hoạt động kinh doanh mới bằng cách cung cấp các chiplet.

Chúng tôi nghĩ rằng các chiplet tăng tốc FPGA và AI sẽ là nguồn doanh thu mới cho các nhà sản xuất chip ASSP, nhưng chúng tôi không nghĩ rằng họ có thể được xếp hạng chặt chẽ là nhà cung cấp IP.

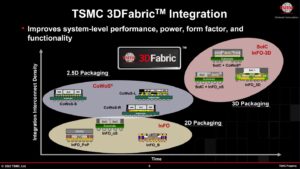

Nếu các nhà cung cấp IP Giao diện sẽ là tác nhân chính trong cuộc cách mạng silicon này thì các xưởng đúc silicon xử lý các nút tiên tiến nhất như TSMC và Samsung cũng sẽ đóng một vai trò quan trọng. Chúng tôi không nghĩ các xưởng đúc sẽ thiết kế chiplet, nhưng họ có thể đưa ra quyết định hỗ trợ các nhà cung cấp IP và thúc đẩy họ thiết kế các chiplet để sử dụng với SoC trong tiến trình 3nm, giống như họ làm ngày nay khi hỗ trợ các nhà cung cấp IP tiên tiến tiếp thị SerDes cao cấp của họ như IP cứng ở 7nm và 5nm.

Sự chuyển đổi gần đây của Intel sang 3rd các xưởng đúc của bên dự kiến cũng sẽ tận dụng IP của bên thứ ba, cũng như việc áp dụng chiplet không đồng nhất của các đối thủ nặng ký về bán dẫn. Trong trường hợp này, chắc chắn rằng các Hyperscalar như Microsoft, Amazon và Google cũng sẽ áp dụng kiến trúc chiplet… nếu họ không đi trước Intel trong việc áp dụng chiplet.

By Eric Esteve (Tiến sĩ.) Nhà phân tích, Chủ sở hữu IPnest

Chia sẻ bài đăng này qua: Nguồn: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- gia tốc

- máy gia tốc

- Nhận con nuôi

- Công nghệ Tiên tiến

- AI

- Cho phép

- đàn bà gan dạ

- AMD

- phân tích

- các ứng dụng

- kiến trúc

- ARM

- trí tuệ nhân tạo

- Trí tuệ nhân tạo (AI)

- ASIC

- BEST

- xây dựng

- Xây dựng

- xăn lên

- xe buýt

- kinh doanh

- mô hình kinh doanh

- mua

- cuộc gọi

- Sức chứa

- thay đổi

- Chip

- Snacks

- đến

- Các công ty

- Tính

- máy tính

- Sự đồng thuận

- Chi phí

- khách hàng

- dữ liệu

- phân phối

- Thiết kế

- phát triển

- Thiết bị (Devices)

- kỹ thuật số

- Đầu

- sớm chấp nhận

- hệ sinh thái

- vv

- sự tiến hóa

- Tên

- Tập trung

- fpga

- Miễn phí

- chức năng

- GPU

- Nhóm

- Phát triển

- Tăng trưởng

- Cao

- lịch sử

- House

- HTTPS

- Hỗn hợp

- Va chạm

- Tăng lên

- ngành công nghiệp

- Sáng kiến

- hội nhập

- Intel

- Sự thông minh

- đầu tư

- IP

- IT

- giữ

- Key

- phóng

- Luật

- hàng đầu

- học tập

- Led

- Tỉ lệ đòn bẩy

- LINK

- học máy

- chính

- nhà sản xuất

- Làm

- sản xuất

- thị trường

- microsoft

- ML

- kiểu mẫu

- mạng lưới

- sản phẩm mới

- các nút

- cung cấp

- cung cấp

- mở

- Tùy chọn

- Nền tảng khác

- chủ sở hữu

- bao bì

- Giấy

- hiệu suất

- Sản phẩm

- Sản lượng

- Sản phẩm

- bảo vệ

- bảo vệ

- Giá

- Thiết kế lại

- REST của

- Nguy cơ

- chạy

- Samsung

- bán dẫn

- Giao Hàng

- mô phỏng

- Kích thước máy

- tiêu chuẩn

- Chiến lược

- hỗ trợ

- Công tắc điện

- hệ thống

- Mục tiêu

- kỹ thuật

- Công nghệ

- thử nghiệm

- hàng đầu

- us

- usb

- nhà cung cấp

- Xác minh

- giấy trắng

- từ

- Công việc

- năm

- Năng suất