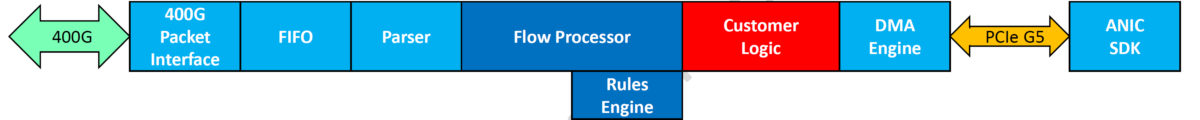

Duy trì truyền tải 400 GbE tốc độ dây chỉ là bước đầu tiên trong việc quản lý lưu lượng doanh nghiệp. Việc thêm tính năng lọc dựa trên quy tắc để sàng lọc các gói trong thời gian thực có thể khiến hầu hết phần cứng mạng bị căng thẳng đến điểm hỏng, làm chậm toàn bộ mạng. Các kiến trúc sư đang cố gắng phân bổ các tải này, phân phối quản lý lưu lượng thông minh khỏi tường lửa cao cấp và các thiết bị khác tới các điểm cuối nơi lưu lượng truy cập bắt nguồn – nhưng phần cứng 400 GbE với công cụ quy tắc tích hợp không dễ dàng giảm quy mô. Achronix có giải pháp xây dựng trên FPGA Speedster7t tích hợp giao diện gói 400 GbE, PCIe Gen 5, bộ xử lý luồng với công cụ quy tắc và còn chỗ cho logic của khách hàng để phân biệt các thiết kế SmartNIC 400 GbE.

Tất cả các thành phần cần thiết cho SmartNIC 400 GbE trong một FPGA

Các bộ thu phát có khả năng 400 GbE đang xuất hiện trên nhiều FPGA cao cấp. Nhưng vấn đề tạo ra “hệ thống ống nước” phù hợp trong một FPGA với tốc độ 400 GbE thường được coi là một bài tập cho người đọc. Hai dự án trong Achronix, với sự trợ giúp từ việc mua lại Accolade IP và kiến thức chuyên môn vào tháng 2022 năm XNUMX, đã suy nghĩ kỹ lưỡng về toàn bộ chuỗi IP và đang cùng nhau đưa ra một giải pháp hoàn chỉnh dưới biểu ngữ Mã cơ sở hạ tầng mạng Achronix (ANIC).

Scott Schweitzer, CISSP, Giám đốc Kế hoạch Sản phẩm SmartNIC tại Achronix cho biết: “Chúng tôi không nghĩ có ai có 400 GbE với loại công cụ quy tắc và xử lý luồng này cho điểm cuối ngay bây giờ”. Nó bắt đầu với công nghệ hỗ trợ – ANIC Shell, đường dẫn luồng gói Ethernet trong RTL. Dự án này bắt nguồn từ công nghệ 100 GbE và PCIe Gen 3, tập trung vào các phần tử FIFO, phân tích cú pháp và DMA cần thiết để giữ cho các gói chuyển động trơn tru. Trong Speedster 7t, hơn một nửa logic vẫn có sẵn cho khách hàng.

![]()

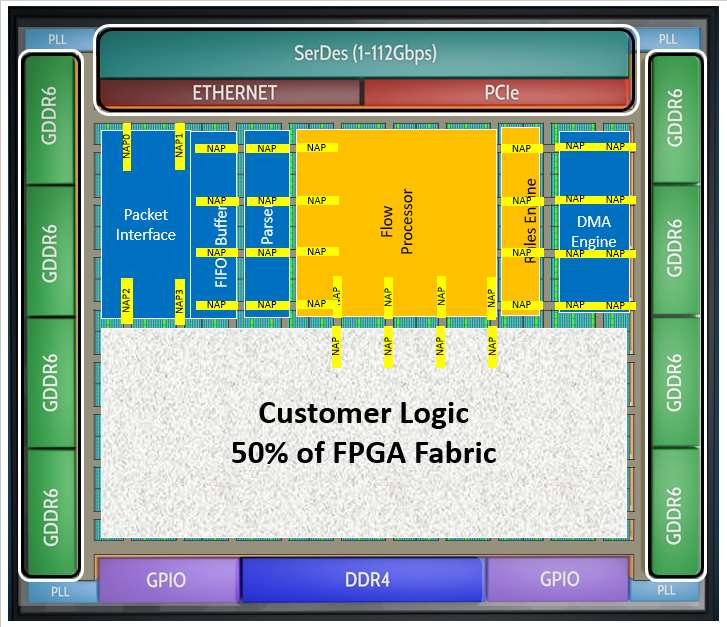

Tiếp theo là việc chuyển từ lớp vỏ sang ANIC hoàn chỉnh cho SmartNIC 400 GbE với bộ xử lý luồng và công cụ quy tắc, vẫn còn khoảng 50% logic Speedster7t.

Việc tăng ANIC lên tới 400 GbE có thể trông dễ dàng từ sơ đồ này, nhưng Schweitzer chỉ ra hai điểm trong chuỗi cần được chú ý cụ thể. Schweitzer cho biết: “Để truy cập máy chủ ở tốc độ 400 Gb, chúng tôi cần từng chút hiệu suất PCIe mà chúng tôi có thể có được – 16 làn PCIe 5 giúp duy trì hoạt động của động cơ DMA”. “Chúng tôi cũng cần bộ nhớ nhanh hơn cho DMA và FIFO và bốn kênh GDDR6 ở mỗi bên đã giúp chúng tôi đạt được điều đó.

Được hiển thị trong dấu chân Speedster7t, ANIC trông như thế này. Lưu ý đây là tất cả các khối IP được tối ưu hóa với thời gian đóng được xác minh ở tốc độ nhanh.

Mở ra những khả năng mới cho quản lý giao thông thông minh

ANIC tạo nền tảng cho sự phát triển SmartNIC, cho phép khách hàng xác định khả năng định hình gói và quản lý lưu lượng trong phần cứng quy mô điểm cuối chạy ở tốc độ 400 GbE SmartNIC. Khách hàng có được thời gian tiếp thị nhanh hơn và kiểm soát việc tùy chỉnh IP ANIC cũng như logic giá trị gia tăng của họ. Có thể thực hiện sao chép hoặc loại bỏ các gói trùng lặp, chạy các kho lưu trữ khóa-giá trị cục bộ và các hoạt động khác trên luồng gói bằng cách sử dụng SmartNIC.

An ninh mạng được cải thiện nhờ tính năng quản lý lưu lượng thông minh cho cả nhận và truyền, nhưng SmartNIC theo truyền thống chỉ áp dụng các chính sách khi nhận. ANIC cho phép áp dụng các chính sách cho cả dữ liệu được nhận và truyền. “Giả sử một đêm nọ, có một máy chủ ứng dụng đột nhiên tạo ra lưu lượng truy cập bất thường vào lúc 2 giờ sáng khi lẽ ra không có ai làm việc,” Schweitzer bắt đầu một giai thoại. “Trong kiến trúc mạng doanh nghiệp thông thường, lưu lượng truy cập tăng lên sẽ đến được một thiết bị như tường lửa hiệu suất cao và nó sẽ phải có các quy tắc thích hợp để dừng các gói tin. Bằng cách chuyển các quy tắc tương tự đó sang SmartNIC 400 GbE có IP ANIC được cài đặt trong máy chủ ứng dụng, lưu lượng truy cập đáng ngờ sẽ không bao giờ rời khỏi nó, ngăn chặn sự lan truyền và giảm tải trên mạng.”

Trí tuệ nhân tạo (AI) cũng có tầm ảnh hưởng lớn trên quy mô khả năng của ANIC. Bộ xử lý máy học (MLP) trong Speedster7t có thể tìm hiểu và triển khai các quy tắc ANIC bằng cách quan sát các mẫu lưu lượng truy cập SmartNIC trước khi các nhóm bảo mật mạng nhận thấy lỗ hổng. Học tập gốc điểm cuối cũng có thể thúc đẩy bộ cân bằng tải ảo, phân tán, thông minh, giảm tải lưu lượng truy cập sang các nền tảng khác nếu các mẫu lưu lượng tập trung xuất hiện.

Achronix đang nỗ lực hết sức để đảm bảo FPGA Speedster7t hiệu suất cao sẵn sàng cho các ứng dụng nâng cao trong thế giới thực. SmartNIC 400 GbE chỉ là một trường hợp sử dụng khả thi cho Speedster7t – và đây là một trường hợp tốt vì rất ít phương pháp khác có thể đạt được kết quả tương tự. Chúng tôi mong đợi sự đổi mới của khách hàng sẽ tiếp tục với một loạt giải pháp khác biệt được xây dựng trên IP ANIC 400 GbE.

Tìm hiểu thêm trong thông cáo báo chí của Achronix:

Achronix vượt qua ranh giới của mạng với 400 GbE và PCIe Gen 5.0 cho SmartNIC

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Ô tô / Xe điện, Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- BlockOffsets. Hiện đại hóa quyền sở hữu bù đắp môi trường. Truy cập Tại đây.

- nguồn: https://semiwiki.com/efpga/achronix/331586-400-gbe-smartnic-ip-sets-up-fpga-based-traffic-management/

- : có

- :là

- :Ở đâu

- $ LÊN

- 100

- 16

- 2022

- 32

- a

- Đạt được

- mua lại

- thêm

- tiên tiến

- AI

- Tất cả

- Cho phép

- Ngoài ra

- am

- an

- và

- bất kỳ ai

- thiết bị

- Các Ứng Dụng

- các ứng dụng

- áp dụng

- cách tiếp cận

- kiến trúc

- LÀ

- xung quanh

- AS

- At

- sự chú ý

- có sẵn

- xa

- trở lại

- cân bằng

- cờ

- BE

- trước

- Một chút

- Chặn

- Khối

- cả hai

- ranh giới

- Phá vỡ

- Xây dựng

- xây dựng

- nhưng

- by

- đến

- CAN

- khả năng

- có khả năng

- trường hợp

- chuỗi

- kênh

- đóng cửa

- mã

- đến

- hoàn thành

- Tập trung

- điều khiển

- thông thường

- có thể

- Tạo

- khách hàng

- khách hàng

- tùy biến

- dữ liệu

- Ngày

- triển khai

- thiết kế

- Phát triển

- phân biệt

- phân biệt

- Giám đốc

- phân phối

- phân phối

- đma

- dont

- xuống

- lái xe

- mỗi

- dễ dàng

- dễ dàng

- nỗ lực

- các yếu tố

- xuất hiện

- cho phép

- cho phép

- Điểm cuối

- thiết bị đầu cuối

- Động cơ

- đảm bảo

- Doanh nghiệp

- Toàn bộ

- Mỗi

- Tập thể dục

- mong đợi

- chuyên môn

- nhanh hơn

- Fed

- vài

- lọc

- tường lửa

- tường lửa

- Tên

- dòng chảy

- Dấu chân

- Trong

- các hình thức

- Nền tảng

- 4

- fpga

- từ

- Thu được

- Gen

- tạo ra

- được

- tốt

- Một nửa

- phần cứng

- Có

- giúp đỡ

- Cao cấp

- hiệu suất cao

- chủ nhà

- HTTPS

- if

- cải thiện

- in

- tăng

- Cơ sở hạ tầng

- sự đổi mới

- tích hợp

- Tích hợp

- Sự thông minh

- Thông minh

- Giao thức

- trong

- IP

- IT

- ITS

- jpg

- chỉ

- chỉ một

- Giữ

- lớn

- LEARN

- học tập

- trái

- Lượt thích

- tải

- tải

- địa phương

- logic

- Xem

- NHÌN

- máy

- học máy

- quản lý

- quản lý

- max-width

- Bộ nhớ

- Might

- chi tiết

- hầu hết

- di chuyển

- cần thiết

- cần

- mạng

- An ninh mạng

- mạng lưới

- không bao giờ

- Mới

- đêm

- Để ý..

- tại

- of

- thường

- on

- ONE

- có thể

- Hoạt động

- tối ưu hóa

- or

- Nền tảng khác

- ra

- kết thúc

- gói

- mô hình

- hiệu suất

- miếng

- đường ống dẫn

- lập kế hoạch

- Nền tảng

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Điểm

- điểm

- Chính sách

- khả năng

- có thể

- Bài đăng

- nhấn

- Thông cáo báo chí

- ngăn chặn

- Vấn đề

- xử lý

- Bộ xử lý

- bộ vi xử lý

- Sản phẩm

- dự án

- dự án

- tuyên truyền

- đúng

- đẩy

- Đặt

- phạm vi

- đạt

- Người đọc

- sẵn sàng

- thực

- thế giới thực

- thời gian thực

- nhận

- nhận

- giảm

- phát hành

- vẫn còn

- Kết quả

- ngay

- Phòng

- quy tắc

- chạy

- tương tự

- nói

- nói

- Quy mô

- scott

- an ninh

- Tháng Chín

- bộ

- định hình

- Shell

- nên

- bên

- Sàng lọc

- kể từ khi

- Chậm

- thông suốt

- rắn

- giải pháp

- Giải pháp

- riêng

- tốc độ

- tốc độ

- lan tràn

- bắt đầu

- Bước

- Vẫn còn

- Dừng

- cửa hàng

- dòng

- căng thẳng

- phù hợp

- đáng ngờ

- Hãy

- đội

- Công nghệ

- hơn

- Sản phẩm

- cung cấp their dịch

- Đó

- Kia là

- nghĩ

- điều này

- những

- nghĩ

- Thông qua

- thời gian

- thời gian

- đến

- bên nhau

- đối với

- theo truyền thống

- giao thông

- chuyển

- truyền

- hai

- kiểu

- Dưới

- bất thường

- us

- sử dụng

- ca sử dụng

- sử dụng

- giá trị gia tăng

- xác minh

- thông qua

- ảo

- khối lượng

- dễ bị tổn thương

- we

- khi nào

- với

- ở trong

- đang làm việc

- sẽ

- zephyrnet