Việc tích hợp nhiều khuôn không đồng nhất trong một gói là mấu chốt để mở rộng Định luật Moore và nâng cao hiệu suất, hiệu suất sử dụng điện và chức năng, nhưng nó cũng đặt ra những vấn đề quan trọng về cách quản lý tải nhiệt.

bao bì tiên tiến cung cấp một cách để tích hợp nhiều tính năng và chức năng hơn vào một thiết bị, ngày càng bằng cách xếp chồng các thành phần khác nhau theo chiều dọc thay vì chỉ thu nhỏ mạch kỹ thuật số để nhồi nhét nhiều chức năng hơn vào một SoC có kích thước hình kẻ ô. Điều đó đặt ra vấn đề về cách tối ưu hóa hiệu suất và sức mạnh. Trên một khuôn đơn, đường dẫn tín hiệu có thể ngắn đến mức cần thiết và chất nền có tác dụng tản nhiệt hiệu quả. Nhưng với nhiều khuôn trong một gói, chất nền và chất điện môi cần phải mỏng hơn để giảm khoảng cách mà tín hiệu cần truyền đi và điều đó hạn chế sự tản nhiệt.

Điều này có thể dẫn đến các điểm nóng khó dự đoán, đặc biệt trong các khối lượng công việc và trường hợp sử dụng khác nhau. Và nó có thể trở nên tồi tệ hơn khi tích hợp nhiều chip hoặc chiplet với các đặc tính nhiệt khác nhau vào một gói duy nhất.

Vik Chaudhry, giám đốc cấp cao, tiếp thị sản phẩm và phát triển kinh doanh tại Công nghệ Amkor. “Chúng tôi thấy các nhà cung cấp không chỉ đặt 3 hoặc 4 mà 8 hoặc 10 hoặc 12 con chết. Làm thế nào để bạn phân phối lượng nhiệt đó ra xung quanh?

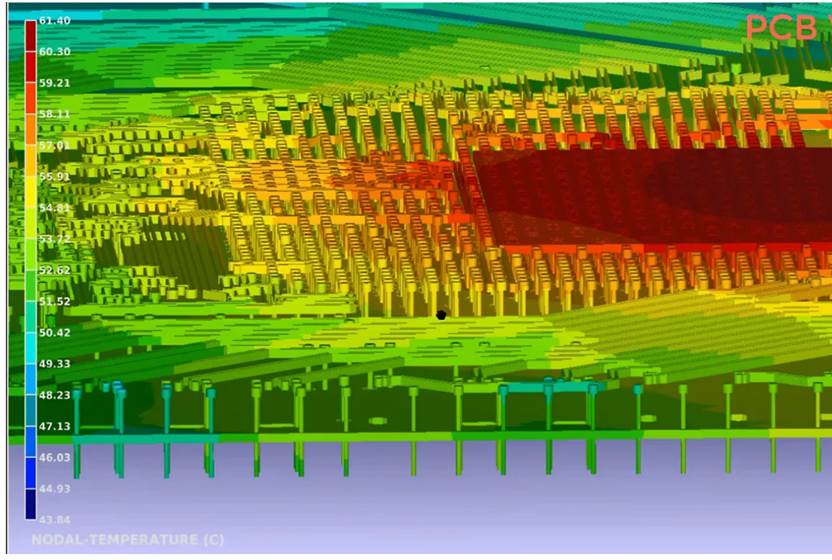

Hình 1: Mô phỏng tản nhiệt ở cặp nhiệt. Nguồn: Ansys

Tích hợp không đồng nhất phụ thuộc vào khả năng loại bỏ nhiệt một cách hiệu quả, đảm bảo rằng các khuôn đúc dày đặc trong mô-đun duy trì nhiệt độ chấp nhận được để vận hành đáng tin cậy. Lộ trình tích hợp không đồng nhất của IEEE xác định một số lĩnh vực cần phát triển, bao gồm các kỹ thuật lập mô hình tiên tiến để dự đoán và quản lý dòng nhiệt, vật liệu mới có cả tính dẫn nhiệt cao và tính dẫn điện thấp, cũng như các giải pháp làm mát mới có thể được tích hợp liền mạch vào các gói phức tạp.

Sự không phù hợp về nhiệt

Lựa chọn vật liệu rất quan trọng đối với việc quản lý nhiệt trong tích hợp không đồng nhất. Khi các thành phần có hệ số giãn nở nhiệt (CTE) khác nhau nóng lên và nguội đi, các vật liệu này sẽ giãn nở và co lại với tốc độ khác nhau. Điều đó có thể gây ra các ứng suất cơ học làm ảnh hưởng đến tính toàn vẹn của chip, làm suy yếu các liên kết kết nối chúng với bộ chuyển đổi hoặc các chất nền khác và ảnh hưởng đến chức năng tổng thể của thiết bị.

Việc sử dụng các vật liệu có CTE tương tự giúp giảm các ứng suất này, giảm thiểu một số nguy cơ hỏng hóc sớm cũng như các hiệu ứng cảm ứng nhiệt khác, chẳng hạn như lão hóa nhanh, giảm độ linh động của điện tử hoặc trôi trong tín hiệu tương tự hoặc quang học.

David Fromm, COO và phó chủ tịch kỹ thuật tại cho biết: “CTE có lẽ là thách thức số một đối với bao bì tiên tiến và tôi không nghĩ có ai thực sự hiểu được nó một cách đầy đủ”. Công nghiệp Promex. “Chúng tôi đang xử lý CTE trên quy mô ba chiều theo những cách mà chúng tôi chưa từng thấy trước đây và những vấn đề về cong vênh hoặc gãy các bộ phận này thực sự là một thách thức. Một số công ty có thể tìm ra quy trình nhất định và sau đó vật liệu thay đổi, kích thước thiết bị thay đổi và phương trình cũng thay đổi. Và sau đó bạn phải tìm hiểu lại.”

Nói một cách đơn giản, việc tích hợp không đồng nhất đòi hỏi sự hiểu biết cơ bản về đặc tính giãn nở nhiệt của mọi vật liệu mà cuối cùng có thể định hình độ tin cậy và năng suất của thiết bị đóng gói. Và đó chỉ là một phần của vấn đề. Việc đóng gói nâng cao đòi hỏi sự hiểu biết về những gì khác ở xung quanh chip hoặc chiplet, cách các phần tử khác đó đang được sử dụng và tất cả những phần tử đó cần được lập mô hình và mô phỏng cùng nhau bằng cách sử dụng khối lượng công việc thực tế được mong đợi. Vấn đề này trở nên khó khăn hơn nhiều khi nhu cầu điện toán thay đổi, chẳng hạn như trong các trung tâm dữ liệu nơi AI tổng hợp đã tăng đáng kể lượng dữ liệu cần xử lý, dẫn đến việc sử dụng bộ xử lý và bộ nhớ cao hơn.

Marc Swinnen, giám đốc tiếp thị sản phẩm tại cho biết: “Luôn luôn có một số mức độ phân tích nhiệt, nhưng nó được thực hiện cuối cùng chỉ để kiểm tra xem không có gì vượt quá tầm kiểm soát”. Ansys. “Bạn có thể nhắm mục tiêu đến một nhiệt độ tiếp giáp nhất định và nếu nó tuân thủ thì mọi việc thật đơn giản. Nhưng giờ đây với hệ thống nhiều khuôn, bạn sẽ phải làm điều đó ở giai đoạn quy hoạch sàn RTL. Bạn sẽ phải biết công suất đầu ra của mỗi con chip này là bao nhiêu để hai con chip nóng lên ở cùng một chế độ hoạt động không được đặt ngay cạnh nhau hoặc ngay trên nhau . Điều đó sẽ làm hỏng thiết kế của bạn.”

trở lại với bản vẽ

Khi ngành phải vật lộn với nhiều thách thức khác nhau đối với lộ trình tích hợp không đồng nhất, quản lý nhiệt không còn là vấn đề cần cân nhắc nữa. Nó đã chuyển sang trái trong quy trình từ thiết kế đến sản xuất và chuyển sang lĩnh vực nơi các bộ giám sát trong mạch có thể đánh giá và điều chỉnh mọi thứ, từ phân vùng đến ưu tiên các chip và chiplet khác nhau.

“Ma quỷ nằm ở chi tiết,” Fromm nói. “Những quyết định tích hợp và thiết kế dường như nhỏ này có thể có tác động to lớn đến việc liệu bạn có thể xây dựng những gì mình muốn hay không, chứ chưa nói đến việc xây dựng nó với năng suất và độ tin cậy của sản phẩm ở phía sau. Việc lựa chọn vật liệu phù hợp, suy nghĩ về việc xếp chồng lên nhau và suy nghĩ về quy trình đều rất quan trọng.”

Điều này thể hiện sự thay đổi cơ bản trong số lượng thiết kế ngày càng tăng, từ trung tâm dữ liệu đến thiết bị điện tử tiêu dùng và các phương tiện tự hành ngày càng tăng. Vì các phần tử không đồng nhất được đóng gói cùng nhau trong người hâm mộ với các trụ cột, 2.5D, và đặc biệt là trong 3D-IC thiết kế, đường dẫn nhiệt cần được vạch ra ngày càng chi tiết. Nếu thực hiện sai, điều này có thể gây hư hỏng cho toàn bộ gói chứa nhiều chip/chiplet, thậm chí việc tìm ra nguồn gốc của sự cố cũng có thể tốn kém.

George Orji, nhà khoa học nghiên cứu của Chương trình Sản xuất Bao bì Tiên tiến Quốc gia CHIPS (NAPMP) cho biết: “Cần phải thiết kế để đáp ứng các hạn chế về cơ nhiệt cũng như công nghệ lắp ráp và chất nền”. “Bao bì tiên tiến không cho phép làm lại, vì vậy các phương pháp thiết kế chip nguyên khối cho bao bì tiên tiến là điều chúng tôi cần phải làm.”

Sự phức tạp vốn có trong các hệ thống tích hợp không đồng nhất đòi hỏi một cách tiếp cận đa ngành để thiết kế. Đây là một vấn đề phức tạp và những nỗ lực nhằm thực hiện phương pháp này không phải là mới và nó đã thất bại khi đối mặt với việc mở rộng quy mô phẳng. David Fried, phó chủ tịch tập đoàn tại Nghiên cứu Lam, cho biết trong một cuộc thảo luận gần đây rằng IBM đã thử tích hợp không đồng nhất 3D cách đây 25 năm khi ông còn ở đó. Ông nói: “Chúng tôi nghĩ rằng chúng tôi có thể ghép nhiều thành phần quy trình lại với nhau trong đó. “Tuy nhiên, một số thách thức lớn nhất nằm ở phía thiết kế và EDA, phân chia công nghệ sẽ sử dụng, cách phân chia các thành phần khác nhau của hệ thống trên các chip khác nhau, sau đó quay lại và tích hợp lại chúng. Thiết kế và sự tối ưu hóa của thiết kế phải có thì mới có thể hoạt động được.”

Điều thay đổi kể từ đó là ngành công nghiệp chip đã hết lựa chọn. Việc phát triển chip tại các nút tiên tiến nhất đang trở nên quá tốn kém và quá bị hạn chế bởi kích thước của ô kẻ ô. Nhưng đây vẫn là công việc khó khăn.

Để giảm bớt gánh nặng cho các nhà thiết kế, các kỹ thuật tổng hợp liên quan đến khoa học vật liệu tiên tiến và các công cụ thiết kế có sự hỗ trợ của máy tính ngày càng trở nên quan trọng, đặc biệt khi cấu hình chip trở nên phức tạp hơn và chức năng tích hợp ngày càng tăng. Swinnen của Ansys cho biết thêm: “Đây là nơi chúng tôi vẫn còn việc phải làm”. “Làm cách nào để chúng ta giải quyết vấn đề này theo cách không yêu cầu mọi nhà thiết kế phải là chuyên gia về nhiệt, chuyên gia về nhiễu điện từ và chuyên gia về cơ khí? Thật không thực tế khi mong đợi điều đó từ cộng đồng thiết kế của chúng tôi.”

Với những hạn chế này xuất hiện sự cần thiết phải đổi mới trong một số khía cạnh chính của quá trình thiết kế. Nhận thức được bản chất nhiều mặt của việc sinh nhiệt trong các chip tích hợp dày đặc, cần phải giải quyết không chỉ các sự kiện nhiệt ở trạng thái ổn định mà còn cả các sự kiện nhiệt nhất thời, phần lớn dựa trên các trường hợp sử dụng hoặc khối lượng công việc. Lộ trình tích hợp không đồng nhất bao gồm các chiến lược như vật liệu giao diện nhiệt 3D và bộ tản nhiệt phù hợp với CTE để đảm bảo phân phối nhiệt đều.

Manuel Mota, giám đốc tiếp thị sản phẩm cấp cao tại cho biết: “Với nhiều khuôn dập, bạn có nhiều nguồn hiệu ứng nhiệt, nhiều gradient cơ học và gradient nhiệt độ”. Synopsys. “Tất cả những điều này phải được giải quyết trong giai đoạn thiết kế.”

Việc tích hợp các cân nhắc về nhiệt vào quá trình thiết kế là một yêu cầu để hiện thực hóa bất kỳ thiết bị bán dẫn phức tạp nào. Nó không chỉ là việc xác định các vật liệu hoặc thành phần phù hợp. Nó cũng hình dung ra cách tất cả họ sẽ hoạt động chung trong lĩnh vực này.

Khi các kỹ sư giảm kích thước của các thiết bị điện tử trong khi tăng hiệu suất của chúng, lớp vỏ nhiệt sẽ thắt chặt đáng kể. Việc quản lý toàn diện các cấu hình nhiệt ở các trạng thái hoạt động khác nhau, tận dụng vật liệu tản nhiệt và giao diện nhiệt mới nhất, trở nên cần thiết để duy trì tính toàn vẹn và hiệu suất của thiết bị trong suốt vòng đời dự định của nó.

Swinnen nói: “Nhiệt là hạn chế số một đối với mật độ tích hợp. “Thật dễ dàng để xếp chồng các con chip. Bạn có thể sản xuất nó và bạn có thể thiết kế nó, nhưng nó sẽ không bao giờ hoạt động được vì nó sẽ quá nóng. Vì vậy, nhiệt đã trở thành một phần trọng tâm trong mối quan tâm của mọi nhà thiết kế chip 3D-IC.”

Giải quyết thách thức về nhiệt trong tích hợp không đồng nhất đòi hỏi phải kết hợp các vật liệu khác nhau, chẳng hạn như chất bán dẫn có CTE thấp hơn, như silicon, với các kim loại như đồng hoặc nhôm, để tản nhiệt hiệu quả. Thật không may, sự kết hợp các vật liệu này thường dẫn đến cong vênh, nứt, nâng mối hàn và thiết bị hỏng sớm hơn dự kiến. Cần có những vật liệu mới có đặc tính tương thích để khắc phục những vấn đề này.

Fromm cho biết: “Những vật liệu nền này có thể sẽ phát triển chậm hơn so với các vật liệu tiếp giáp, chất kết dính, epoxies, v.v.”. “Nó liên quan đến việc xử lý các điều kiện và cách bạn quản lý những điều kiện đó. Nơi mà chúng tôi có thể làm tốt hơn ở khía cạnh xử lý là làm việc với các nhà sản xuất chất kết dính để hiểu những thay đổi về nhiệt độ, sau đó ở cấp độ thiết kế để hiểu cách tất cả các ngăn xếp này có thể phát triển, xem xét những thay đổi về nhiệt độ đó.”

Đổi mới vật chất

Mối lo ngại về nhiệt không chỉ dừng lại ở hoạt động của con chip. Nhiệt độ cũng là một vấn đề ở phía sản xuất. Các chip bên trong một gói nâng cao phải tồn tại trong quá trình lắp ráp và sản xuất, trong đó một số vấn đề về CTE tương tự có thể trở thành vấn đề.

Ví dụ, hãy xem xét khuôn đúc chung (CoD2W), sử dụng liên kết nén nhiệt để gắn khuôn vào tấm bán dẫn. Rama Puligadda, giám đốc điều hành R&D công nghệ tiên tiến tại cho biết: “Trong quy trình CoD2W, có những tình huống trong đó các khuôn khác nhau đến từ các nguồn khác nhau và có thể có chiều cao hoặc độ dày khác nhau”. Khoa học nấu bia. “Khi bạn lắp những khuôn này vào vật mang, rất khó để biết liệu tất cả các khuôn có tiếp xúc với mục tiêu trong quá trình liên kết hay không. Các đặc tính cơ học của chất kết dính gắn khuôn được thiết kế để cho phép khuôn cao hơn hơi dính vào trong quá trình liên kết, điều này cho phép tất cả các khuôn tiếp xúc tốt với tấm wafer mục tiêu.”

Điều đó đặt ra những vấn đề khác nhau. Puligadda cho biết: “Những thách thức đối với vật liệu của chúng tôi bao gồm giới hạn nhiệt độ của các khuôn khác nhau. “Chúng tôi phải đảm bảo rằng nhiệt độ được sử dụng cho vật liệu liên kết không vượt quá giới hạn nhiệt của bất kỳ con chip nào đang được tích hợp vào gói. Ngoài ra, có thể có một số quy trình tiếp theo như hình thành hoặc đúc lớp phân phối lại. Vật liệu của chúng tôi phải tồn tại trong những quá trình đó. Chúng phải tồn tại trước các hóa chất mà chúng tiếp xúc trong suốt quá trình đóng gói. Ứng suất cơ học trong bao bì tạo thêm thách thức cho vật liệu liên kết.”

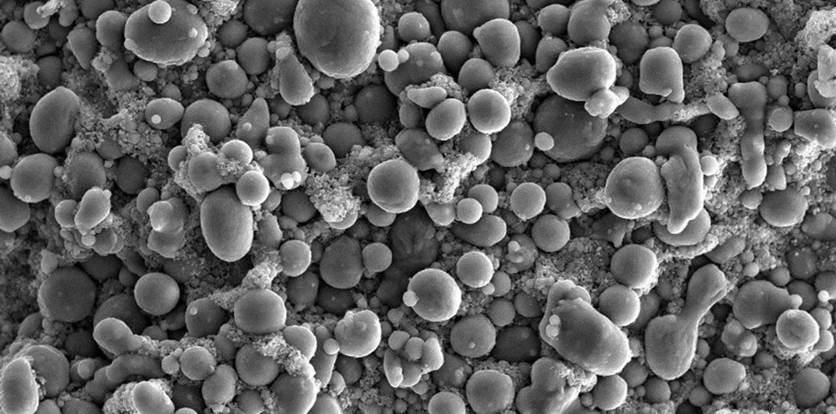

Một loạt các vật liệu đang được phát triển có khả năng dẫn nhiệt cũng như cách điện vượt trội. Những vật liệu giao diện nhiệt (TIM) được thiết kế mới này cung cấp các đường dẫn nhiệt hiệu quả giữa chip và bộ làm mát của nó mà không ảnh hưởng đến hiệu suất của chip. TIM không chỉ có khả năng dẫn nhiệt được cải thiện mà còn đáp ứng được những sai lệch nhỏ do sự sinh nhiệt không đều trên bề mặt chip.

Orji cho biết: “Việc quản lý nhiệt sẽ yêu cầu các vật liệu nhiệt mới cũng như cấu trúc liên kết mạch mới sử dụng chất nền tiên tiến và khả năng tích hợp không đồng nhất”. “Bởi vì các con chip được đóng gói rất gần nhau nên khả năng truyền nhiệt dư thừa rất hạn chế.”

Hình 2: Cái nhìn chi tiết về vật liệu giao diện nhiệt polymer chứa đầy hạt. Nguồn: Amkor

Lý tưởng nhất là những vật liệu mới này sẽ thể hiện các liên kết cộng hóa trị mạnh và khối lượng anion-cation cân bằng, giống như cấu trúc nguyên tử đơn giản được tìm thấy trong kim cương. Các vật liệu được công nhận trong danh mục này bao gồm kim cương, cùng với các hợp chất như oxit berili, nhôm nitrit, boron nitrit và ở một mức độ nào đó là silicon nitrit. Bất chấp khả năng dẫn nhiệt, những vật liệu này đặt ra những thách thức trong sản xuất do chính các liên kết mang lại độ bền cho chúng, chẳng hạn như đòi hỏi các quy trình thiêu kết ở nhiệt độ cao để đạt được mật độ mong muốn. Một ngoại lệ là kim cương, không thể thiêu kết được.

Một cách tiếp cận để khai thác lợi ích của những vật liệu này, bất chấp những thách thức trong quá trình xử lý, bao gồm việc sử dụng vật liệu tổng hợp. Ví dụ, việc kết hợp nhôm nitrit trong hỗn hợp epoxy sẽ mang lại một phần lợi thế về xử lý nhiệt, mặc dù nó không phù hợp với mức độ dẫn điện của vật liệu gốm rắn. Sự kết hợp các đặc tính vật liệu này rất quan trọng trong bao bì điện tử, nơi mong muốn có một chất dẫn điện tuyệt vời có thể hút đủ nhiệt ra khỏi lõi chip để tránh ảnh hưởng đến hiệu suất tín hiệu.

Kim cương, nổi tiếng vì độ cứng cực cao, nổi bật như một chất dẫn nhiệt và chất cách điện mẫu mực. Các vật liệu polyme như Teflon (Polytetrafluoroethylene hoặc PTFE), mặc dù kém dẫn điện hơn gốm sứ hoặc kim cương nhưng vẫn vượt trội hơn nhiều loại nhựa về khả năng dẫn nhiệt và mang lại khả năng cách điện đáng tin cậy. PTFE đủ hiệu quả để sử dụng làm vật liệu phủ trong các ứng dụng cần nhiều nhiệt như dụng cụ nấu ăn.

Thủy tinh, sứ và các loại gốm sứ dày đặc khác có chung đặc tính cách nhiệt và dẫn nhiệt này. Chúng tạo ra các giải pháp thiết thực, đặc biệt trong trường hợp cần có chất cách điện tốt để quản lý nhiệt. Nhôm nitrit (AlN) được sử dụng làm chất cách điện trong các thiết bị bán dẫn, thu hẹp khoảng cách giữa khuôn và các bộ phận truyền nhiệt. Mặc dù không dẫn nhiệt tốt như oxit berili nhưng AlN mang lại giải pháp thay thế an toàn hơn và tiết kiệm chi phí hơn. Ngoài ra, AlN còn vượt trội hơn các chất cách điện tiêu chuẩn khác như mica, polyimide và alumina về quản lý nhiệt.

Sapphire tổng hợp cũng đáng được chú ý nhờ giá cả phải chăng và tính dễ uốn thành nhiều dạng khác nhau, khiến nó trở thành một nhân tố có giá trị khác trong lĩnh vực đóng gói chất bán dẫn. Mỗi vật liệu này đều có những ưu điểm riêng trong thiết kế bao bì, trong đó việc kiểm soát nhiệt mà không cản trở hiệu suất điện tử là điều tối quan trọng.

Mặc dù các vật liệu tiên tiến như kim cương và nhôm nitrit luôn đi đầu trong việc giải quyết các thách thức về nhiệt trong các thiết bị bán dẫn, nhưng không phải tất cả các giải pháp đều yêu cầu các thành phần lạ hoặc cứng. Mỡ nhiệt và chất kết dính đóng vai trò là mô liên kết trong bao bì điện tử, lấp đầy những khoảng trống nhỏ hoặc những điểm bất thường trên bề mặt và tạo điều kiện truyền nhiệt giữa các bộ phận có địa hình khác nhau. Khả năng phù hợp với các bề mặt của chúng mang lại sự bổ sung quan trọng cho các giải pháp quản lý nhiệt vững chắc hơn, hình thành một cách tiếp cận toàn diện về tản nhiệt. Với mục tiêu cải tiến những vật liệu này, các nhà nghiên cứu đặt mục tiêu nâng cao đặc tính dẫn nhiệt của chúng, khiến chúng trở thành đối tác hiệu quả hơn trong mô hình quản lý nhiệt.

“Mỡ chịu nhiệt và chất kết dính nhiệt có tính dẫn nhiệt,” Fromm cho biết thêm, “Nhưng so với các vật liệu như gốm thông thường có tính dẫn nhiệt, chúng dẫn nhiệt kém gấp 10 lần. Những vật liệu này không tốt và có những lý do vật lý và hóa học. Có rất nhiều điều có thể đạt được ở đó và có rất nhiều công việc đang diễn ra trong không gian đó.”

Nhìn về phía trước

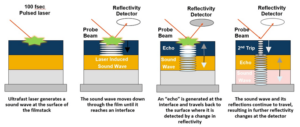

Khi các vật liệu mới mở đường cho khả năng giảm nhiệt, các kỹ thuật làm mát mới cải tiến cũng đang được phát triển. Các kênh vi mô silicon, là những con đường có quy mô cực nhỏ được khắc vào chất nền, có thể dẫn chất làm mát trực tiếp đến trung tâm của các điểm nóng. Phương pháp làm mát trực tiếp này vượt trội hơn so với tản nhiệt truyền thống nhưng đặt ra những thách thức về thiết kế, lắp ráp và độ tin cậy.

Tương tự, sự phát triển của hệ thống làm mát bằng chất lỏng vòng kín có thể cho phép các bộ phận luôn mát mà không bị hạn chế bởi các phương pháp luồng không khí. Các hệ thống này hứa hẹn mang lại nhiệt độ hoạt động mát hơn mà không có nguy cơ bị giảm nhiệt, nhưng cần thực hiện nhiều nghiên cứu cả về thiết kế và xử lý quy trình cho hệ thống làm mát bằng chất lỏng.

Một lựa chọn khác là chỉ cần đảo ngược cấu trúc của khuôn xếp chồng lên nhau, do đó thay vì đặt bộ nhớ lên trên logic, logic được đặt lên trên bộ nhớ với một bộ tản nhiệt ở trên. Winbond đã đề xuất điều này bằng công nghệ phần tử siêu băng thông (CUBE) tùy chỉnh, một phương pháp hiệu suất cao xếp khuôn trên SoC trực tiếp vào bộ nhớ, sau đó được gắn vào đế bằng các via xuyên silicon. Cách tiếp cận này, theo CS Lin, giám đốc tiếp thị tại winbond, sử dụng ít năng lượng hơn, từ đó làm giảm nhiệt. Ngoài ra, nó cho phép loại bỏ nhiệt trực tiếp, thay vì truyền nhiệt qua một mê cung gồm các thành phần không đồng nhất.

Một lựa chọn khác là sử dụng tính năng quản lý nhiệt theo thời gian thực, được hỗ trợ bởi AI. Các thuật toán giờ đây có thể giám sát nhiệt độ ở nhiều vị trí khác nhau trên chip, điều khiển tài nguyên làm mát một cách linh hoạt, đảm bảo hiệu suất tối ưu mà không vượt qua giới hạn nhiệt đỏ. Ví dụ, ProteanTecs vừa tung ra một giải pháp nhắm vào trung tâm dữ liệu mà hãng cho biết có thể giảm điện năng trong máy chủ bằng cách giảm lượng dải bảo vệ cần thiết để bảo vệ chip khỏi quá nóng. Cách tiếp cận này dựa vào việc giám sát các thay đổi từ bên trong chip và đưa ra các điều chỉnh khi cần thiết.

Synopsys và Siemens EDA cũng có sẵn các giải pháp để theo dõi những thay đổi về nhiệt độ và hoạt động khác nhau bằng cách sử dụng các cảm biến bên trong. Khả năng nhận được các chỉ số từ bên trong gói hàng bằng phương pháp đo từ xa là một thành phần ngày càng quan trọng trong việc quản lý nhiệt.

Swinnen cho biết thêm: “Bạn có cấu trúc cơ học của các con chip trên chip và trên bộ chuyển đổi với hàng nghìn hoặc hàng triệu va chạm vi mô, và tất cả chúng đều giãn nở và co lại khi chip nóng lên”. “Tùy thuộc vào bản đồ nhiệt của bạn, tính toàn vẹn nguồn điện của bạn sẽ phải thích ứng với cấu hình nhiệt độ cục bộ trong thời gian thực. Bạn có thể tính toán mức năng lượng mà một con chip phát ra, nhưng nhiệt độ mang lại cho nó là bao nhiêu thì còn tùy thuộc. Nó đang nằm trên một cái đĩa lạnh hay nó đang nằm dưới ánh mặt trời ở sa mạc Sahara? Cùng một con chip và cùng một hoạt động có thể dẫn đến nhiệt độ rất khác nhau tùy thuộc vào môi trường xung quanh.”

Ngoài ra, nghiên cứu về các vật liệu chuyển pha, hấp thụ nhiệt bằng cách thay đổi trạng thái của chúng, hứa hẹn khả năng điều chỉnh nhiệt độ thụ động nhưng mạnh mẽ. Hơn thế nữa, việc khám phá các hệ thống làm mát sinh học, cố gắng bắt chước phản ứng của cơ thể con người với nhiệt, báo trước một tương lai nơi các thiết bị của chúng ta có thể tản nhiệt một cách trực quan như chúng ta đổ mồ hôi.

Kết luận

Khi ngành công nghiệp bán dẫn tiếp tục vượt qua các ranh giới về hiệu suất và khả năng tích hợp, việc quản lý nhiệt trong bao bì tiên tiến vẫn là một thách thức. Ở một phía của quang phổ, sự phức tạp về nhiệt ngày càng tăng xuất hiện khi các công ty hướng tới các mô-đun đa chip có mật độ dày đặc hơn. Ngược lại, những tiến bộ trong khoa học vật liệu và công nghệ làm mát tiên tiến cố gắng giảm bớt căng thẳng về nhiệt. Cả hai đều cần phải giải quyết những thách thức phức tạp về nhiệt, nhưng vẫn còn rất nhiều việc phải làm để giải quyết vấn đề này một cách nhất quán và có thể dự đoán được.

- Ed Sperling đã đóng góp vào báo cáo này.

Đọc liên quan

Quản lý ứng suất do nhiệt gây ra trong chip

Tích hợp không đồng nhất và mật độ ngày càng tăng tại các nút nâng cao đang tạo ra một số thách thức phức tạp và khó khăn cho việc sản xuất và đóng gói vi mạch.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiengineering.com/navigating-heat-in-advanced-packaging/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 1

- 10

- 12

- 25

- 3d

- 8

- a

- có khả năng

- Có khả năng

- Giới thiệu

- tăng tốc

- chấp nhận được

- Theo

- Đạt được

- đạt được

- ngang qua

- hoạt động

- thích ứng

- thêm vào

- Ngoài ra

- thêm vào

- Ngoài ra

- địa chỉ

- giải quyết

- Thêm

- Chất kết dính

- điều chỉnh

- điều chỉnh

- tiên tiến

- Vật liệu tiên tiến

- tiến bộ

- lợi thế

- ảnh hưởng đến

- một lần nữa

- Lão hóa

- cách đây

- trước

- AI

- nhằm mục đích

- nhằm vào

- KHÔNG KHÍ

- dòng chảy

- thuật toán

- Tất cả

- giảm bớt

- cho phép

- cho phép

- ALN

- dọc theo

- Ngoài ra

- thay thế

- Mặc dù

- luôn luôn

- số lượng

- an

- phân tích

- và

- Một

- bất kì

- các ứng dụng

- phương pháp tiếp cận

- LÀ

- khu vực

- xung quanh

- AS

- các khía cạnh

- hợp ngữ

- đánh giá

- At

- nguyên tử

- đính kèm

- Nỗ lực

- sự chú ý

- tự trị

- xe tự trị

- xa

- trở lại

- Cân bằng

- dựa

- BE

- bởi vì

- trở nên

- trở thành

- trở thành

- được

- trước

- được

- Lợi ích

- Hơn

- giữa

- Ngoài

- lớn nhất

- Trộn

- Trái phiếu

- cả hai

- ranh giới

- Phá vỡ

- cầu nối

- Mang lại

- xây dựng

- gánh nặng

- kinh doanh

- phát triển kinh doanh

- nhưng

- by

- tính toán

- CAN

- khả năng

- chụp

- trường hợp

- Phân loại

- phục vụ

- Nguyên nhân

- nổi tiếng

- Trung tâm

- Trung tâm

- trung tâm

- nhất định

- thách thức

- thách thức

- thách thức

- thay đổi

- thay đổi

- Những thay đổi

- thay đổi

- kiểm tra

- hóa chất

- hóa chất

- Chip

- Snacks

- lựa chọn

- lựa chọn

- Đóng

- lạnh

- Tập thể

- chung

- Đến

- đến

- cộng đồng

- Các công ty

- so

- tương thích

- Bổ sung

- phức tạp

- phức tạp

- phức tạp

- compliant

- phức tạp

- thành phần

- các thành phần

- toàn diện

- thỏa hiệp

- Tính

- Liên quan

- Mối quan tâm

- điều kiện

- Tiến hành

- độ dẫn

- dẫn

- Kết nối

- sự cân nhắc

- xem xét

- thích hợp

- khó khăn

- xây dựng

- người tiêu dùng

- Thiết bị điện tử tiêu dùng

- liên lạc

- liên tiếp

- hợp đồng

- đóng góp

- kiểm soát

- thì thầm

- Mát mẻ

- Copper

- Doanh nghiệp

- chi phí-hiệu quả

- tốn kém

- có thể

- Đối tác

- CỘNG TRỊ

- Tạo

- quan trọng

- băng qua

- quan trọng

- tùy chỉnh

- hư hại

- dữ liệu

- Trung tâm dữ liệu

- các trung tâm dữ liệu

- David

- xử lý

- quyết định

- nhu cầu

- ngu si

- mật độ

- Tùy

- phụ thuộc

- Thiết kế

- quá trình thiết kế

- thiết kế

- nhà thiết kế

- thiết kế

- thiết kế

- mong muốn

- Mặc dù

- chi tiết

- chi tiết

- chi tiết

- phát triển

- Phát triển

- phát triển

- thiết bị

- Thiết bị (Devices)

- ma quỷ

- Diamond

- Die

- khác nhau

- khó khăn

- kỹ thuật số

- trực tiếp

- đạo diễn

- trực tiếp

- Giám đốc

- thảo luận

- khoảng cách

- phân phát

- phân phối

- do

- làm

- Không

- thực hiện

- dont

- diệt vong

- xuống

- vẽ

- rút

- lái xe

- hai

- suốt trong

- năng động

- mỗi

- Sớm hơn

- dễ dàng

- ed

- Hiệu quả

- hiệu quả

- hiệu ứng

- hiệu quả

- hiệu quả

- điện tử

- Thiết bị điện tử

- các yếu tố

- khác

- nhúng

- xuất hiện

- việc làm

- cho phép

- cuối

- thiết kế

- Kỹ Sư

- Kỹ sư

- nâng cao

- tăng cường

- đủ

- đảm bảo

- đảm bảo

- Toàn bộ

- phong bì

- đặc biệt

- thiết yếu

- Ngay cả

- sự kiện

- Mỗi

- tất cả mọi thứ

- phát triển

- ví dụ

- quá

- tuyệt vời

- ngoại lệ

- dư thừa

- điều hành

- Giám đốc điều hành

- triển lãm

- Exotic

- Mở rộng

- mở rộng

- mong đợi

- dự kiến

- đắt tiền

- chuyên gia

- thăm dò

- thêm

- mở rộng

- mức độ

- cực

- Đối mặt

- tạo điều kiện

- yếu tố

- thất bại

- không

- Không

- xa

- Tính năng

- lĩnh vực

- Sung

- Hình

- hình

- đầy

- đổ đầy

- tìm kiếm

- dòng chảy

- Tập trung

- Trong

- đi đầu

- hình thức

- hình thành

- các hình thức

- Ra

- tìm thấy

- từ

- đầy đủ

- chức năng

- chức năng

- chức năng

- cơ bản

- tương lai

- khoảng cách

- khoảng trống

- thế hệ

- thế hệ

- Trí tuệ nhân tạo

- George

- được

- được

- Go

- đi

- tốt

- có

- gradients

- tay

- Xử lý

- Xảy ra

- Cứng

- Khai thác

- Có

- he

- Trái Tim

- chiều cao

- giúp

- Cao

- hiệu suất cao

- cao hơn

- bản lề

- NÓNG BỨC

- Độ đáng tin của

- Hướng dẫn

- HTTPS

- Nhân loại

- i

- IBM

- ý tưởng

- xác định

- xác định

- if

- Va chạm

- bắt buộc

- quan trọng

- Áp đặt

- cải thiện

- cải thiện

- in

- bao gồm

- bao gồm

- Bao gồm

- kết hợp

- tăng

- tăng

- lên

- ngành công nghiệp

- vốn có

- sự đổi mới

- sáng tạo

- trong

- ví dụ

- thay vì

- tích hợp

- Tích hợp

- hội nhập

- tính toàn vẹn

- dự định

- Giao thức

- sự can thiệp

- giao thoa

- nội bộ

- trong

- phức tạp

- liên quan đến

- vấn đề

- các vấn đề

- IT

- ITS

- chính nó

- jpg

- chỉ

- Key

- Biết

- mê cung

- phần lớn

- mới nhất

- Luật

- lớp

- dẫn

- Dẫn

- trái

- Cho vay

- ít

- Cấp

- niveaux

- tận dụng

- vòng đời

- nâng

- Lượt thích

- giới hạn

- hạn chế

- Hạn chế

- giới hạn

- lin

- Dòng

- Chất lỏng

- tải

- địa phương

- . Các địa điểm

- logic

- còn

- Rất nhiều

- Thấp

- thấp hơn

- thực hiện

- duy trì

- làm cho

- Làm

- quản lý

- quản lý

- giám đốc

- quản lý

- Các nhà sản xuất

- sản xuất

- nhiều

- bản đồ

- Marketing

- quần chúng

- Trận đấu

- vật liệu

- nguyên vật liệu

- max-width

- Có thể..

- cơ khí

- Memories

- Bộ nhớ

- Kim loại

- phương pháp

- phương pháp

- phương pháp

- Mica

- Might

- hàng triệu

- nhỏ

- phút

- giảm nhẹ

- pha

- di động

- Chế độ

- người mẫu

- mô-đun

- Modules

- Màn Hình

- giám sát

- màn hình

- Monolithic

- chi tiết

- hầu hết

- nhiều

- đa lĩnh vực

- nhiều

- phải

- quốc dân

- Thiên nhiên

- điều hướng

- sự cần thiết

- Cần

- cần thiết

- nhu cầu

- không bao giờ

- Mới

- mới

- tiếp theo

- Không

- các nút

- không

- tiểu thuyết

- tại

- con số

- of

- cung cấp

- Cung cấp

- thường

- on

- ONE

- có thể

- hoạt động

- hoạt động

- đối diện

- tối ưu hóa

- Tối ưu hóa

- tối ưu

- Tùy chọn

- Các lựa chọn

- or

- Nền tảng khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- ra

- đầu ra

- kết thúc

- tổng thể

- Vượt qua

- Gói

- gói

- đóng gói

- gói

- bao bì

- đóng gói

- bảng điều khiển

- thảo luận nhóm

- mô hình

- Paramount

- một phần

- đặc biệt

- Đối tác

- các bộ phận

- thụ động

- đường dẫn

- con đường

- mở đường

- hiệu suất

- giai đoạn

- vật lý

- mảnh

- trụ cột

- quan trọng

- Nơi

- đặt

- nhựa

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- máy nghe nhạc

- polymer

- mạnh

- quyền lực

- -

- Thực tế

- dự đoán

- Dự đoán

- Sớm

- quà

- Chủ tịch

- ngăn chặn

- ưu tiên

- có lẽ

- Vấn đề

- quá trình

- xử lý

- Quy trình

- xử lý

- bộ vi xử lý

- Sản phẩm

- Hồ sơ

- Profiles

- chương trình

- lời hứa

- Hứa hẹn

- tài sản

- bảo vệ

- cho

- cung cấp

- cung cấp

- Đẩy

- đặt

- Đặt

- R & D

- tăng giá

- nâng cao

- dốc

- phạm vi

- Giá

- hơn

- thực

- thời gian thực

- thực tế

- hiện thực hóa

- có thật không

- lý do

- gần đây

- công nhận

- công nhận

- đỏ

- giảm

- Giảm

- làm giảm

- giảm

- về

- Quy định

- độ tin cậy

- đáng tin cậy

- cứu trợ

- vẫn còn

- tẩy

- Đã loại bỏ

- báo cáo

- đại diện cho

- yêu cầu

- cần phải

- yêu cầu

- đòi hỏi

- nghiên cứu

- nhà nghiên cứu

- giải quyết

- Thông tin

- phản ứng

- kết quả

- kết quả

- đảo ngược

- ngay

- cứng nhắc

- Mọc

- Nguy cơ

- lộ trình

- Cán

- Route

- chạy

- s

- an toàn hơn

- Nói

- tương tự

- nói

- Quy mô

- mở rộng quy mô

- Đề án

- KHOA HỌC

- Nhà khoa học

- liền mạch

- nhìn thấy

- đã xem

- phân khúc

- bán dẫn

- Chất bán dẫn

- cao cấp

- cảm biến

- phục vụ

- máy chủ

- một số

- Hình dạng

- Chia sẻ

- thay đổi

- thay đổi

- ngắn

- bên

- Siemens

- Tín hiệu

- tín hiệu

- có ý nghĩa

- đáng kể

- Silicon

- tương tự

- Đơn giản

- đơn giản

- kể từ khi

- duy nhất

- Ngồi

- tình huống

- Kích thước máy

- kích thước

- chậm rãi

- nhỏ

- So

- rắn

- giải pháp

- Giải pháp

- động SOLVE

- một số

- một cái gì đó

- nguồn

- nguồn

- Không gian

- quang phổ

- lan tràn

- ngăn xếp

- xếp chồng lên nhau

- xếp chồng

- Stacks

- Traineeship

- Tiêu chuẩn

- đứng

- Tiểu bang

- Bang

- ở lại

- Vẫn còn

- chiến lược

- sức mạnh

- căng thẳng

- phấn đấu

- mạnh mẽ

- cấu trúc

- tiếp theo

- như vậy

- mặt trời

- cao

- Bề mặt

- vượt qua

- vượt qua

- tồn tại

- hiệp lực

- hệ thống

- hệ thống

- giải quyết

- Mục tiêu

- kỹ thuật

- Công nghệ

- Công nghệ

- 10

- khủng khiếp

- hơn

- việc này

- Sản phẩm

- Nguồn

- cung cấp their dịch

- Them

- sau đó

- Đó

- nhiệt

- Kia là

- họ

- nghĩ

- Suy nghĩ

- điều này

- những

- Tuy nhiên?

- nghĩ

- hàng ngàn

- mối đe dọa

- ba chiều

- Thông qua

- khắp

- thời gian

- mô

- đến

- bên nhau

- quá

- công cụ

- hàng đầu

- đối với

- truyền thống

- chuyển

- đi du lịch

- kinh hai

- cố gắng

- cố gắng

- XOAY

- hai

- điển hình

- Cuối cùng

- Dưới

- hiểu

- sự hiểu biết

- không may

- độc đáo

- UPS

- upside

- sử dụng

- trường hợp sử dụng

- đã sử dụng

- sử dụng

- sử dụng

- tận dụng

- Bằng cách sử dụng

- Quý báu

- khác nhau

- thay đổi

- Xe cộ

- nhà cung cấp

- theo chiều dọc

- rất

- phó

- Phó Chủ Tịch

- Xem

- muốn

- Làm ấm

- là

- Đường..

- cách

- we

- TỐT

- là

- Điều gì

- Là gì

- khi nào

- liệu

- cái nào

- trong khi

- tại sao

- sẽ

- với

- ở trong

- không có

- Công việc

- đang làm việc

- tệ hơn

- Sai

- năm

- nhưng

- Năng suất

- bạn

- trên màn hình

- zephyrnet