Seit seinem Debüt in den 1980er-Jahren mit gemeinsam genutzten 10-Mbit/s-LANs über Koaxialkabel hat Ethernet stetige Fortschritte gemacht und verfügt nun über das Potenzial, Geschwindigkeiten von bis zu 1.6 Tbit/s zu unterstützen. Dieser Fortschritt hat es Ethernet ermöglicht, eine breitere Palette von Anwendungen zu bedienen, wie z. B. Live-Streaming, Funkzugangsnetzwerke und industrielle Steuerung, was die Bedeutung einer zuverlässigen Paketübertragung und Dienstqualität unterstreicht. Da die aktuelle Internetbandbreite bei etwa 500 Tbit/s liegt, besteht ein wachsender Bedarf an einer verbesserten Back-End-Verkehrsabwicklung innerhalb des Rechenzentrums. Obwohl einzelne Server noch nicht auf dem Terabit-pro-Sekunde-Niveau arbeiten, nähert sich der gesamte Rechenzentrumsverkehr diesem Ausmaß, was die 802.3dj-Gruppe des IEEE dazu veranlasst, Standardisierungsbemühungen zu unternehmen und robuste Ethernet-Controller und SerDes zur Verwaltung des wachsenden Datenflusses erforderlich zu machen. Vor dem Hintergrund steigender Anforderungen erreicht die Interprozessorkommunikation bereits diese Geschwindigkeiten.

Die Kommunikation zwischen Prozessoren führt zu einem Bedarf an 1.6T-Raten mit minimaler Latenz. Während einzelne Geräte durch ihre inhärente Verarbeitungskapazität und Chipgröße eingeschränkt sind, können diese Kapazitäten durch die Kombination von Chips erheblich erweitert werden. Der ersten Anwendungsgeneration sollen voraussichtlich Switch-to-Switch-Verbindungen innerhalb des Rechenzentrums folgen, die die Bündelung von Hochleistungsprozessoren und Speicher ermöglichen und so die Skalierbarkeit und Effizienz im Cloud Computing steigern.

IEEE 802.3dj-Initiative: Weiterentwicklung von Ethernet-Standards für 1.6-Tbit/s-Interoperabilität

Die Einhaltung der sich entwickelnden Standardisierungsbemühungen ist für eine nahtlose Ökosystem-Interoperabilität von entscheidender Bedeutung. Die 802.3dj-Gruppe des IEEE ist dabei, den kommenden Ethernet-Standard zu formulieren, der physikalische Schichten und Verwaltungsparameter für Geschwindigkeiten von 200 G bis zu 1.6 Terabit pro Sekunde umfasst. Das Ziel der Gruppe ist eine Ethernet-MAC-Datenrate von 1.6 Tbit/s und eine maximale Bitfehlerrate von nicht mehr als 10-13 auf der MAC-Ebene. Zu den weiteren Bestimmungen gehören optionale 16- und 8-spurige Attachment Unit Interfaces (AUI), die für verschiedene Chipanwendungen geeignet sind und 112G- und 224G-SerDes nutzen. Physikalisch sieht die 1.6-Tbit/s-Spezifikation die Übertragung über 8 Paar Kupfer-Twinax-Kabel für bis zu einem Meter und 8 Paar Glasfaser für Entfernungen zwischen 500 Metern und 2 km vor. Obwohl mit der vollständigen Ratifizierung des Standards bis zum Frühjahr 2026 gerechnet wird, wird mit einer Fertigstellung der Kernfunktionen im Jahr 2024 gerechnet.

Bandbreiten-Overhead und Fehlerkorrektur in einem 1.6T-Ethernet-Subsystem

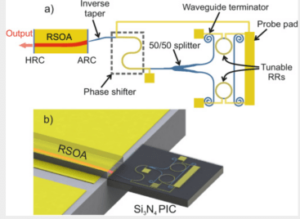

Abb. 1: Diagramm, das die Komponenten eines 1.6T-Ethernet-Subsystems darstellt.

In früheren Ethernet-Iterationen konzentrierte sich das PCS hauptsächlich auf die Datenkodierung für eine zuverlässige Paketerkennung. Mit der Steigerung der Ethernet-Geschwindigkeit auf 1.6T wird jedoch die Notwendigkeit einer Vorwärtsfehlerkorrektur (FEC) deutlich, insbesondere um einer Signalverschlechterung auch bei kurzen Verbindungen entgegenzuwirken. Zu diesem Zweck nutzt 1.6T Ethernet weiterhin Reed-Solomon FEC. Bei diesem Ansatz wird ein Codewort erstellt, das aus 514 10-Bit-Symbolen besteht, die in einen 544-Symbolblock codiert sind, was zu einem Bandbreiten-Overhead von 6 % führt. Diese FEC-Codewörter werden über die physischen AUI-Links verteilt, sodass nicht jeder physische Link (8 für 1.6T-Ethernet) ein ganzes Codewort trägt. Diese Methode bietet nicht nur zusätzlichen Schutz vor Fehlerhäufen, sondern ermöglicht auch die Parallelisierung am Decoder am anderen Ende und reduziert so die Latenz.

Der Physical Medium Attachment (PMA) mit Getriebe und SerDes bringt das Ethernet-Signal auf die übertragenen Kanäle. Bei 1.6T-Ethernet umfasst dies 8 Kanäle mit jeweils 212 Gbit/s, was einem FEC-Overhead von 6 % entspricht. Bei der verwendeten Modulationstechnik handelt es sich um die 4-Level Pulse Amplitude Modulation (PAM-4), die zwei Datenbits für jedes Übertragungssymbol codiert und so die Bandbreite im Vergleich zum herkömmlichen Non-Return Zero (NRZ)-Ansatz effektiv verdoppelt. Der Übertragungsmechanismus basiert auf einer Digital-Analog-Wandlung, während auf der Empfangsseite eine Analog-Digital-Wandlung in Kombination mit DSPs für eine genaue Signalextraktion sorgt.

Darüber hinaus ist es wichtig zu beachten, dass das Ethernet PCS einen „äußeren FEC“ einführt, der sich durchgängig über eine Ethernet-Verbindung erstreckt. Um Kanäle mit größerer Reichweite zu stärken, ist eine zusätzliche Ebene der Fehlerkorrektur für einzelne physische Leitungen in Planung, wahrscheinlich unter Verwendung eines Hamming-Codes FEC. Es wird erwartet, dass diese Korrektur ihre primäre Anwendung in optischen Transceivermodulen findet, wo eine solche Korrektur zwingend erforderlich ist.

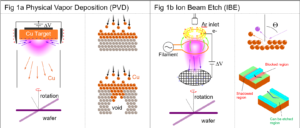

Abb. 2: Diagramm, das den zusätzlichen Overhead zeigt, der durch die Verwendung eines verketteten FEC für eine größere Reichweite entsteht.

In dem in Abbildung 2 dargestellten Beispielsystem sind MAC und PCS über ein optisches Modul und eine Glasfaserstrecke verbunden. Der PCS hat eine Bitfehlerrate von 10-5 an der optischen Modulverbindung sowie Fehler von der optischen Verbindung selbst. Die Verwendung eines einzigen RS-FEC-End-to-End würde nicht ausreichen, um die 10 zu erreichen-13 Ethernet-Standard, wodurch die Verbindung unzuverlässig wird. Eine Option wäre eine dreifache Implementierung eines separaten RS-FEC bei jedem Hop, was die Kosten und die Latenz deutlich erhöhen würde. Eine effektivere Lösung ist die Integration eines verketteten Hamming-Code-FEC speziell für die optische Verbindung, der den typischen Zufallsfehlern optischer Verbindungen Rechnung trägt. Diese innere FEC-Schicht sorgt für eine zusätzliche Erweiterung der Leitungsrate von 212 Gbit/s auf 226 Gbit/s, daher ist es wichtig, dass der SerDes diese Leitungsrate unterstützen kann.

Latenzprobleme in 1.6T-Ethernet-Systemen

Abb. 3: Latenzpfad für das 1.6T-Ethernet-Subsystem.

Verschiedene Komponenten tragen zur Ethernet-Latenz bei: die Übertragungswarteschlange, die Übertragungsdauer, die mittlere Durchlaufzeit sowie verschiedene Verarbeitungs- und Empfangszeiten. Um dies zu veranschaulichen, betrachten Sie Abbildung 3, die ein umfassendes 1.6T-Ethernet-Subsystem zeigt. Während die Latenz durch die Reaktionszeit der Remote-End-Anwendung beeinflusst werden kann, ist dieser Faktor außerhalb von Ethernet und wird daher bei der Latenzanalyse oft ausgeschlossen. Um die Latenz an der Ethernet-Schnittstelle zu minimieren, müssen die spezifischen Umstände verstanden werden. Beispielsweise ist die Latenz aufgrund der inhärenten Verzögerungen bei langsameren Client-Verbindungen möglicherweise kein primäres Problem bei Trunk-Verbindungen zwischen Switches. Auch die Distanz spielt eine Rolle; Größere Längen führen zu mehr Latenz. Das bedeutet natürlich nicht, dass wir die Latenz in anderen Szenarien übersehen sollten; die Reduzierung der Latenz ist immer ein Ziel.

Die Übertragungslatenz hängt von Natur aus mit der Ethernet-Rate und der Framegröße zusammen. Insbesondere für ein 1.6-T-Ethernet-System erfordert die Übertragung eines Pakets minimaler Größe 0.4 ns – im Wesentlichen ein Ethernet-Frame pro Tick eines 2.5-GHz-Takts. Andererseits dauert die Übertragung eines standardmäßigen Frames mit maximaler Größe 8 ns, bei Jumbo Frames sogar 48 ns. Das gewählte Medium bestimmt außerdem die Latenz. Beispielsweise weist Glasfaser typischerweise eine Latenzzeit von 5 ns pro Meter auf, während Kupferkabel mit 4 ns pro Meter geringfügig schneller sind.

Ein wesentlicher Teil der Gesamtlatenz ist auf den Empfänger-Controller zurückzuführen. Der RS-FEC-Decoder führt von Natur aus zu Latenz. Um eine Fehlerkorrektur einzuleiten, muss das System 4 Codewörter empfangen, was bei 1.6 Tbit/s 12.8 ns entspricht. Nachfolgende Aktivitäten, einschließlich Fehlerkorrektur und Pufferung, verstärken diese Latenz. Während die Speicherdauer des FEC-Codeworts konsistent bleibt, hängt die Latenz während des Nachrichtenempfangs von der spezifischen Implementierung ab. Dennoch kann die Latenz durch den Einsatz sorgfältiger digitaler Designstrategien optimiert werden.

Im Wesentlichen gibt es aufgrund des FEC-Mechanismus und der physischen Entfernung oder Kabellänge eine inhärente, unvermeidbare Latenz. Über diese Faktoren hinaus spielt Designkompetenz eine entscheidende Rolle, um die Latenz des Ethernet-Controllers zu minimieren. Der Einsatz einer Komplettlösung, die MAC, PCS und PHY integriert und optimiert, ebnet den Weg für die effizienteste Implementierung mit geringer Latenz.

Zusammenfassung

Abb. 4: Erster Silizium-Erfolg für Synopsys 224G Ethernet PHY IP im 3-nm-Prozess mit hochlinearen PAM-4-Augen.

1.6 Tbit/s Ethernet ist auf die bandbreitenintensivsten und latenzempfindlichsten Anwendungen zugeschnitten. Mit dem Aufkommen der 224G-SerDes-Technologie in Verbindung mit Fortschritten bei MAC und PCS IP stehen nun umfassende Lösungen zur Verfügung, die kontinuierlich den sich weiterentwickelnden 1.6T-Ethernet-Standards entsprechen. Darüber hinaus muss das digitale und analoge IP-Design aufgrund der dem Protokoll und den Fehlerkorrekturmethoden innewohnenden Latenz sorgfältig von erfahrenen Designern ausgearbeitet werden, um unnötige Latenzzeiten im Datenpfad zu vermeiden.

Um Spitzenleistungen für 1.6-T-SoC-Designs zu erzielen, sind eine effizient optimierte Architektur und sorgfältige Designpraktiken für jede Chipkomponente erforderlich. Dies betont die Energieeinsparung und minimiert den Silizium-Fußabdruck, wodurch Datenraten von 1.6 T Wirklichkeit werden. Silizium-erprobtes Synopsys 224G Ethernet PHY IP hat den Grundstein für den 1.6T MAC und den PCS-Controller gelegt. Mithilfe modernster Design-, Analyse-, Simulations- und Messtechniken liefert Synopsys weiterhin außergewöhnliche Signalintegrität und Jitter-Leistung mit einem komplette Ethernet-Lösung inklusive MAC+PCS+PHY.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- Zugang

- zugänglich

- Buchhaltung

- genau

- Erreichen

- über

- Aktivitäten

- hinzugefügt

- Zusätzliche

- zusätzlich

- Die Annahme

- Fortschritte

- Vorrückend

- gegen

- Anvisieren

- erlaubt

- bereits

- ebenfalls

- Obwohl

- immer

- inmitten

- Beträge

- verstärken

- an

- Analyse

- und

- Vorweggenommen

- Anwendung

- Anwendungen

- Ansatz

- Architektur

- SIND

- AS

- At

- vermeiden

- Back-End

- Hintergrund

- Bandbreite

- BE

- wird

- zwischen

- Beyond

- Bit

- Blockieren

- Nackenrolle

- Stärkung

- Brings

- baut

- aber

- by

- Kabel

- Kabel

- CAN

- Kapazitäten

- tragen

- Herausforderungen

- Kanäle

- Chip

- Pommes frites

- gewählt

- Umstände

- Auftraggeber

- Uhr

- Cloud

- Cloud Computing

- Code

- kombiniert

- Vereinigung

- Kommunikation

- abschließen

- Abschluss

- Komponente

- Komponenten

- umfassend

- umfassend

- Computing

- Hautpflegeprobleme

- Verbindung

- Sie

- Verbindungen

- CONSERVATION

- Geht davon

- Überlegungen

- konsistent

- weiter

- ständig

- beitragen

- Smartgeräte App

- Controller

- Umwandlung (Conversion)

- Kupfer

- Kernbereich

- Kosten

- entgegenwirken

- Kurs

- Gefertigt

- schafft

- Strom

- technische Daten

- Datacenter

- Debüt

- Verzögerungen

- Übergeben

- Demand

- anspruchsvoll

- Anforderungen

- darstellend

- Design

- Designer

- Designs

- Entdeckung

- Geräte

- diktiert

- anders

- digital

- fleißig

- Displays

- Abstand

- verteilt

- Tut nicht

- Verdoppelung

- zwei

- Dauer

- im

- jeder

- Früher

- Ökosystem

- Effektiv

- effektiv

- Effizienz

- effizient

- effizient

- Bemühungen

- Entstehung

- betont

- Betonung

- beschäftigt

- anstellen

- ermöglicht

- ermöglichen

- umfasst

- Ende

- End-to-End

- sorgt

- Ganz

- Fehler

- Fehler

- Eskalation

- Essenz

- essential

- im Wesentlichen

- Äther (ETH)

- Sogar

- Jedes

- offensichtlich

- sich entwickelnden

- Beispiel

- außergewöhnlich

- ausgeschlossen

- Ausbau

- Expansion

- erwartet

- Experte

- Expertise

- erweitern

- Verlängerung

- extern

- Extraktion

- Augenfarbe

- Faktor

- Faktoren

- weit

- beschleunigt

- Eigenschaften

- Einzigartige

- Abbildung

- Finden Sie

- Vorname

- Erste Generation

- Fluss

- konzentriert

- gefolgt

- Fußabdruck

- Aussichten für

- formulieren

- vorwärts

- FRAME

- für

- weiter

- Generation

- gibt

- mehr

- Gruppe an

- Gruppen

- persönlichem Wachstum

- Pflege

- Handling

- GUTE

- Hohe Leistungsfähigkeit

- hoch

- aber

- HTML

- HTTPS

- Imperativ

- Implementierung

- Bedeutung

- wichtig

- verbessert

- in

- In anderen

- das

- Einschließlich

- zunehmend

- Krankengymnastik

- industriell

- beeinflusst

- inhärent

- von Natur aus

- initiieren

- Initiative

- Instanz

- Integriert

- Integration

- Integrität

- Schnittstelle

- Schnittstellen

- Internet

- Flexible Kommunikation

- in

- innere

- einführen

- Stellt vor

- Einführung

- beinhaltet

- IP

- IT

- Iterationen

- SEINE

- selbst

- jpg

- Spur

- Latency

- Schicht

- Lagen

- Länge

- Cholesterinspiegel

- Nutzung

- wahrscheinlich

- Line

- Linien

- LINK

- Links

- leben

- länger

- Sneaker

- mac

- Making

- verwalten

- Management

- max-width

- maximal

- Kann..

- bedeuten

- Messung

- Mechanismus

- mittlere

- Memory

- Nachricht

- Methode

- Methoden

- sorgfältig

- minimal

- minimieren

- minimiert

- minimieren

- Modulen

- Module

- mehr

- vor allem warme

- sollen

- sich nähern

- Need

- Netzwerke

- dennoch

- nicht

- beachten

- jetzt an

- Ziel

- of

- vorgenommen,

- on

- EINEM

- einzige

- die

- optimiert

- Verbessert

- Option

- or

- Andere

- übrig

- Gesamt-

- Paare

- Parameter

- besonders

- Weg

- PCs

- für

- Leistung

- Leistungen

- physikalisch

- Physisch

- Pipeline

- zentrale

- Plato

- Datenintelligenz von Plato

- PlatoData

- spielt

- erfahren

- Potenzial

- Werkzeuge

- Praktiken

- in erster Linie

- primär

- Prozessdefinierung

- Verarbeitung

- Prozessoren

- Progression

- projektiert

- Sicherheit

- Protokoll

- Puls

- Zweck

- Schieben

- Qualität

- Radio

- zufällig

- Angebot

- Bewerten

- Honorar

- erreichen

- Erreichen

- Reaktion

- Realität

- erhalten

- Empfang

- Rezeption

- Reduzierung

- zuverlässig

- bleibt bestehen

- Rendering

- erfordert

- eingeschränkt

- was zu

- robust

- Rollen

- verwurzelt

- Laufen

- Skalierbarkeit

- Skalieren

- Szenarien

- nahtlos

- Zweite

- gesehen

- Segment

- empfindlich

- getrennte

- brauchen

- kompensieren

- mehrere

- von Locals geführtes

- Short

- sollte

- präsentiert

- Signal

- bedeutend

- Silizium

- Simulation

- Größe

- So

- Lösung

- Lösungen

- überspannt

- Speerspitze

- spezifisch

- speziell

- Spezifikation

- Geschwindigkeiten

- Feder

- Stufe

- Standard

- Standardisierung

- Normen

- Lagerung

- Strategien

- Streaming

- Folge

- wesentlich

- Erfolg

- so

- geeignet

- Support

- Symbol

- System

- zugeschnitten

- nimmt

- Technik

- Techniken

- Technologie

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- ihr

- Dort.

- damit

- deswegen

- Diese

- fehlen uns die Worte.

- Durch

- So

- Tick

- Gebunden

- Zeit

- mal

- zu

- Top

- traditionell

- der Verkehr

- privaten Transfer

- übertragen

- Verdreifachen

- XNUMX

- typisch

- typisch

- annehmbar

- Verständnis

- unternehmen

- Einheit

- anstehende

- auf

- Verwendung von

- Nutzen

- visualisieren

- Weg..

- we

- wann

- welche

- während

- breiter

- mit

- .

- würde

- noch

- Zephyrnet

- Null