Der spezifische Widerstand von Kupfer hängt von seiner Kristallstruktur, seinem Hohlraumvolumen, seinen Korngrenzen und der Nichtübereinstimmung der Materialgrenzflächen ab, was bei kleineren Maßstäben an Bedeutung gewinnt. Die Bildung von Kupferdrähten (Cu) erfolgt traditionell durch das Ätzen eines Grabenmusters in Low-k-Siliziumdioxid mithilfe eines Grabenätzprozesses und das anschließende Füllen des Grabens mit Cu über einen Damaszenerfluss. Leider entstehen bei dieser Methode multikristalline Strukturen mit erheblichen Korngrenzen und Hohlräumen, was den Widerstand des Cu-Drahts erhöht. In diesem Prozess wird auch ein hochohmiges TaN-Linermaterial verwendet, um die Cu-Diffusion während des Damaszener-Glühprozesses zu verhindern.

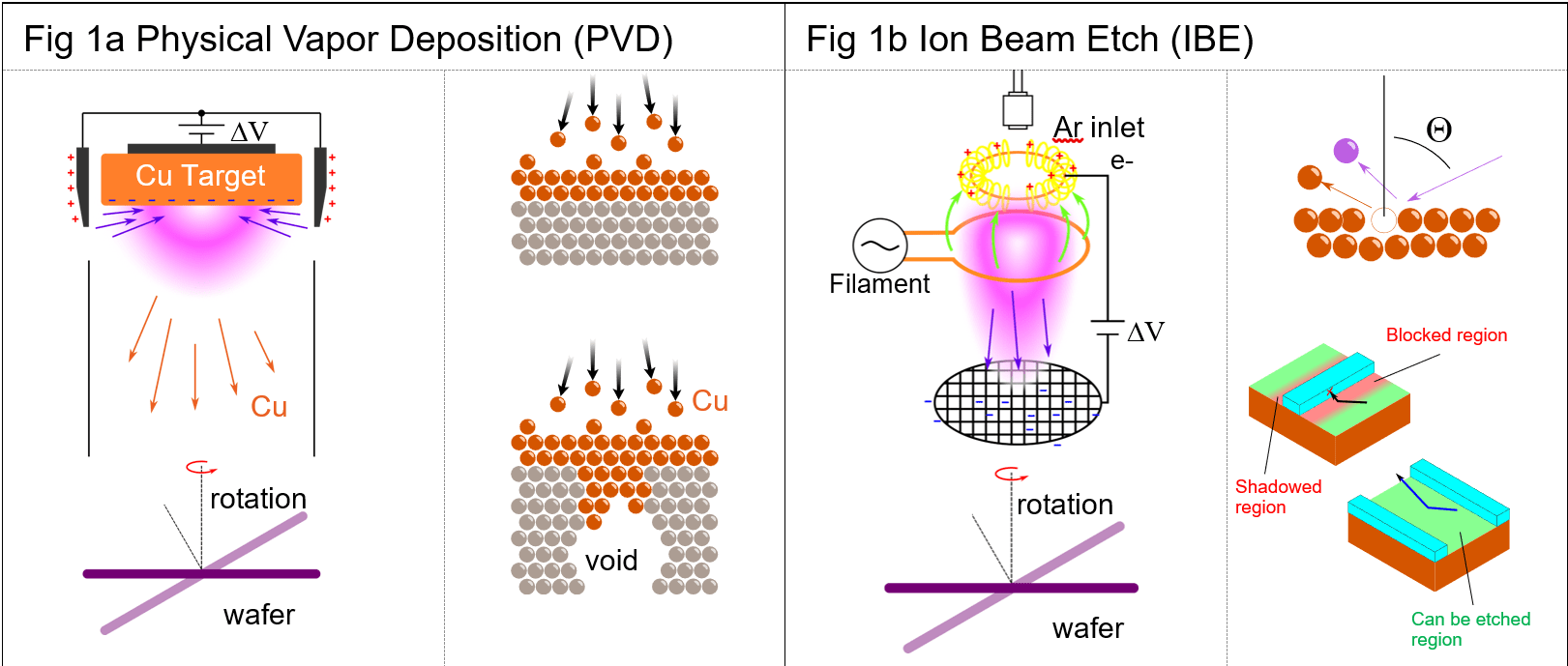

Durch physikalische Gasphasenabscheidung (PVD) kann Kupfer bei hohen kinetischen Energien (zwischen 10 und 100 eV) abgeschieden werden, wodurch dichte Einkristallstrukturen mit geringem Widerstand entstehen. Ein Nachteil von PVD besteht darin, dass die PVD-Abscheidung eine Streuung der Sichtlinie aufweist und nur gleichmäßig auf flachen Oberflächen abgeschieden werden kann. Es kann nicht zum Füllen von tiefen Löchern oder Gräben verwendet werden (Abbildung 1a). Um isolierte Drahtformen zu bilden, muss eine gleichmäßige Cu-Schicht auf einer flachen Oberfläche abgeschieden und dann durch Ionenstrahlen physikalisch geätzt werden. Cu bildet mit reaktiven Gasen keine flüchtigen Verbindungen, sodass ein reaktives Ionenätzverfahren nicht angewendet werden kann. Beschleunigte Ar-Ionen, die beim Ionenstrahlätzen (IBE) entstehen, können Cu entfernen, wenn der Einfallswinkel sehr groß ist. Leider sind die ätzbaren Bereiche aufgrund von Maskenschatteneffekten begrenzt. Abbildung 1b zeigt die Bereiche (in Rot), in denen kein Material geätzt werden kann, wenn die Maske senkrecht zum einfallenden Ionenstrahl steht. Dieser Ätzfehler tritt entweder aufgrund einer Abschattung oder einer Blockierung des Weges des ausgestoßenen Atoms auf. Wenn die Maske parallel zum Ionenweg verläuft, können alle unmaskierten Bereiche geätzt werden. Daher ist das Ionenstrahlätzen auf das Ätzen von linienförmigen Masken beliebig großer Länge beschränkt.

![]()

Abb. 1: (1a) Physical Vapour Deposition (PVD); (1b) Ionenstrahlätzen (IBE).

Prozessschritte und virtueller Fertigungsprozess

Um die Auswirkung von Abscheidung und Ätzung auf den Leitungswiderstand zu verstehen, modellieren wir nun die PVD- und IBE-Ätzprozesse mithilfe der SEMulator3D-Sichtbarkeitsabscheidungs- und Ätzfunktionen. PVD wurde mithilfe eines 30-Grad-Winkelspreizungs-Sichtbarkeitsabscheidungsprozesses in SEMulator3D reproduziert, der die zufällige Natur der ausgestoßenen Cu-Atome während des Beschusses mit AR-Ionen genau modelliert. IBE wurde im Modell mithilfe einer Sichtbarkeitsätzung mit einer Winkelausbreitung von 2 Grad und einer Polarwinkelneigung von 60 Grad reproduziert, um das Verhalten gitterbeschleunigter Ionen mit geringer Strahldivergenz widerzuspiegeln. Es wird davon ausgegangen, dass sich beide Wafer frei drehen können. Andere Prozessschritte wurden im virtuellen Fertigungsprozess angepasst, um IBE- und PVD-Einschränkungen zu berücksichtigen. Abbildung 2 zeigt die gleiche Struktur, die sowohl mit einer Damaszener-Cu-Füllung (Abbildung 2a) als auch mit einem PVD/IBE-Prozess (Abbildung 2b) erstellt wurde. Zusätzliche Prozessschritte wurden einbezogen, um bestimmte Einschränkungen von PVD/IBE zu berücksichtigen und die entsprechende Form für unsere gewünschten Endstrukturen zu schaffen.

![]()

Abb. 2: (2a) Damaszener-Füllung von Cu-Drähten; (2b) PVD/IBE-Cu-Drahtherstellung.

Anschließend zeigen wir, dass unter Einhaltung dieser Einschränkungen eine äquivalente 16-nm-SRAM-Schaltkreiszelle mit PVD/IBE-Drähten hergestellt werden kann. Da alle Metallschichten über dem mittleren Ende der Leitung aus einer flachen Oberfläche bestehen, ist sie im Gegensatz zu den komplexen Verbindungstopologien, die bei einem FinFET-Gerät zu sehen sind, ein idealer Kandidat für PVD/IBE-Drähte. Abbildung 3 zeigt die isolierte Struktur jeder Metallschicht und die notwendigen Schritte, die zum Erstellen einer FinFET-Struktur mit drei Metallschichten mithilfe von PVD/IBE erforderlich sind.

![]()

Abb. 3: (3a) 16 nm FinFET MEOL und 3 Metallschichten; (3b) Schrittweise Herstellung der Metallschicht mittels PVD/IBE.

Widerstandsergebnisse und Schlussfolgerung

Anschließend messen wir den elektrischen Widerstand der Drähte von der obersten Metallschicht bis zu den Durchkontaktierungen der P- und N-Kanäle des FinFET, sowohl für den Damascene-Fluss als auch für die physikalische Gasphasenabscheidung. Abbildung 4 zeigt den Start- und Endpunkt der Widerstandsmessung am P- und N-Kanal (alle anderen Isoliermaterialien sind transparent). Um den Grenzflächenwiderstand zwischen der TaN-Auskleidung und dem Kupferdraht zu kompensieren, wurde der spezifische Widerstand von Kupfer durch Verwendung einer exponentiellen Abfallkonstante von 1 nm als Funktion des nächsten Abstands zur TaN-Grenzfläche erhöht. Da bei einer Damaszenerfüllungs-Cu-Abscheidung nicht davon auszugehen ist, dass sie vollständig kristallin ist, wurde der spezifische Widerstand von Cu um 50 % erhöht. Der PVD/IBE-Kupferprozess verwendet keinen TaN-Liner, daher wurde die exponentielle Zerfallsfunktion nicht angewendet und in diesem Modell der Massenwiderstand von Kupfer verwendet. Eine Tabelle des spezifischen Widerstands, der einen Damaszener-Fluss mit PVD vergleicht, ist in Abbildung 4 enthalten.

![]()

Abb. 4: Startpunkt und Endpunkt der Widerstandsmessung am P- und N-Kanal.

Die anhand unseres Modells berechneten Widerstandswerte besagen, dass wir mit der IBE/PVD-Herstellungsmethode eine Reduzierung des Widerstands um 67 % im Vergleich zu einer herkömmlichen Grabenätzung mit anschließender Damaszener-Abscheidung erreichen können. Dies liegt daran, dass bei IBE/PVD kein TaN-Liner benötigt wird und während dieses Prozesses ein geringerer CU-Widerstand vorliegt. Unsere Ergebnisse deuten darauf hin, dass durch die Verwendung von IBE/PVD im Vergleich zur Damaszenerfüllung während der Bildung der Metallleitung Widerstandsverbesserungen erzielt werden können, allerdings auf Kosten eines komplexeren Herstellungsprozesses.

Timothy Yang

(alle Artikel)

Timothy Yang ist Softwareanwendungsingenieur bei Coventor, einem Lam-Forschungsunternehmen. Er ist in den Bereichen Prozessentwicklung, Integration und Ertragsverbesserungsanwendungen tätig und verfügt über Fachkenntnisse in Speichertechnologien. Vor seiner Tätigkeit bei Coventor arbeitete Yang bei Tokyo Electron an der Entwicklung von Ätzschemata, Techniken zur Postlithografie-Musterverbesserung, Prozessflusssteuerung für SADP- und SAQP-Strukturierungsanwendungen sowie EUV- und Immersionslithografie-Fotolacktechnologie. Yang erhielt seinen BS-Abschluss in Physik von der UCLA, einen MS-Abschluss in Materialwissenschaften vom Chiba Institute of Technology und einen Ph.D. Abschluss in Materialwissenschaften an der Universität Tohoku.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Quelle: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :hast

- :Ist

- ][P

- 1

- 10

- 100

- a

- oben

- beschleunigt

- unterbringen

- genau

- Erreichen

- erreicht

- Zusätzliche

- Bereinigt

- Alle

- Alle Beiträge

- und

- Angular

- Anwendungen

- angewandt

- AR

- SIND

- AS

- angenommen

- At

- Atom

- BE

- Strahl

- wird

- war

- zwischen

- Grenzen

- by

- berechnet

- CAN

- Kandidat

- kann keine

- sicher

- Kanäle

- Unternehmen

- verglichen

- Vergleich

- Komplex

- konstante

- Einschränkungen

- Smartgeräte App

- konventionellen

- Kupfer

- Kosten

- erstellen

- erstellt

- Kristall

- technische Daten

- verringern

- tief

- Grad

- zeigen

- hängt

- Einzahlungen

- hinterlegt

- erwünscht

- Entwicklung

- Entwicklung

- Gerät

- Rundfunk

- Displays

- Abstand

- Divergenz

- nach unten

- im

- jeder

- bewirken

- Effekten

- entweder

- Ingenieur

- Äquivalent

- EV

- erwartet

- Expertise

- exponentiell

- Scheitern

- Abbildung

- füllen

- Wohnung

- Fluss

- gefolgt

- Aussichten für

- unten stehende Formular

- Ausbildung

- Formen

- Frei

- für

- voll

- Funktion

- Funktionen

- Gitter

- Haben

- he

- GUTE

- hoch

- Bohrungen

- HTTPS

- Idee

- Eintauchen

- Verbesserung

- Verbesserungen

- in

- Zwischenfall

- inklusive

- Eingehende

- integrieren

- hat

- Steigert

- zeigen

- Institut

- Integration

- Schnittstelle

- isoliert

- IT

- SEINE

- jpg

- Lam

- Schicht

- Lagen

- Einschränkungen

- Limitiert

- Line

- Linien

- Lang

- Sneaker

- MACHT

- Maske"

- Masken

- Ihres Materials

- Materialien

- max-width

- messen

- Memory

- Metall

- Methode

- Mitte

- Modell

- für

- mehr

- Natur

- notwendig,

- erforderlich

- of

- on

- Auftrag

- Andere

- UNSERE

- Parallel

- Weg

- Schnittmuster

- physikalisch

- Physisch

- Physik

- Plato

- Datenintelligenz von Plato

- PlatoData

- Points

- polar

- Post

- BLOG-POSTS

- verhindern

- Vor

- Prozessdefinierung

- anpassen

- zufällig

- Received

- Rot

- reflektieren

- Regionen

- entfernen

- Forschungsprojekte

- Robustes Design

- Die Ergebnisse

- s

- gleich

- Waage

- Regelungen

- Wissenschaft

- Halbleiter

- Form

- geformt

- Formen

- Konzerte

- Sehenswürdigkeit

- signifikant

- Silizium

- da

- Single

- kleinere

- So

- Software

- Verbreitung

- Beginnen Sie

- Bundesstaat

- Schritt

- Shritte

- Struktur

- Anschließend

- Oberfläche

- Tabelle

- Techniken

- Technologies

- Technologie

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Diese

- nach drei

- Daumennagel

- zu

- Tokio

- oberste

- traditionell

- transparent

- ucla

- verstehen

- Universität

- -

- benutzt

- seit

- Werte

- Assistent

- Sichtbarkeit

- flüchtig

- Volumen

- vs

- welche

- während

- werden wir

- Schweißdraht

- mit

- Arbeiten

- gearbeitet

- Werk

- Ausbeute

- Zephyrnet