Nó đã quay lại 1991 rằng Cadence lần đầu tiên công bố tên sản phẩm Virtuoso, và chúng ta ở đây sau 32 năm và sản phẩm vẫn tồn tại và hoạt động khá tốt. Steven Lewis từ Cadence đã cập nhật cho tôi về một điều mới mà họ gọi là Studio điêu luyệnvà tất cả đều là về thiết kế vi mạch tùy chỉnh cho thế giới thực. Trong 32 năm đó, chúng ta đã chứng kiến quá trình bán dẫn đi theo Định luật Moore từ 600nm bằng cách sử dụng CMOS phẳng, thu nhỏ xuống kỷ nguyên FinFET dưới 22 nm, đạt GAA ở nút 3nm. Rõ ràng nhu cầu về công cụ EDA đã thay đổi khi các nút nhỏ hơn mang lại các hiệu ứng vật lý mới cần được mô hình hóa và mô phỏng để đảm bảo thành công silicon đầu tiên.

Trọng tâm của Cadence Virtuoso Studio là giúp các nhà thiết kế vi mạch đương đầu với những thách thức ngày nay thông qua sáu lĩnh vực:

- Tăng độ phức tạp của quy trình

- Xử lý 10,000 mô phỏng mạch

- Tự động hóa thiết kế và di chuyển mạch

- Tích hợp không đồng nhất

- AI

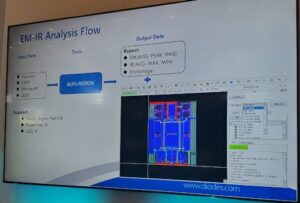

- Đăng xuất, xác minh và phân tích trong thiết kế

Sản phẩm ADE điêu luyện (Môi trường thiết kế tương tự) cho phép các kỹ sư mạch khám phá các thiết kế tương tự, tín hiệu hỗn hợp và RFIC của họ thông qua việc chụp sơ đồ và mô phỏng mạch. Kiến trúc của Virtuoso ADE đã được cải tiến để kiểm soát công việc tốt hơn, giảm mức sử dụng RAM và tăng tốc mô phỏng bằng cách sử dụng đám mây. Ví dụ: RAM cần thiết để chạy Spectre trên 10,000 mô phỏng đã giảm từ 420 MB xuống chỉ còn 18 MB để theo dõi mô phỏng, trong khi đánh giá biểu thức giảm từ 420 MB RAM xuống chỉ còn 280 MB.

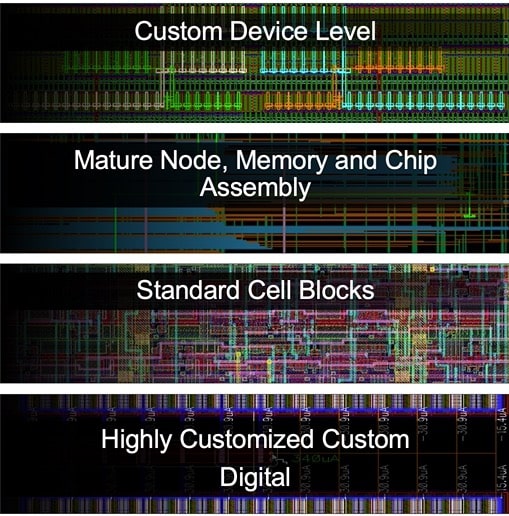

Cập nhật cho Bộ bố cục điêu luyện bao gồm bốn lựa chọn về công nghệ địa điểm và tuyến đường, mỗi lựa chọn phù hợp với nhiệm vụ riêng biệt thông qua môi trường Virtuoso:

Bốn công nghệ P&R

Các lần chạy DRC và LVS là một phần của quá trình xác minh vật lý và việc chạy chúng ở chế độ hàng loạt, sửa chữa và lặp lại, dẫn đến lịch trình phát triển dài. Xác minh trong thiết kế cho phép sử dụng tương tác DRC và LVS trong khi làm việc trên bố cục vi mạch, do đó, phản hồi về những gì cần thay đổi sẽ nhanh chóng được nêu rõ, tăng tốc năng suất. Nhà thiết kế bố cục sử dụng Virtuoso Layout Suite được hưởng lợi từ việc xác minh trong thiết kế bằng cách sử dụng Pegasus Công nghệ DRC và LVS.

Chiplets, bao bì 2.5D và 3D trải rộng trên các lĩnh vực truyền thống riêng biệt của lĩnh vực thiết kế PCB, gói và vi mạch. Virtuoso Studio cho phép đồng thiết kế và xác minh các gói, mô-đun và IC bằng cách:

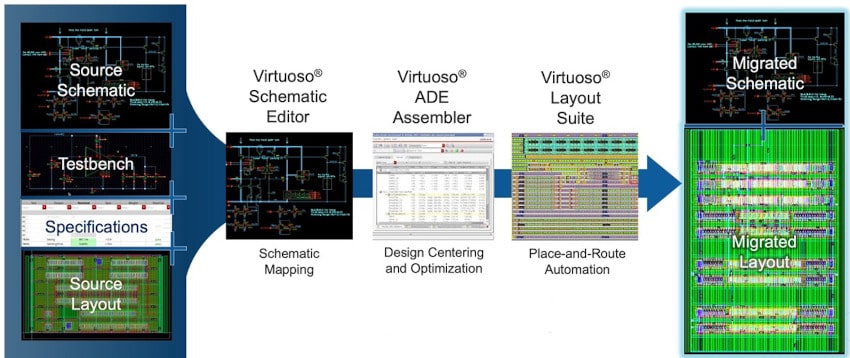

Nhìn về tương lai gần, bạn có thể mong đợi được thấy thông tin chi tiết về cách AI đang được áp dụng để tự động chuyển từ sơ đồ tương tự sang bố cục dựa trên thông số kỹ thuật và học máy. Những bố cục thử nghiệm được tạo tự động này sẽ tiếp tục đẩy nhanh quá trình sử dụng nhiều lao động. Lĩnh vực phát triển thứ hai để áp dụng AI là vấn đề di chuyển IP analog tùy chỉnh sang nút quy trình mới. Giữ nguyên.

Những khách hàng đầu tiên của Virtuoso Studio bao gồm Analog Devices để đồng thiết kế vi mạch và gói, các thiết kế vi mạch tiêu dùng hàng đầu tại MediaTek và quá trình di chuyển quy trình dựa trên AI tại Renesas.

Tổng kết

Virtuoso Studio đã đưa ra phiên bản 23.1 một số tính năng mới ấn tượng mà nhóm thiết kế vi mạch có thể bắt đầu sử dụng để làm việc hiệu quả hơn. Cơ sở hạ tầng Virtuoso đã thay đổi để đáp ứng những thách thức của Định luật Moore, mô phỏng với mô phỏng mạch 10,000 giây là thực tế, RFIC và đồng thiết kế mô-đun 2.5D/3D được hỗ trợ, xác minh DRC/LVS trong thiết kế mất ít thời gian hơn nhiều và AI đang được áp dụng để tự động hóa các tác vụ tương tự.

Blog liên quan

Chia sẻ bài đăng này qua:- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- : có

- :là

- $ LÊN

- 1

- 10

- 3d

- a

- Giới thiệu

- tăng tốc

- AI

- Tất cả

- cho phép

- dọc theo

- và

- công bố

- áp dụng

- kiến trúc

- LÀ

- KHU VỰC

- khu vực

- AS

- At

- tự động hóa

- tự động

- Tự động hóa

- trở lại

- dựa

- BE

- được

- được

- phía dưới

- Lợi ích

- Hơn

- Mang lại

- by

- Nhịp

- cuộc gọi

- CAN

- nắm bắt

- thách thức

- thay đổi

- lựa chọn

- Rõ ràng

- đám mây

- người tiêu dùng

- điều khiển

- khách hàng

- khách hàng

- ngày

- nhu cầu

- Thiết kế

- nhà thiết kế

- thiết kế

- thiết kế

- chi tiết

- Phát triển

- Thiết bị (Devices)

- làm

- lĩnh vực

- xuống

- mỗi

- hiệu ứng

- cho phép

- Kỹ sư

- đảm bảo

- Môi trường

- Kỷ nguyên

- đánh giá

- ví dụ

- mong đợi

- khám phá

- Tính năng

- thông tin phản hồi

- Tên

- Tập trung

- Trong

- 4

- từ

- xa hơn

- tương lai

- Go

- tay

- Có

- giúp đỡ

- tại đây

- Nhấn mạnh

- Độ đáng tin của

- HTML

- HTTPS

- ICS

- ấn tượng

- in

- bao gồm

- Cơ sở hạ tầng

- tương tác

- IP

- Việc làm

- jpg

- nhân công

- Luật

- Bố trí

- Dẫn

- học tập

- Đồ dùng móc đá lên cao

- dài

- máy

- học máy

- Tháng Ba

- max-width

- Gặp gỡ

- di cư

- Chế độ

- mô-đun

- Modules

- giám sát

- chi tiết

- tên

- Gần

- cần thiết

- Mới

- Các tính năng mới

- nút

- các nút

- of

- on

- ONE

- gói

- gói

- bao bì

- một phần

- vật lý

- Nơi

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Bài đăng

- Thực tế

- trình bày

- Vấn đề

- quá trình

- Sản phẩm

- sản xuất

- năng suất

- đặt

- Mau

- RAM

- đạt

- thực

- thế giới thực

- Giảm

- giảm

- phát hành

- cần phải

- Route

- chạy

- chạy

- mở rộng quy mô

- Thứ hai

- xem chi tiết

- bán dẫn

- riêng biệt

- Silicon

- mô phỏng

- Six

- nhỏ hơn

- So

- một số

- một cái gì đó

- nhịp cầu

- thông số kỹ thuật

- Quang phổ

- tốc độ

- Bắt đầu

- ở lại

- phòng thu

- thành công

- bộ

- Hỗ trợ

- Hãy

- mất

- Nhiệm vụ

- nhiệm vụ

- đội

- Công nghệ

- việc này

- Sản phẩm

- cung cấp their dịch

- Kia là

- Thông qua

- thời gian

- đến

- công cụ

- theo truyền thống

- thử nghiệm

- độc đáo

- Cập nhật

- Sử dụng

- sử dụng

- Xác minh

- thông qua

- TỐT

- Điều gì

- trong khi

- sẽ

- với

- đang làm việc

- thế giới

- năm

- zephyrnet