Hội nghị in thạch bản nâng cao SPIE được tổ chức vào tháng Hai. Gần đây tôi đã có cơ hội phỏng vấn Steven Scheer, phó chủ tịch về quy trình và vật liệu tạo mẫu nâng cao tại imec và xem xét các bài báo được chọn lọc mà imec đã trình bày.

Tôi đã hỏi Steve thông điệp bao trùm tại SPIE năm nay là gì, anh ấy nói rằng sự sẵn sàng cho NA cao là chìa khóa. Ông đã xác định ba khu vực hệ sinh thái chính:

- Cơ sở hạ tầng Công nghệ tăng cường độ phân giải và mặt nạ (RET).

- Vật liệu, chất cản quang và lớp lót.

- Đo lường

Tất nhiên, các công cụ phơi sáng cũng rất quan trọng, nhưng đó không phải là điều mà Steve nói đến. Lưu ý của các tác giả - Tôi cũng sẽ viết bài về các bài thuyết trình SPIE của ASML.

Mặt nạ

Steve tiếp tục liệt kê các vấn đề liên quan đến mặt nạ:

- Che các hiệu ứng 3d, chẳng hạn như thay đổi tiêu điểm và mất độ tương phản – NA cao là độ phơi sáng góc thấp khiến hiệu ứng 3D trở thành một vấn đề.

- Mặt nạ có khuyết tật thấp và mặt nạ có độ biến thiên thấp về độ nhám và CD

- Cần có mặt nạ Low-n để kích hoạt độ tương phản cao hơn và giảm hiệu ứng mặt nạ 3D.

- Kỹ thuật hiệu chỉnh tiệm cận quang học.

- Mặt nạ viết, đa tia.

- Khâu mặt nạ – kích thước nhỏ hơn của trường máy quét yêu cầu các khuôn đó được khâu lại với nhau.

- 4x một hướng, 8x hướng khác yêu cầu một loại thiết kế mặt nạ mới để kích hoạt đường may.

- Pellets cho nguồn năng lượng cao hơn.

In “Các hạt CNT: Các kết quả tiếp xúc và tối ưu hóa gần đây,” Joost Bekaert et.al., khám phá hạt ống nano cacbon (CNT).

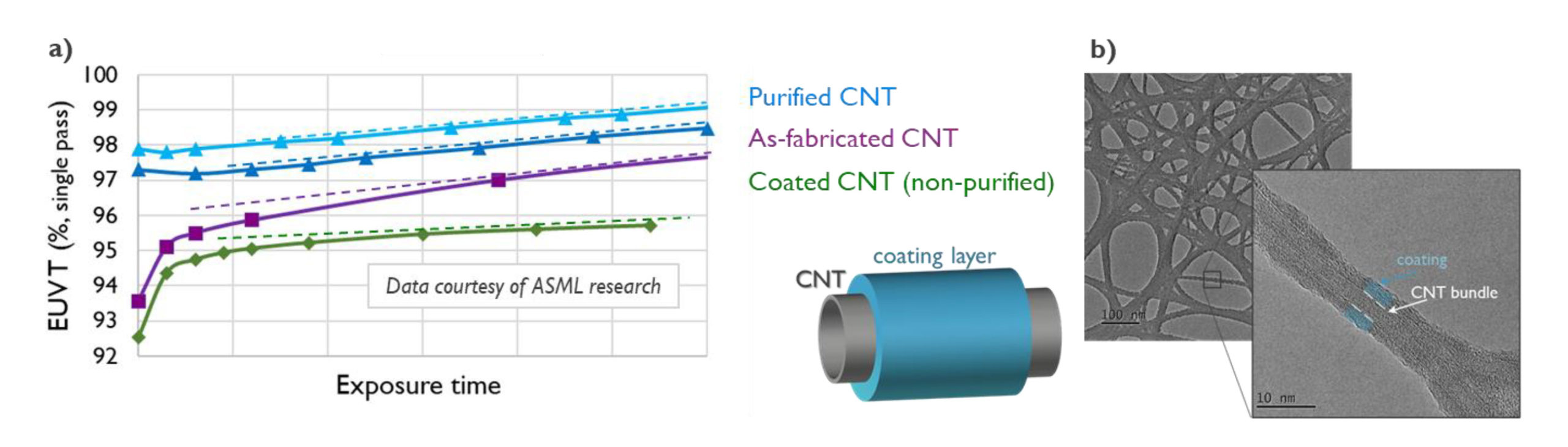

ASML có các hệ thống nguồn 600 watt trên lộ trình của họ, các hạt hiện tại dựa trên chất diệt khuẩn kim loại chỉ khả thi ở mức xấp xỉ 400 watt. Các hạt cần phải chặn các hạt, có khả năng truyền tải cao, đủ độ bền cơ học để lơ lửng trên diện tích khoảng 110mm x 140mm và bền. CNT đã cho thấy khả năng truyền dẫn lên tới 98%. Bức xạ EUV mạnh đến mức nó tạo ra một plasma hydro ăn mòn hạt, cuối cùng dẫn đến sự mất tính toàn vẹn cơ học của hạt. imec đã và đang đánh giá tốc độ ăn mòn và cách ổn định hạt.

Tốc độ ăn mòn có thể được đánh giá bằng cách xem xét quá trình truyền, vì Hạt được làm mỏng bằng quá trình ăn mòn, quá trình truyền tăng lên. Hình 1 minh họa quá trình truyền tải theo thời gian của một Hạt chịu các điều kiện khác nhau.

ASML đánh giá quá trình truyền hạt so với thời gian phơi sáng bằng cách sử dụng công cụ phơi nhiễm plasma ngoại tuyến và trong nghiên cứu này, imec đã chứng minh mức độ tiếp xúc của hạt CNT lên tới 3,000 tấm wafer (96 khuôn ở 30 mJ/cm² mỗi tấm wafer) và cho thấy mối tương quan giữa các kết quả thu được từ quá trình phơi sáng máy quét thực tế và những thứ từ công cụ ngoại tuyến.

Viên ban đầu có các tạp chất hữu cơ dễ bay hơi từ quá trình sản xuất hấp thụ năng lượng EUV cho đến khi chúng cháy hết, nhìn thấy các đường cong màu xanh lục và tím. Nướng viên ở nhiệt độ cao “làm sạch” viên bằng cách đốt cháy các chất gây ô nhiễm dẫn đến thay đổi tốc độ ăn mòn chi phối quá trình truyền. Độ dốc của hai đường cong màu xanh là do tốc độ ăn mòn. Đường cong màu lục minh họa một hạt “được phủ” thể hiện tốc độ ăn mòn thấp hơn, tuy nhiên, lớp phủ làm giảm khả năng truyền tải và có thể không tương thích với các mức công suất rất cao.

Thợ chụp ảnh

Steve, sau đó thảo luận về chất cản quang.

Đối với chất cản quang, bước sóng từ 24nm đến 20nm là điểm lý tưởng để chèn NA cao với bước sóng 16nm là độ phân giải cuối cùng. Điện trở khuếch đại hóa học (CAR) có hiệu suất kém dưới 24nm. Metal Oxide Resists (MOR) có vẻ đầy hứa hẹn xuống tới 17nm hoặc thậm chí 16nm. Khiếm khuyết vẫn là một vấn đề. Liều ở bước 24nm là 67mJ/cm2 cho MOR và 77mJ/cm2 cho ô tô. MOR có một số vấn đề về độ ổn định và liều lượng càng thấp thì khả năng phản ứng càng cao/kém ổn định hơn. Đây là những thách thức, không phải showstoppers.

In “Các lớp lót lắng đọng được thu nhỏ lại để in thạch bản EUV,” Gupta et.al., đã khám phá các lớp lót cản quang. Khi cao độ bị thu hẹp, đối với cùng một lớp cản quang, tỷ lệ khung hình sẽ tăng lên và có thể dẫn đến sự sụp đổ của mẫu. Cải thiện độ bám dính của lớp lót có thể giải quyết vấn đề này. Ngoài ra, một chất cản quang mỏng hơn có thể được sử dụng để quản lý tỷ lệ khung hình nhưng điều này có thể dẫn đến các vấn đề ăn mòn trừ khi có thể tìm thấy độ chọn lọc ăn mòn cao dưới lớp.

imec đã phát hiện ra rằng năng lượng bề mặt của các lớp bên dưới lắng đọng có thể phù hợp với chất cản quang để đạt được độ bám dính được cải thiện. Điều chỉnh mật độ của lớp dưới lắng đọng có thể được sử dụng để cung cấp tính chọn lọc ăn mòn được cải thiện.

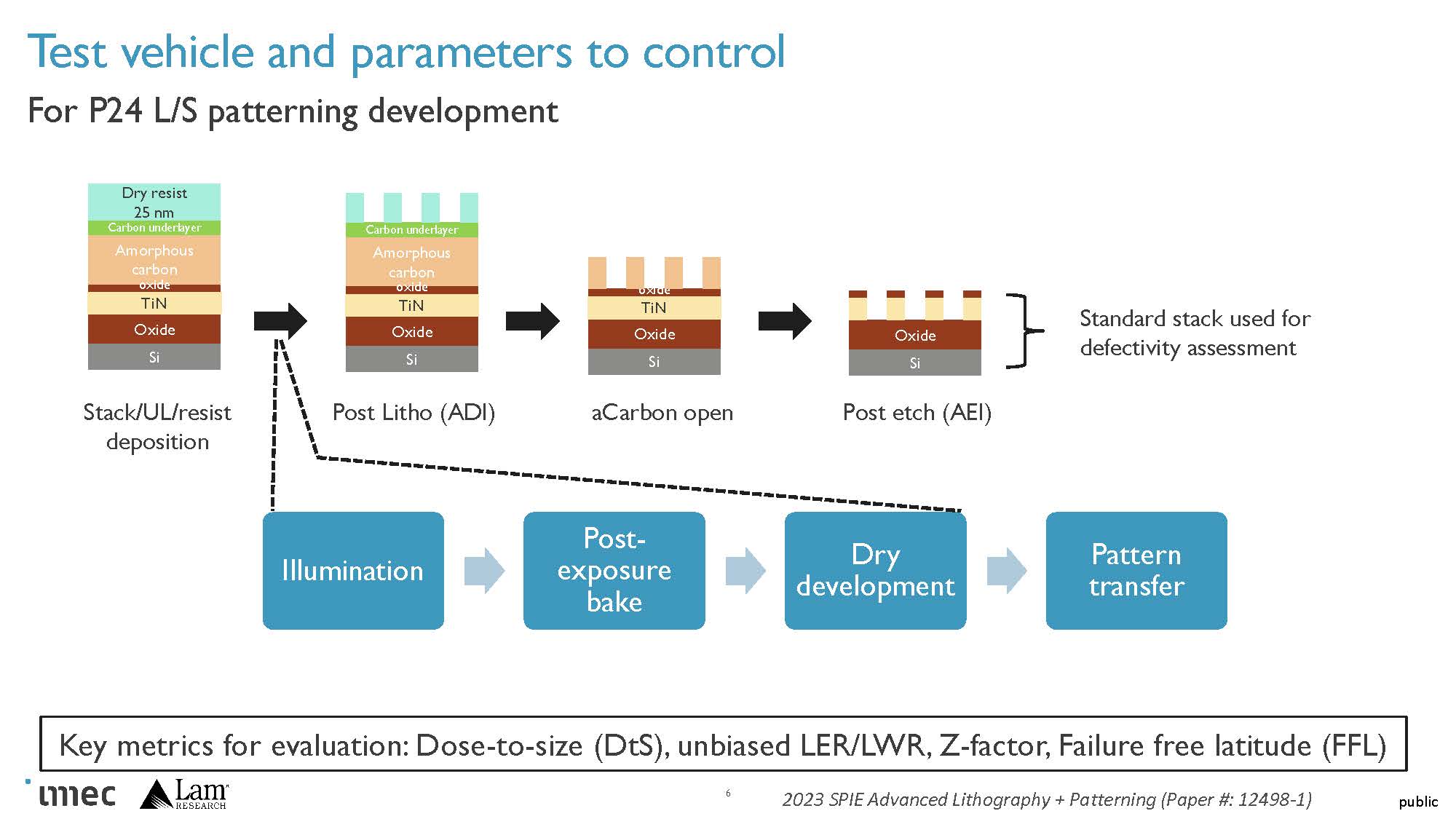

In “Sẵn sàng tạo mẫu kháng khô đối với kỹ thuật in thạch bản NA EUV cao,” Hyo Sean Suh et.al., từ imec và Lam đã khám phá quy trình chất cản quang khô của Lam. Đối với các quy trình N2+ và A14, bước kim loại 2 (M2P) dự kiến sẽ là ~24nm với 15nm từ đầu đến cuối (T2T) và sau đó ở A10 M2P sẽ là ~22nm với <15nm T2T.

Quá trình điện trở khô Lam được minh họa trong hình 2.

Post Exposure Bake (PEB) đã được tìm thấy để thúc đẩy mạnh mẽ việc giảm liều lượng nhưng ảnh hưởng đến cầu và độ nhám. Đồng tối ưu hóa quá trình phát triển và khắc giảm thiểu cầu nối và độ nhám, đồng thời cho thấy một cửa sổ quy trình mạnh mẽ để tạo khuôn L/S bước 24nm.

In “Tính khả thi của việc chia tỷ lệ kim loại logic với khuôn đơn 0.55NA EUV,” Dongbo Xu et.al. đã mô tả một đánh giá về những gì hệ thống NA cao (0.55NA) có thể đạt được với việc tạo mẫu đơn lẻ.

Họ kết luận rằng có thể đạt được bước tiến 24nm. 20nm có vẻ đầy hứa hẹn theo hướng ngang nhưng hướng dọc cần nhiều công việc hơn. Sân 18nm cần làm việc bổ sung.

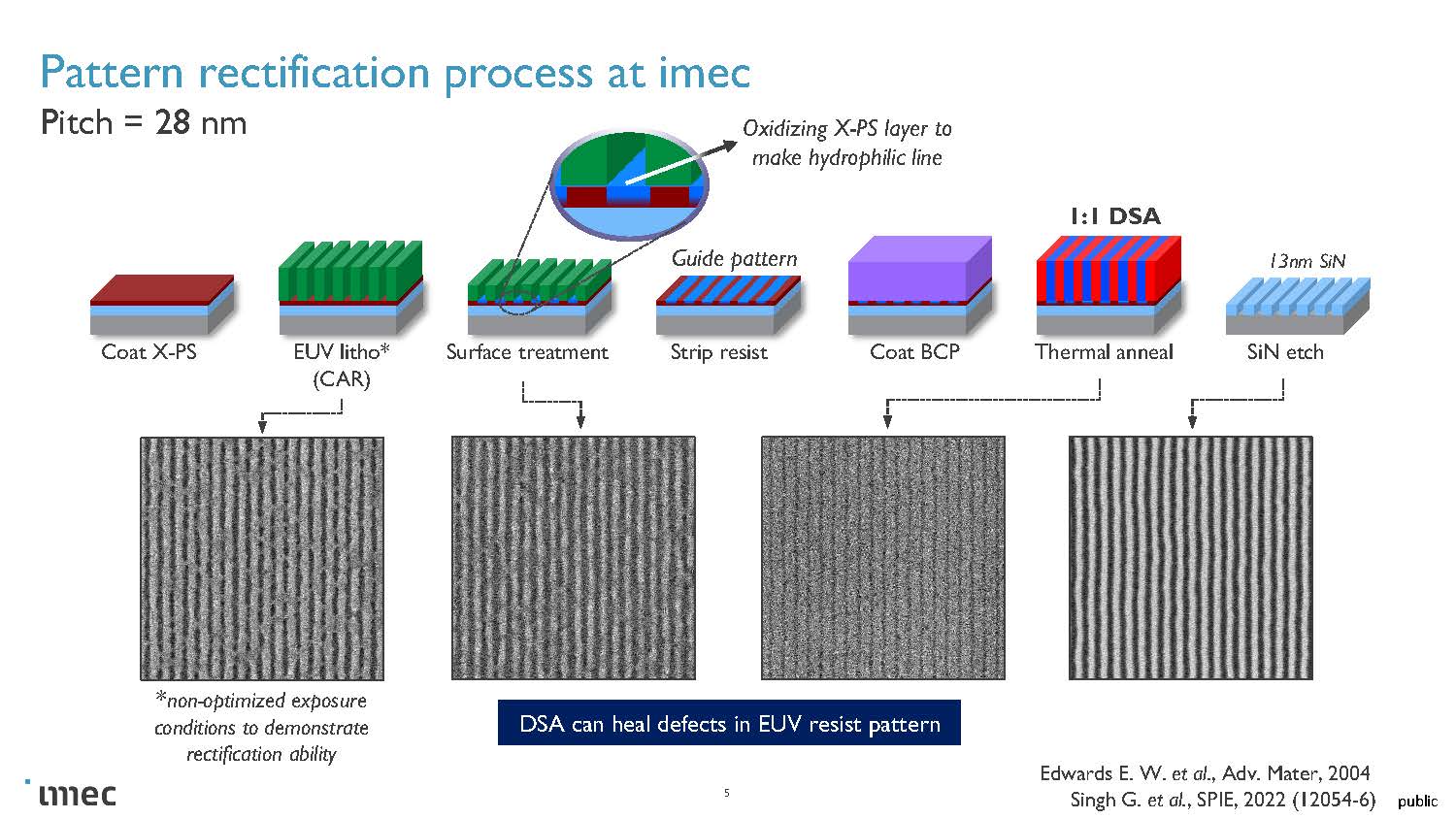

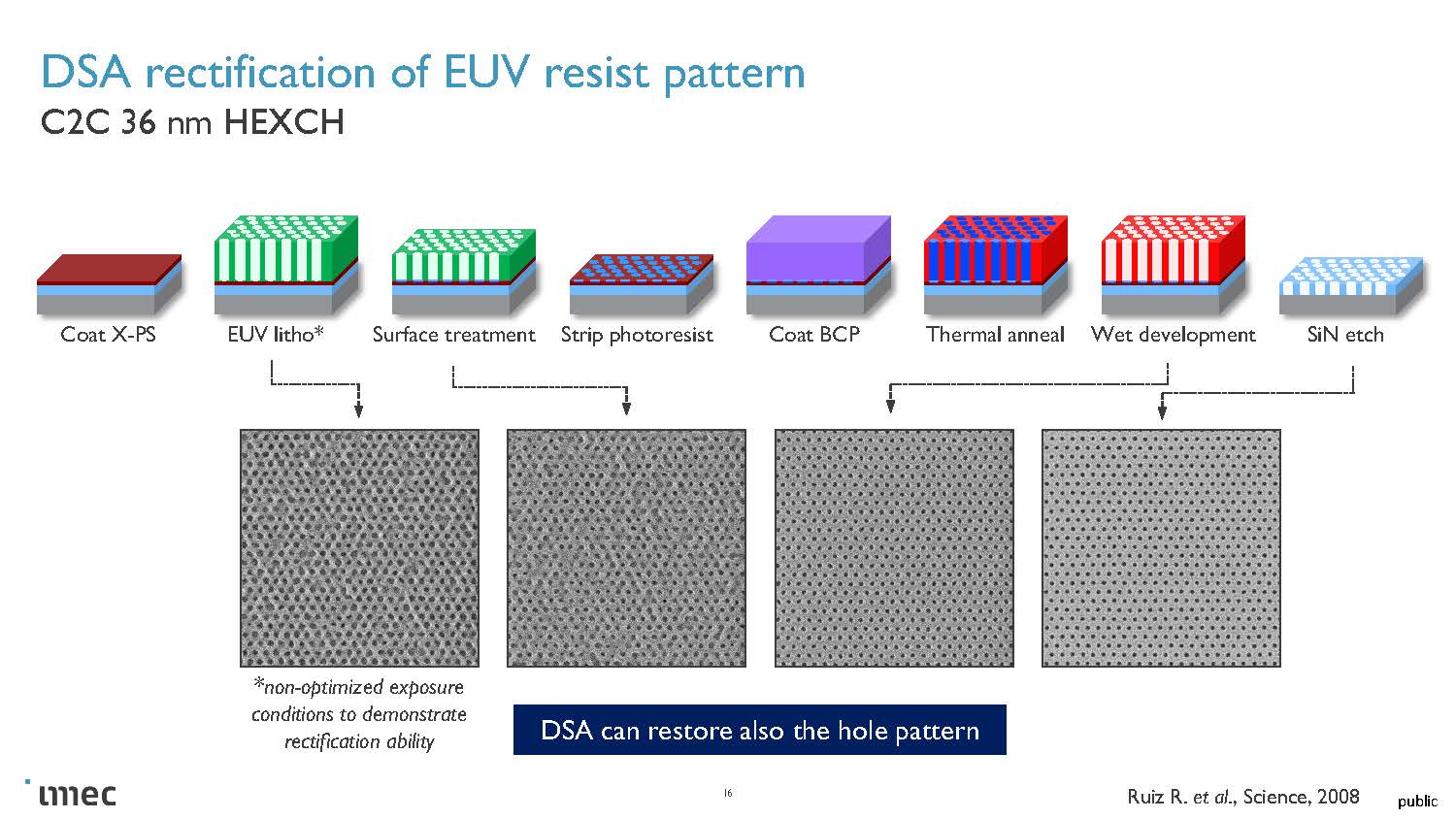

EUV đã được chứng minh là một công nghệ rất thách thức từ góc độ độ nhám của Đường và khuyết tật ngẫu nhiên. Directed Self Assembly (DSA) là một công nghệ đã xuất hiện từ lâu nhưng không thu hút được nhiều sự chú ý. DSA hiện đang được chú ý như một kỹ thuật để giải quyết các khuyết tật về độ nhám của đường và ngẫu nhiên cho EUV.

In “CHUẨN CHỈNH MẪU KHÔNG GIAN DÒNG EUV LITHOGRAPHY SỬ DỤNG BLOCK COPOLYMER TỰ LẮP RÁP TRỰC TIẾP: Một nghiên cứu về độ nhám và khuyết tật,” Julie Van Bel et.al. nhận thấy rằng việc kết hợp DSA với EUV vượt trội hơn so với các quy trình DSA dựa trên kỹ thuật in chìm với độ nhám của chiều rộng đường kẻ thấp hơn và không có khuyết tật về trật khớp.

In “Giảm thiểu ngẫu nhiên trong in thạch bản EUV bằng phương pháp tự lắp ráp có chỉ đạo,” Lander Verstraete et.al. đã khám phá bằng cách sử dụng DSA để giảm thiểu các khiếm khuyết ngẫu nhiên trong quá trình xử lý EUV.

Quy trình imec để khắc phục các lỗi EUV dòng/khoảng cách được minh họa trong hình 3.

Quy trình imec để khắc phục các lỗi trong mảng tiếp xúc được minh họa trong hình 4.

EUV cộng với DSA có vẻ rất hứa hẹn cho dòng/khoảng cách ở bước 28nm với khuyết điểm chính là cầu nối. Ở bước cải tiến 24nm là cần thiết với quá nhiều lỗi cầu nối. Các khuyết tật tương quan với công thức copolyme khối và thời gian ủ.

Đối với các mảng tiếp xúc, EUV + DSA cải thiện Tính đồng nhất Kích thước Tới hạn Cục bộ (LCDU) và Lỗi Vị trí Mẫu, đồng thời cho phép sử dụng liều thấp hơn.

Đo lường

Khi độ dày màng giảm, tín hiệu đo lường tỷ lệ nhiễu trở thành một vấn đề.

Với EUV, có một cửa sổ quy trình xử lý lỗi, ở một bên có một vách đá trong đó các lỗi trong mẫu trở thành một vấn đề và ở phía bên kia của các cửa sổ có một vách đá trong đó các cầu nối giữa các mẫu trở thành một vấn đề.

Khi thử một sân mới, có rất nhiều lỗi sẽ giảm dần theo thời gian.

Thật khó để đo một khu vực đủ lớn với đủ độ nhạy. E beam check nhạy nhưng chậm, soi quang nhanh nhưng không nhạy. Các quy trình 3D mới như CFET đưa ra các thách thức bổ sung.

In “Khả năng sẵn sàng đo lường kháng khô đối với EUVL NA cao,” Gian Francesco Lorusso et.al, điều tra Kính hiển vi lực nguyên tử (AFM), kiểm tra E Beam và CD SEM để mô tả đặc tính của các chất cản quang rất mỏng.

Sử dụng quy trình chất cản quang khô Lam<CD SEM đã được chứng minh là khả thi với chất cản quang dày 5nm. Khi độ dày điện trở giảm độ nhám của đường tăng, khả năng in các khuyết tật của cầu giảm trong khi các khuyết tật gãy vẫn giữ nguyên. Sự sụp đổ mô hình chỉ được nhìn thấy trong các bộ phim dày hơn. Các phép đo AFM cho thấy độ dày màng giảm. E Beam cho thấy khả năng bắt lỗi tốt ngay cả đối với những bộ phim rất vật chất.

In “Đo lường chất bán dẫn cho kỷ nguyên 3D,” J. Bogdanowicz et.al., khám phá những thách thức của đo lường trên cấu trúc 3D.

Trong kỷ nguyên 3D, hướng Z đã trở thành tỷ lệ X/Y mới. Đối với các thiết bị logic, CFET và Semi damascene đưa ra các thách thức, trong bộ nhớ 3D DRAM là một thách thức trong tương lai và các kết nối 3D cho Công nghệ Hệ thống Tối ưu hóa (STCO) là một thách thức khác.

Đối với các quy trình Nanosheet ngang và CFET, việc mô tả đặc điểm và lấp đầy phần lõm bên và phát hiện dư lượng cũng như các khiếm khuyết khác trong các ngăn xếp nhiều lớp sẽ rất quan trọng. Trong Bộ nhớ 3D, việc lập cấu hình lỗ/tách có tỷ lệ khung hình cao (HAR) và tương tự như logic phát hiện các khuyết tật và cặn bị chôn vùi trong phim nhiều lớp sẽ rất quan trọng. Đối với các ứng dụng STCO, tính toàn vẹn của các giao diện liên kết và căn chỉnh sẽ là chìa khóa.

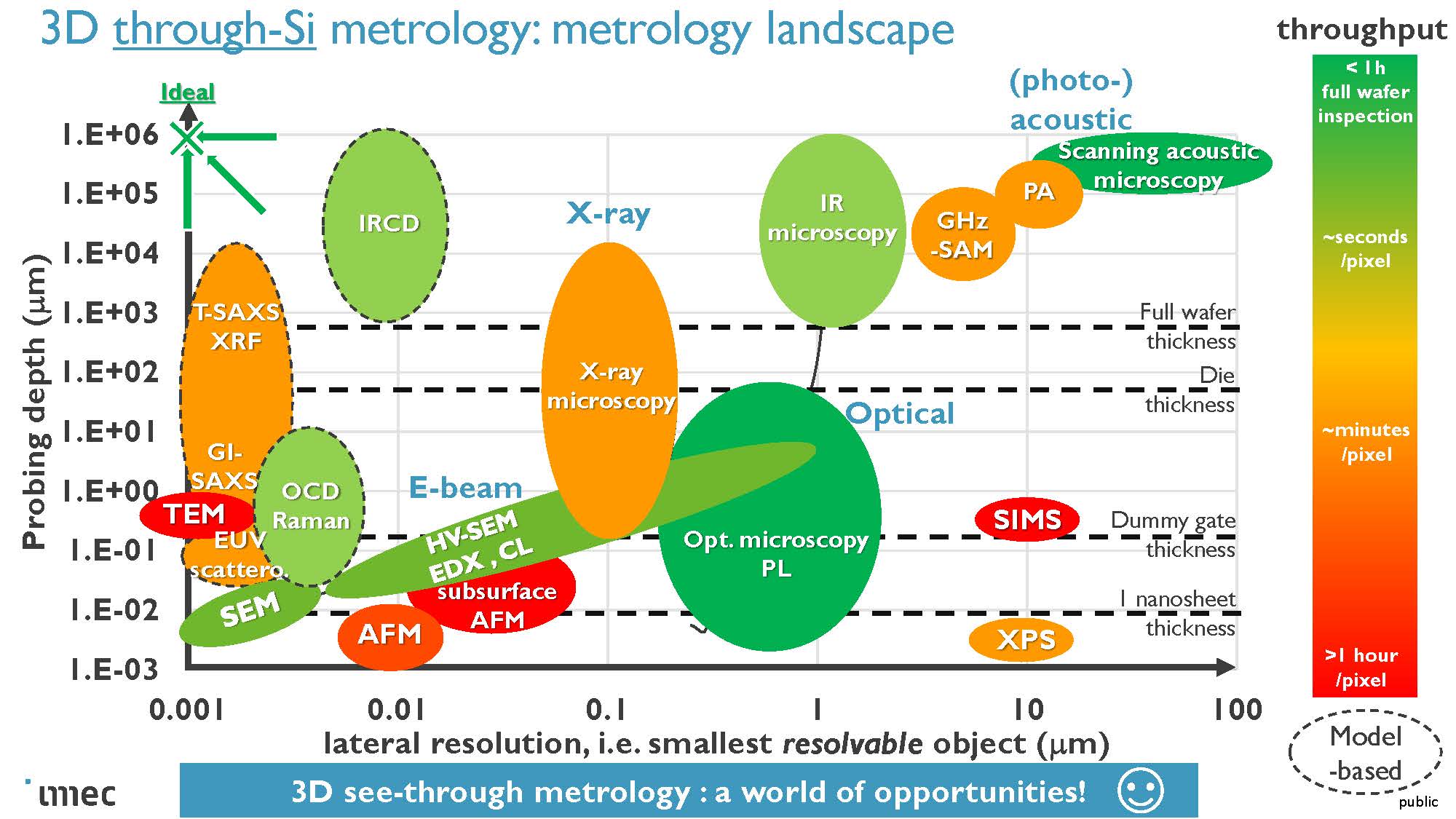

Đối với phép đo bề mặt truyền thống, đã có sự đánh đổi giữa độ nhạy và tốc độ, giờ đây độ sâu kiểm tra so với độ phân giải ngang là một sự đánh đổi quan trọng. Hình 5 trình bày độ sâu thăm dò so với độ phân giải bên và thông lượng cho các kỹ thuật đo lường khác nhau.

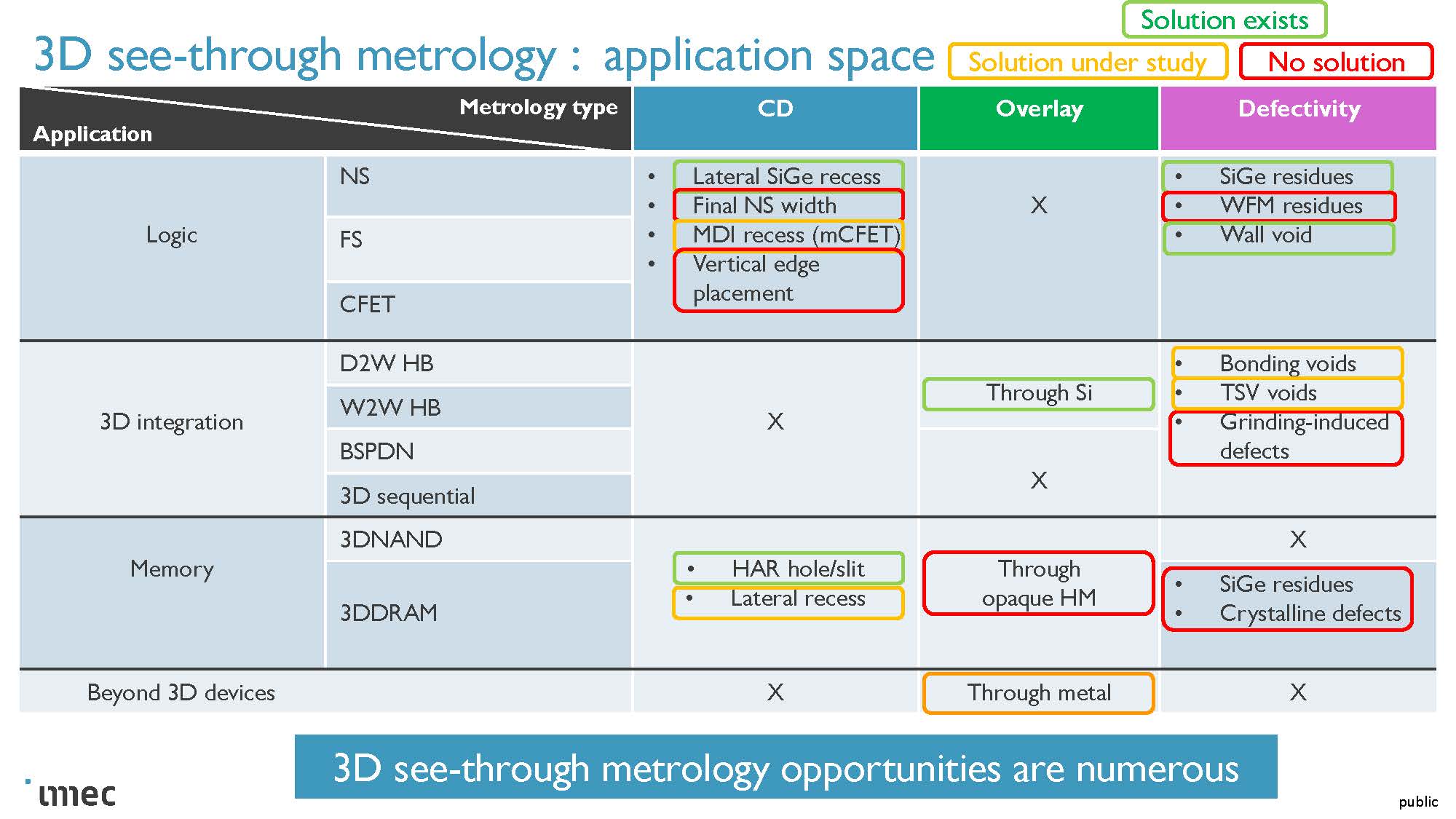

Hình 6 tóm tắt mức độ sẵn sàng hiện tại của đo lường 3D để giải quyết các nhu cầu khác nhau.

Từ hình 6, vẫn còn rất nhiều thách thức phải vượt qua để đạt được một chương trình đo lường toàn diện.

Kết luận

Thời đại của NA EUV cao đang đến gần. Có những tiến bộ tốt đang được thực hiện trong hạt, chất cản quang và đo lường và imec tiếp tục hoạt động trong cả ba lĩnh vực để đạt được những tiến bộ hơn nữa.

Cũng đọc:

TSMC đã chi nhiều tiền hơn cho 300mm so với bạn nghĩ

SPIE Advanced Lithography Conference 2023 – Thông báo của AMAT Sculpta®

IEDM 2023 – Vật liệu 2D – Intel và TSMC

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- Mua và bán cổ phần trong các công ty PRE-IPO với PREIPO®. Truy cập Tại đây.

- nguồn: https://semiwiki.com/lithography/329278-spie-2023-imec-preparing-for-high-na-euv/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 000

- 1

- 2022

- 2023

- 2D

- Vật liệu 2D

- 30

- 3d

- a

- Đạt được

- thực tế

- thêm vào

- địa chỉ

- tiên tiến

- kỹ thuật in thạch bản nâng cao

- AL

- Tất cả

- Đã

- Ngoài ra

- Khuếch đại

- an

- và

- Một

- các ứng dụng

- tiếp cận

- khoảng

- LÀ

- KHU VỰC

- khu vực

- xung quanh

- AS

- khía cạnh

- hợp ngữ

- At

- đã cố gắng

- sự chú ý

- tác giả

- nướng bánh

- dựa

- BE

- Chùm tia

- trở nên

- được

- được

- phía dưới

- giữa

- Chặn

- Màu xanh da trời

- Nghỉ giải lao

- nghỉ giải lao

- CẦU

- cầu

- ghi

- nhưng

- by

- CAN

- nắm bắt

- xe hơi

- carbon

- CD

- thách thức

- thách thức

- thách thức

- Những thay đổi

- CO

- Sự sụp đổ

- kết hợp

- tương thích

- toàn diện

- kết luận

- điều kiện

- Hội nghị

- liên lạc

- chất gây ô nhiễm

- liên tiếp

- Ngược lại

- Tương quan

- khóa học mơ ước

- tạo ra

- quan trọng

- Current

- đường cong

- giảm

- chứng minh

- mật độ

- ký gửi

- chiều sâu

- mô tả

- Thiết kế

- Phát triển

- Thiết bị (Devices)

- Die

- kích thước

- hướng

- thảo luận

- trật khớp

- làm

- xuống

- lái xe

- điều khiển

- khô

- hai

- e

- E&T

- hệ sinh thái

- hiệu ứng

- cho phép

- cho phép

- năng lượng

- tăng cường

- đủ

- Kỷ nguyên

- lôi

- đánh giá

- đánh giá

- đánh giá

- Ngay cả

- cuối cùng

- triển lãm

- dự kiến

- khám phá

- Khám phá

- Tiếp xúc

- NHANH

- Tháng Hai

- lĩnh vực

- Hình

- điền

- Phim ảnh

- phim

- Tập trung

- Trong

- Buộc

- xây dựng

- tìm thấy

- từ

- xa hơn

- tương lai

- nhận được

- tốt

- màu xanh lá

- có

- Cứng

- Có

- he

- Được tổ chức

- Cao

- cao hơn

- Ngang

- Độ đáng tin của

- Hướng dẫn

- Tuy nhiên

- HTTPS

- khinh khí

- i

- xác định

- minh họa

- ngâm

- cải thiện

- cải thiện

- cải thiện

- in

- tăng

- Tăng

- chỉ ra

- Cơ sở hạ tầng

- ban đầu

- tính toàn vẹn

- Intel

- kết nối

- giao diện

- Phỏng vấn

- Giới thiệu

- điều tra

- vấn đề

- các vấn đề

- IT

- jpg

- Key

- Lâm

- cảnh quan

- lớn

- lớp

- lớp

- dẫn

- hàng đầu

- niveaux

- Lượt thích

- Dòng

- Danh sách

- địa phương

- logic

- dài

- thời gian dài

- Xem

- tìm kiếm

- NHÌN

- sự mất

- Rất nhiều

- Thấp

- thực hiện

- Làm

- quản lý

- sản xuất

- nhiều

- mặt nạ

- Mặt nạ

- phù hợp

- nguyên vật liệu

- max-width

- Có thể..

- đo

- đo

- cơ khí

- Bộ nhớ

- tin nhắn

- kim loại

- Đo lường

- Kính hiển vi

- Giảm nhẹ

- tiền

- chi tiết

- nhiều

- đa

- Cần

- cần thiết

- nhu cầu

- Mới

- Không

- Tiếng ồn

- tại

- thu được

- of

- off

- Ngoại tuyến

- on

- ONE

- có thể

- Cơ hội

- tối ưu hóa

- or

- hữu cơ

- Nền tảng khác

- ra

- kết thúc

- Vượt qua

- giấy tờ

- Họa tiết

- mô hình

- hiệu suất

- quan điểm

- Pitch

- Plasma

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- thêm

- người nghèo

- Bài đăng

- chuẩn bị

- Thuyết trình

- trình bày

- quà

- Chủ tịch

- chính

- Vấn đề

- quá trình

- Quy trình

- xử lý

- profiling

- chương trình

- Tiến độ

- hứa hẹn

- đã được chứng minh

- cho

- Bức xạ

- Tỷ lệ

- Giá

- tỉ lệ

- Đọc

- Sẵn sàng

- gần đây

- gần đây

- giảm

- Giảm

- làm giảm

- giảm

- liên quan

- vẫn

- đòi hỏi

- Độ phân giải

- kết quả

- Kết quả

- xem xét

- lộ trình

- mạnh mẽ

- Nói

- tương tự

- mở rộng quy mô

- Sean

- xem

- đã xem

- chọn

- TỰ

- SEM

- bán

- nhạy cảm

- Độ nhạy

- thay đổi

- cho thấy

- thể hiện

- bên

- Tín hiệu

- tương tự

- duy nhất

- Kích thước máy

- Slope

- chậm

- nhỏ hơn

- So

- một số

- nguồn

- Không gian

- tốc độ

- tiêu

- Spot

- Tính ổn định

- ổn định

- ổn định

- Stacks

- Steve

- Vẫn còn

- sức mạnh

- mạnh mẽ

- Học tập

- Tiêu đề

- như vậy

- đủ

- cao

- Bề mặt

- đình chỉ

- ngọt ngào

- hệ thống

- hệ thống

- Các cuộc đàm phán

- kỹ thuật

- Công nghệ

- hơn

- việc này

- Sản phẩm

- Khối

- cung cấp their dịch

- sau đó

- Đó

- Kia là

- họ

- điều

- điều này

- năm nay

- những

- số ba

- thông lượng

- thời gian

- đến

- bên nhau

- quá

- công cụ

- công cụ

- đối với

- theo dõi

- lực kéo

- thương mại

- truyền thống

- hai

- kiểu

- cuối cùng

- Dưới

- cho đến khi

- sử dụng

- tận dụng

- Bằng cách sử dụng

- khác nhau

- Versus

- thẳng đứng

- rất

- thông qua

- khả thi

- Phó Chủ Tịch

- Dễ bay hơi

- là

- TỐT

- đi

- Điều gì

- trong khi

- sẽ

- cửa sổ

- với

- Công việc

- viết

- viết

- năm

- bạn

- zephyrnet