Trong những năm qua, các công cụ của DRC đã thực hiện một công việc đáng khâm phục là bắt kịp với sự phát triển vượt bậc về quy mô thiết kế vi mạch. Tuy nhiên, DRC chạy để phê duyệt thiết kế đầy đủ bằng cách sử dụng sàn quy tắc đúc mất nhiều giờ để hoàn thành. Thời gian dài này có thể chấp nhận được đối với lần đăng xuất cuối cùng, nhưng có nhiều trường hợp cần có kết quả DRC nhanh chóng khi những thay đổi nhỏ đang được thực hiện đối với thiết kế để khắc phục các sự cố ở giai đoạn cuối. Siemens EDA kết hợp với MaxLinear đã viết một sách trắng trình bày cách DRC trong thiết kế Calibre RealTime Digital có thể cung cấp kết quả DRC nhanh chóng khi có những thay đổi nhỏ trong thiết kế. Quay vòng DRC nhanh hơn cho các thay đổi được bản địa hóa có thể tăng tốc độ sửa lỗi lặp đi lặp lại thường cần thiết để đạt được băng xuất.

Trong sách trắng có tiêu đề “MaxLinear và Calibre RealTime Digital: Hội tụ DRC đăng xuất nhanh hơn cộng với tối ưu hóa thiết kế cho khả năng sản xuất” MaxLinear và Siemens nói về các trường hợp có khả năng chạy DRC trên một vùng nhỏ của thiết kế với sàn quy tắc đúc đầy đủ có thể tiết kiệm nhiều giờ và lặp đi lặp lại chậm đau đớn.

Các công cụ P&R hiện đại thực hiện xuất sắc công việc tạo ra bố cục chính xác của DRC. Tuy nhiên, luôn có những trường hợp nguồn vi phạm phức tạp hơn và bị bỏ sót trong quá trình P&R. Chúng thường yêu cầu sửa chữa thủ công có tính đến các quy tắc thiết kế phức tạp. Trong quá trình sửa lỗi thủ công này, cũng có khả năng xảy ra các lỗi mới. Siemens trình bày thông tin từ MaxLinear trong sách trắng nêu bật cách Calibre RealTime Digital giao tiếp với công cụ P&R của họ cho phép họ nhanh chóng triển khai và xác thực các bản sửa lỗi thủ công. Cách khác là thực hiện chạy DRC đầy đủ chỉ để xem các thay đổi trong một khu vực nhỏ có đúng không.

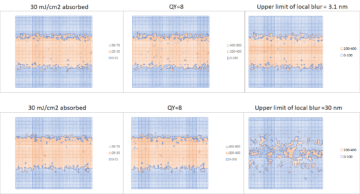

MaxLinear sản xuất chip với các khối tương tự và kỹ thuật số. Các khối tương tự yêu cầu ít lớp kim loại hơn, vì vậy để giảm chi phí sản xuất, họ tìm cách giảm các lớp định tuyến trong toàn bộ thiết kế. Điều này tạo ra các vấn đề về mật độ định tuyến, thường xung đột với việc duy trì xếp hạng DFM cao. Vias cắt một lần sử dụng ít không gian nhất nhưng góp phần vào xếp hạng DFM thấp. Khi gặp khó khăn, các nhà thiết kế MaxLinear có thể chuyển đổi thủ công qua các loại để xử lý khả năng định tuyến so với cân bằng DFM. Nhưng những điều này cần được theo dõi bằng một DRC toàn diện để kiểm tra những thứ như vi phạm đa mẫu. Calibre RealTime Digital cho phép các nhà thiết kế hoán đổi qua các loại và sau đó nhanh chóng xem liệu có tồn tại lỗi DRC nào không.

Vias không phải là vấn đề duy nhất có thể dẫn đến các vấn đề DRC cần thời gian và nỗ lực để giải quyết. Sách trắng mô tả một số tình huống trong đó cần phải thực hiện thao tác thủ công và cách duy nhất để giải quyết triệt để các sự cố này là chạy DRC sạch. Một trong những tình huống xảy ra muộn trong quá trình này là khi cần kiểm tra lại băng từ (RTO) để đảm bảo ECO tương thích với mặt nạ hiện có. Các quy tắc RTO về bản chất là hạn chế hơn so với các quy tắc ban đầu của DRC.

Sách trắng cũng đề cập đến các vấn đề về di chuyển điện có thể do sử dụng vias không phù hợp. Một lần nữa, Calibre ReatTime Digital là công cụ giúp MaxLinear triển khai DRC chính xác thông qua thay thế. Tổng hợp lại, có nhiều trường hợp yêu cầu kiểm tra DRC sau khi thực hiện những thay đổi nhỏ để khắc phục các vấn đề về chức năng hoặc khả năng sản xuất trong thiết kế. Có khả năng nhận được kết quả ngay lập tức, thay vì chờ đợi một ngày hoặc lâu hơn khi chạy DRC đầy đủ, có thể rút ngắn nhiều ngày hoặc nhiều tuần cho một dự án. Sẽ không tốt nếu bạn tìm thấy bất ngờ sau một giải DRC lớn. Giao diện Siemens Calibre RealTime Digital cho các công cụ P&R dường như là một sự phù hợp lý tưởng cho việc này. Bạn có thể tìm thấy sách trắng này của Siemens trên trang web EDA của Siemens.

Chia sẻ bài đăng này qua:

Nguồn: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/

- Tất cả

- KHU VỰC

- bài viết

- gây ra

- Séc

- Snacks

- xung đột

- nội dung

- ngày

- nhiều

- Thiết kế

- kỹ thuật số

- Cuối cùng

- phù hợp với

- Sửa chữa

- Foundry

- Full

- tốt

- Tăng trưởng

- tại đây

- Cao

- Độ đáng tin của

- HTTPS

- lớn

- thông tin

- các vấn đề

- Việc làm

- giữ

- dẫn

- dài

- sản xuất

- Mặt nạ

- kim loại

- Giấy

- dự án

- giảm

- Kết quả

- quy tắc

- chạy

- Siemens

- Kích thước máy

- nhỏ

- So

- Không gian

- tốc độ

- Traineeship

- Công tắc điện

- thumbnail

- thời gian

- Versus

- Website

- giấy trắng

- Công việc

- năm