Một bài báo kỹ thuật mới có tiêu đề “Thiết kế logic động phi truyền thống sử dụng FDSOI cho điện toán cực kỳ hiệu quả” đã được xuất bản bởi các nhà nghiên cứu tại Đại học Stuttgart, UC Berkeley, Viện Công nghệ Ấn Độ Kanpur và TU Munich, với sự tài trợ của Quỹ nghiên cứu Đức .

Tóm tắt

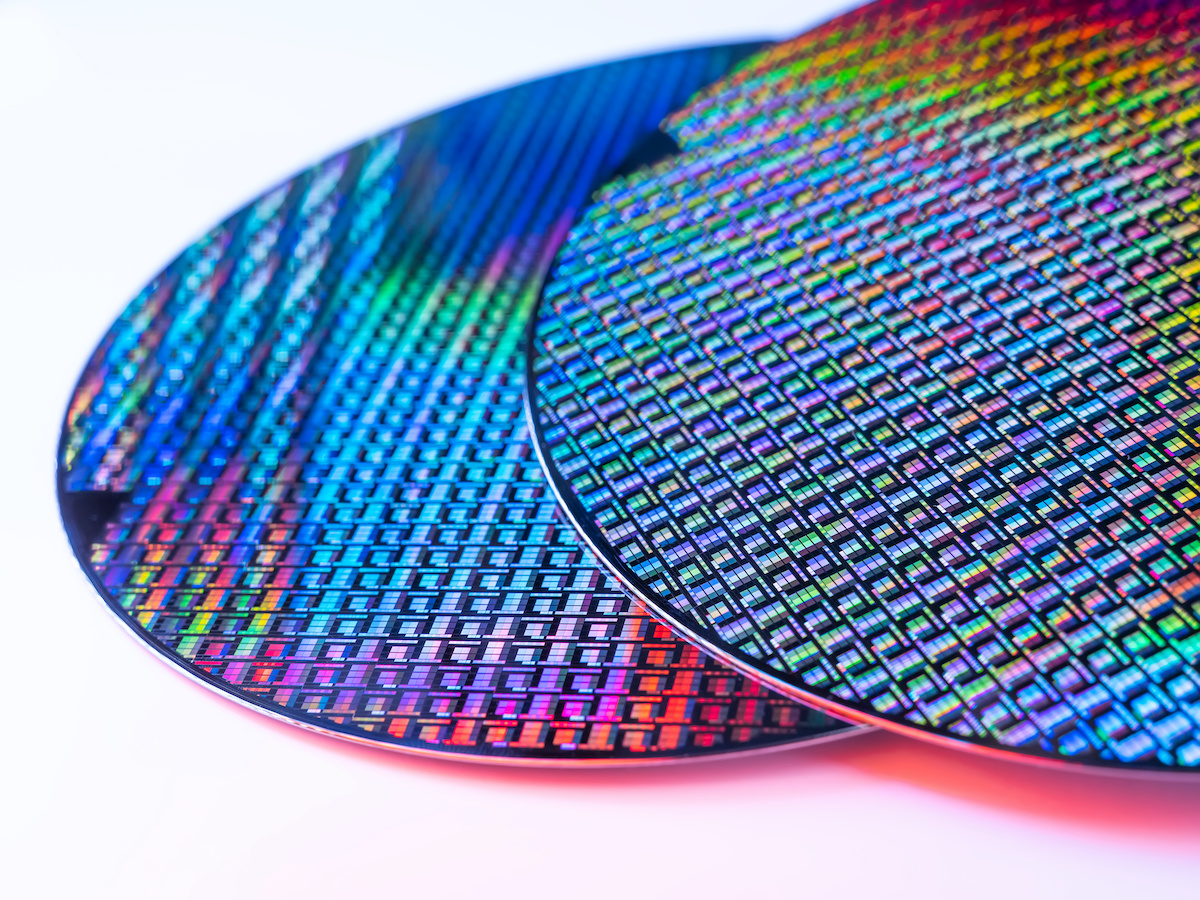

“Trong bài báo này, chúng tôi đề xuất một thiết kế phi truyền thống của các mạch logic động sử dụng FET Silicon trên Chất cách điện (FDSOI) đã cạn kiệt hoàn toàn. FDSOI FET cho phép điện áp ngưỡng ( Vt ) có thể điều chỉnh được (nghĩa là trạng thái Vt thấp và Vt cao) bằng cách sử dụng độ lệch cổng sau. Thiết kế của chúng tôi sử dụng các cổng trước và sau của FDSOI FET làm đầu cuối đầu vào và đề xuất các cổng logic động (như; NAND, NOR, AND, OR, XOR và XNOR) và các mạch (như; bộ cộng một nửa và bộ cộng đầy đủ). Nó yêu cầu ít bóng bán dẫn hơn để xây dựng các cổng logic động và đạt được hiệu suất cao với mức tiêu thụ điện năng thấp so với các thiết kế logic động thông thường. Mô hình công nghiệp nhỏ gọn của FDSOI FET (BSIM-IMG) đã được sử dụng để mô phỏng các cổng logic động và được hiệu chỉnh đầy đủ để tái tạo dữ liệu nút công nghệ FDSOI FET 14nm. Hiệu chuẩn được thực hiện cho cả các đặc tính điện và các biến thể của quy trình. Kết quả mô phỏng cho thấy sự cải thiện trung bình về số lượng bóng bán dẫn, độ trễ lan truyền, công suất và sản phẩm độ trễ công suất lần lượt là 23.43%, 57.16%, 47.05% và 77.29% so với các thiết kế thông thường. Hơn nữa, thiết kế của chúng tôi làm giảm hiệu ứng chia sẻ điện tích, ảnh hưởng đến khả năng điều khiển của các cổng logic động. Ngoài ra, chúng tôi đã phân tích tác động của quá trình, điện áp cung cấp và sự thay đổi điện dung tải đối với độ trễ lan truyền của họ logic động một cách chi tiết. Kết quả cho thấy rằng các biến thể này có tác động nhỏ đến độ trễ lan truyền của các cổng logic động dựa trên FDSOI được đề xuất so với các cổng logic động thông thường.”

Tìm giấy kỹ thuật ở đây. Xuất bản tháng 2023 năm XNUMX.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan và H. Amrouch, “Thiết kế phi truyền thống của logic động sử dụng FDSOI cho điện toán cực kỳ hiệu quả,” trong Tạp chí IEEE về mạch và thiết bị điện toán thể rắn khám phá, doi: 10.1109/JXCDC.2023.3269141. Mở truy cậps.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- Mua và bán cổ phần trong các công ty PRE-IPO với PREIPO®. Truy cập Tại đây.

- nguồn: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- : có

- :là

- 10

- 2023

- 23

- 77

- a

- Đạt được

- Ngoài ra

- điều chỉnh

- cho phép

- an

- và

- Tháng Tư

- AS

- At

- Trung bình cộng

- trở lại

- BE

- được

- Berkeley

- thiên vị

- cả hai

- xây dựng

- by

- đặc điểm

- phí

- so

- máy tính

- thông thường

- dữ liệu

- chậm trễ

- Thiết kế

- thiết kế

- chi tiết

- Thiết bị (Devices)

- năng động

- e

- hiệu lực

- gia đình

- FET

- ít hơn

- Trong

- Nền tảng

- trước mặt

- Full

- đầy đủ

- tài trợ

- xa hơn

- Gates

- Tiếng Đức

- Một nửa

- Có

- Cao

- HTTPS

- i

- IEEE

- Va chạm

- cải thiện

- in

- người Ấn Độ

- công nghiệp

- đầu vào

- Viện

- IT

- tạp chí

- Lượt thích

- tải

- logic

- Thấp

- nhỏ

- kiểu mẫu

- Munich

- Mới

- nút

- of

- on

- or

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- Giấy

- hiệu suất

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- quyền lực

- quá trình

- Sản phẩm

- đề xuất

- đề xuất

- đề xuất

- công bố

- làm giảm

- đòi hỏi

- nghiên cứu

- nhà nghiên cứu

- tương ứng

- Kết quả

- s

- chia sẻ

- hiển thị

- Silicon

- mô phỏng

- Bang

- cung cấp

- Kỹ thuật

- Công nghệ

- việc này

- Sản phẩm

- Kia là

- điều này

- ngưỡng

- có tiêu đề

- đến

- trường đại học

- đã sử dụng

- sử dụng

- sử dụng

- điện áp

- là

- we

- cái nào

- với

- zephyrnet