Cụm từ cũ cho rằng việc chữa khỏi còn tệ hơn căn bệnh này là phù hợp khi thảo luận về MBIST cho các SOC lớn, nơi việc chạy song song nhiều thử nghiệm MBIST có thể vượt quá khả năng của mạng phân phối điện (PDN). Tự kiểm tra tích hợp bộ nhớ (MBIST) thường chạy tự động trong các sự kiện bật nguồn. Do mong muốn tăng tốc độ kiểm tra và thời gian khởi động chip nên các thử nghiệm này thường được chạy song song. Vấn đề là chúng có thể dễ dàng tạo ra hoạt động chuyển mạch cao hơn nhiều so với mức được tìm thấy trong quá trình vận hành chip thông thường. Thật vậy, mức hoạt động chuyển mạch cao hơn này không chỉ có thể gây ra tình trạng sụt giảm nguồn cung ảnh hưởng đến kết quả thử nghiệm mà lượng nhiệt sinh ra cao còn có thể gây hại cho chip. Những tác động này có thể dẫn đến việc phân nhóm không chính xác hoặc các sự kiện xảy ra lỗi trực tiếp và tiềm ẩn.

Giải pháp là mô phỏng hoạt động MBIST để dự đoán tải trên PDN và các hiệu ứng nhiệt liên quan. Với kết quả mô phỏng trong tay, các nhà thiết kế có thể quyết định chính xác số lượng và khối bộ nhớ nào có thể được kiểm tra song song. Tuy nhiên, điều này không phải lúc nào cũng khả thi trong các SOC lớn có nhiều khối bộ nhớ vì thời gian mô phỏng có thể bị hạn chế. Với mức cổng và mô phỏng RTL kém chính xác hơn, có thể không chạy đủ chu kỳ để có được thông tin cần thiết.

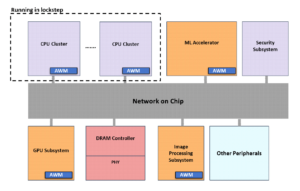

Trong sách trắng có tiêu đề “Phân tích tác động sức mạnh của việc sử dụng MBIST”, Siemens EDA xem xét cách các nhà thiết kế có thể chạy mô phỏng đầy đủ để đưa ra quyết định sáng suốt về chiến lược thử nghiệm trước khi triển khai. Siemens đã làm việc với ARM trên một trong các chip thử nghiệm của họ để tạo trường hợp thử nghiệm trong đó họ có thể áp dụng mô phỏng phần cứng với ứng dụng DFT và Power cho trình mô phỏng phần cứng Veloce của Siemens. Đầu tiên, ứng dụng Veloce DFT được sử dụng để xuất hoạt động nội bộ trong quá trình mô phỏng MBIST. Ứng dụng sử dụng Ngôn ngữ giao diện thử nghiệm tiêu chuẩn (STIL) và tạo ra các tệp đầu ra tiêu chuẩn ngành.

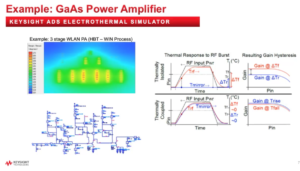

Ứng dụng Veloce Power lấy thông tin hoạt động từ các lần chạy MBIST để tạo dạng sóng, cấu hình nguồn và bản đồ nhiệt có thể cho biết khi nào có mức điện tăng đột biến vượt quá giới hạn quy định. Với thông tin này, các kỹ sư kiểm tra có thể đưa ra quyết định sáng suốt về trình tự của MBIST.

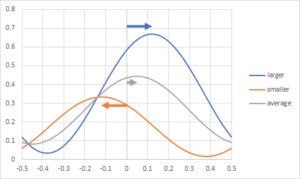

Trường hợp thử nghiệm ARM được mô tả trong sách trắng của Siemens chứa 176 triệu cổng. Siemens đã sử dụng hệ thống Veloce với 6 bảng Veloce Strato cho trường hợp thử nghiệm này. Quá trình chạy trình mô phỏng Veloce chỉ mất 26 giờ, nhanh hơn 15,600 lần so với mô phỏng cấp cổng. Một lợi ích khác của luồng Veloce là thông tin hoạt động được ứng dụng Power truyền trực tuyến tới các công cụ quyền lực trong luồng, giúp tiết kiệm dung lượng và thời gian trên ổ đĩa. Kết quả từ trường hợp thử nghiệm cho thấy một số xung điện vi phạm các thông số kỹ thuật thiết kế SOC. Đầu ra từ ứng dụng Veloce Power hiển thị tổng mức công suất thông qua mô phỏng cùng với sự đóng góp công suất riêng biệt cho đồng hồ, logic tổ hợp và bộ nhớ. Tương tự như vậy, có thông tin về nơi năng lượng đang được sử dụng trên khuôn. Thông tin này giúp bạn dễ dàng xác định nơi có vấn đề.

Việc tìm ra những vấn đề như vậy đòi hỏi phải chạy hàng triệu hoặc hàng tỷ chu kỳ đồng hồ. Những hạn chế của trình mô phỏng phần mềm khiến việc thực hiện các phân tích cần thiết trở nên khó khăn. Mô phỏng cung cấp một phương pháp độc đáo để kiểm tra chặt chẽ tác động về năng lượng của MBIST và các hoạt động thử nghiệm khác từ rất lâu trước khi có silicon. Sách trắng của Siemens cung cấp cái nhìn sâu sắc về phương pháp năng lượng được sử dụng trong trường hợp thử nghiệm thực tế. Sách trắng có sẵn để tải xuống và đọc trên trang web của Siemens.

Chia sẻ bài đăng này qua: Nguồn: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Giới thiệu

- phân tích

- ứng dụng

- ứng dụng

- ARM

- có sẵn

- được

- Nguyên nhân

- Chip

- Snacks

- Đồng hồ

- chứa

- có thể

- chữa bệnh

- Thiết kế

- Bệnh

- suốt trong

- dễ dàng

- Kỹ sư

- Sự kiện

- sự kiện

- nhanh hơn

- Tên

- dòng chảy

- tìm thấy

- Gates

- tạo ra

- phần cứng

- Cao

- Độ đáng tin của

- HTTPS

- ngành công nghiệp

- thông tin

- IT

- Ngôn ngữ

- lớn

- dẫn

- Cấp

- niveaux

- tải

- dài

- Maps

- triệu

- hàng triệu

- cần thiết

- mạng

- Cung cấp

- Hoạt động

- gọi món

- Nền tảng khác

- Giấy

- quyền lực

- Vấn đề

- Profiles

- Reading

- Kết quả

- chạy

- chạy

- tiết kiệm

- Siemens

- mô phỏng

- Phần mềm

- Không gian

- tốc độ

- Chiến lược

- xem trực tiếp

- cung cấp

- hệ thống

- thử nghiệm

- Kiểm tra

- kiểm tra

- nhiệt

- Thông qua

- thời gian

- công cụ

- độc đáo

- thường

- Website

- giấy trắng

- làm việc