Kể từ khi ra mắt vào những năm 1980 với mạng LAN chia sẻ 10Mbps qua cáp đồng trục, Ethernet đã chứng kiến những tiến bộ nhất quán, giờ đây có tiềm năng hỗ trợ tốc độ lên tới 1.6Tbps. Sự phát triển này đã cho phép Ethernet phục vụ nhiều ứng dụng hơn, chẳng hạn như phát trực tiếp, Mạng truy cập vô tuyến và điều khiển công nghiệp, nhấn mạnh tầm quan trọng của việc truyền gói đáng tin cậy và chất lượng dịch vụ. Với băng thông Internet hiện tại ở mức ~500 Tbps, nhu cầu xử lý lưu lượng truy cập nội bộ trung tâm dữ liệu phía sau được cải thiện ngày càng tăng. Mặc dù các máy chủ riêng lẻ vẫn chưa hoạt động ở mức Terabit/giây, lưu lượng trung tâm dữ liệu tổng thể đang tiến gần đến quy mô này, khiến nhóm 802.3dj của IEEE phải thực hiện các nỗ lực tiêu chuẩn hóa và yêu cầu các bộ điều khiển Ethernet và SerDes mạnh mẽ để quản lý luồng dữ liệu đang mở rộng. Trong bối cảnh nhu cầu ngày càng tăng, giao tiếp giữa các bộ xử lý đã đạt được tốc độ này.

Giao tiếp giữa các bộ xử lý đang dẫn đầu nhu cầu về tốc độ 1.6T với độ trễ tối thiểu. Trong khi các thiết bị riêng lẻ bị hạn chế bởi khả năng xử lý vốn có và kích thước chip, việc kết hợp các chip có thể mở rộng đáng kể những khả năng này. Thế hệ ứng dụng đầu tiên dự kiến sẽ được nối tiếp bằng các kết nối chuyển đổi giữa các trung tâm dữ liệu nội bộ, cho phép tập hợp các bộ xử lý và bộ nhớ hiệu suất cao, tăng cường khả năng mở rộng và hiệu quả trong điện toán đám mây.

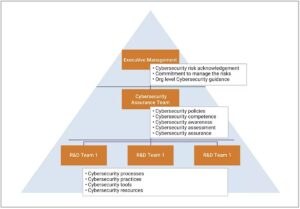

Sáng kiến 802.3dj của IEEE: Nâng cao các tiêu chuẩn Ethernet cho khả năng tương tác 1.6 Tbps

Việc tuân thủ các nỗ lực tiêu chuẩn hóa ngày càng phát triển là yếu tố then chốt để đảm bảo khả năng tương tác liền mạch của hệ sinh thái. Nhóm 802.3dj của IEEE đang trong quá trình xây dựng tiêu chuẩn Ethernet sắp tới, bao gồm các lớp vật lý và các tham số quản lý cho tốc độ từ 200G đến 1.6 Terabit mỗi giây. Mục tiêu của nhóm là tốc độ dữ liệu Ethernet MAC 1.6 Tbps, hướng tới tỷ lệ lỗi bit tối đa không quá 10-13 ở lớp MAC. Các điều khoản khác bao gồm Giao diện thiết bị đính kèm (AUI) 16 & 8 làn tùy chọn phù hợp cho các ứng dụng chip khác nhau, tận dụng SerDes 112G và 224G. Về mặt vật lý, thông số kỹ thuật 1.6Tbps đòi hỏi phải truyền qua 8 cặp cáp đôi đồng trục dài tối đa 8 mét và 500 cặp sợi quang cho khoảng cách từ 2 mét đến 2026 km. Mặc dù dự kiến việc phê chuẩn hoàn chỉnh của tiêu chuẩn sẽ diễn ra vào mùa xuân năm 2024, nhưng bộ tính năng cốt lõi dự kiến sẽ hoàn thành vào năm XNUMX.

Chi phí băng thông và sửa lỗi trong hệ thống con Ethernet 1.6T

Hình 1: Sơ đồ mô tả các thành phần của Hệ thống con Ethernet 1.6T.

Trong các phiên bản Ethernet trước đó, PCS chủ yếu tập trung vào mã hóa dữ liệu để phát hiện gói tin đáng tin cậy. Tuy nhiên, với tốc độ Ethernet tăng lên 1.6T, nhu cầu Sửa lỗi chuyển tiếp (FEC) trở nên rõ ràng, đặc biệt là để chống lại sự suy giảm tín hiệu ngay cả trên các liên kết ngắn. Với mục đích này, Ethernet 1.6T tiếp tục sử dụng Reed-Solomon FEC. Cách tiếp cận này xây dựng một từ mã bao gồm 514 ký hiệu 10 bit được mã hóa thành khối ký hiệu 544, dẫn đến chi phí băng thông là 6%. Các từ mã FEC này được phân phối trên các liên kết vật lý AUI sao cho mỗi liên kết vật lý (8 cho Ethernet 1.6T) không mang toàn bộ từ mã. Phương pháp này không chỉ cung cấp khả năng bảo vệ bổ sung chống lại các đợt lỗi mà còn cho phép thực hiện song song hóa ở bộ giải mã đầu xa, do đó làm giảm độ trễ.

Thiết bị đính kèm phương tiện vật lý (PMA), bao gồm hộp số và SerDes, đưa tín hiệu Ethernet lên các kênh được truyền. Đối với Ethernet 1.6T, điều này bao gồm 8 kênh, mỗi kênh chạy ở tốc độ 212Gbps, chiếm 6% chi phí FEC. Kỹ thuật điều chế được sử dụng là Điều chế biên độ xung 4 cấp (PAM-4), mã hóa hai bit dữ liệu cho mỗi ký hiệu truyền, do đó tăng gấp đôi băng thông một cách hiệu quả khi kết hợp với phương pháp Non-Return Zero (NRZ) truyền thống. Cơ chế truyền dựa trên chuyển đổi kỹ thuật số sang tương tự, trong khi ở đầu nhận, chuyển đổi tương tự sang kỹ thuật số kết hợp với DSP đảm bảo trích xuất tín hiệu chính xác.

Hơn nữa, điều quan trọng cần lưu ý là Ethernet PCS giới thiệu một “FEC bên ngoài” trải dài từ đầu đến cuối trên liên kết Ethernet. Để củng cố các kênh có phạm vi tiếp cận dài hơn, một lớp sửa lỗi bổ sung cho từng đường truyền vật lý đang được triển khai, có khả năng áp dụng mã hamming FEC. Sự hiệu chỉnh này dự kiến sẽ tìm thấy ứng dụng chính của nó trong các mô-đun thu phát quang, nơi việc hiệu chỉnh như vậy là bắt buộc.

Hình 2: Sơ đồ thể hiện chi phí bổ sung được thêm vào khi sử dụng FEC được nối để mở rộng phạm vi tiếp cận.

Trong hệ thống ví dụ được mô tả ở hình 2, MAC và PCS được kết nối thông qua một mô-đun quang và một sợi quang. PCS có tỷ lệ lỗi bit là 10-5 tại liên kết mô-đun quang, cộng với các lỗi từ chính liên kết quang. Chỉ sử dụng một đầu cuối RS-FEC duy nhất sẽ không đủ để đạt được điểm 10-13 Tiêu chuẩn Ethernet, khiến liên kết không đáng tin cậy. Một tùy chọn sẽ là triển khai ba lần RS FEC riêng biệt trên mỗi bước nhảy, làm tăng đáng kể chi phí và độ trễ. Một giải pháp hiệu quả hơn là tích hợp Mã Hamming FEC được ghép nối dành riêng cho liên kết quang, phục vụ cho các lỗi ngẫu nhiên điển hình của kết nối quang. Lớp FEC bên trong này tạo ra sự mở rộng bổ sung về tốc độ đường truyền từ 212 Gbps lên 226 Gbps, do đó điều cần thiết là SerDes có thể hỗ trợ tốc độ đường truyền này.

Những thách thức về độ trễ trong hệ thống Ethernet 1.6T

Hình 3: Đường dẫn độ trễ cho Hệ thống con Ethernet 1.6T.

Các thành phần khác nhau góp phần tạo ra độ trễ Ethernet: hàng đợi truyền, thời lượng truyền, thời gian truyền trung bình và một số thời gian xử lý và nhận. Để hình dung điều này, hãy xem hình 3, hiển thị hệ thống con Ethernet 1.6T toàn diện. Mặc dù độ trễ có thể bị ảnh hưởng bởi thời gian phản hồi của ứng dụng xa, yếu tố này nằm ngoài Ethernet và do đó thường bị loại trừ trong quá trình phân tích độ trễ. Giảm thiểu độ trễ ở giao diện Ethernet đòi hỏi phải hiểu rõ các trường hợp cụ thể. Ví dụ: độ trễ có thể không phải là mối quan tâm chính đối với các kết nối đường trục giữa các thiết bị chuyển mạch do độ trễ cố hữu trên các liên kết máy khách chậm hơn. Khoảng cách cũng đóng một vai trò nào đó; độ dài lớn hơn giới thiệu độ trễ nhiều hơn. Tất nhiên, điều này không có nghĩa là chúng ta nên bỏ qua độ trễ trong các tình huống khác, việc giảm độ trễ luôn là mục tiêu.

Độ trễ truyền vốn gắn liền với tốc độ Ethernet và kích thước khung hình. Cụ thể, đối với hệ thống Ethernet 1.6T, việc truyền gói có kích thước tối thiểu cần 0.4ns – về cơ bản là một khung Ethernet trên mỗi tích tắc của xung nhịp 2.5 GHz. Mặt khác, việc truyền khung có kích thước tối đa tiêu chuẩn mất 8ns, kéo dài đến 48ns đối với Khung Jumbo. Phương tiện được chọn sẽ quyết định thêm độ trễ. Ví dụ, cáp quang thường có độ trễ là 5ns/m, trong khi cáp đồng nhanh hơn một chút ở mức 4ns/m.

Một phần đáng kể của độ trễ tổng thể bắt nguồn từ bộ điều khiển máy thu. Bộ giải mã RS FEC vốn đã gây ra độ trễ. Để bắt đầu sửa lỗi, hệ thống phải nhận được 4 từ mã, với tốc độ 1.6 Tbps, tương đương 12.8ns. Các hoạt động tiếp theo, bao gồm sửa lỗi và lưu vào bộ đệm, sẽ tăng độ trễ này. Trong khi thời lượng lưu trữ từ mã FEC vẫn nhất quán thì độ trễ trong quá trình nhận bản tin phụ thuộc vào việc triển khai cụ thể. Tuy nhiên, độ trễ có thể được tối ưu hóa bằng cách sử dụng các chiến lược thiết kế kỹ thuật số tỉ mỉ.

Về bản chất, có một độ trễ cố hữu không thể tránh khỏi do cơ chế FEC và khoảng cách vật lý hoặc chiều dài cáp. Ngoài những yếu tố này, kiến thức chuyên môn về thiết kế đóng vai trò then chốt để giảm thiểu độ trễ của bộ điều khiển Ethernet. Tận dụng giải pháp hoàn chỉnh tích hợp và tối ưu hóa MAC, PCS và PHY, mở đường cho việc triển khai độ trễ thấp, hiệu quả nhất.

Tổng kết

Hình 4: Thành công silicon bước đầu cho Synopsys 224G Ethernet PHY IP trong quy trình 3nm cho thấy mắt PAM-4 có độ tuyến tính cao.

Ethernet 1.6 Tbps được thiết kế riêng cho các ứng dụng nhạy cảm với độ trễ và yêu cầu băng thông cao nhất. Với sự xuất hiện của công nghệ 224G SerDes, kết hợp với những tiến bộ trong MAC và PCS IP, giờ đây có thể truy cập được các giải pháp toàn diện và liên tục tuân thủ các tiêu chuẩn Ethernet 1.6T đang phát triển. Ngoài ra, do độ trễ nội tại của giao thức và phương pháp sửa lỗi, thiết kế analog và kỹ thuật số IP phải được các nhà thiết kế chuyên nghiệp thực hiện một cách tỉ mỉ để tránh tạo ra độ trễ không cần thiết vào đường dẫn dữ liệu.

Để đạt được hiệu suất cao nhất cho các thiết kế SoC 1.6T đòi hỏi phải có kiến trúc được tối ưu hóa hiệu quả và thực hành thiết kế tỉ mỉ cho mọi thành phần chip. Điều này nhấn mạnh đến việc tiết kiệm năng lượng và giảm thiểu dấu chân silicon, biến tốc độ dữ liệu 1.6T thành hiện thực. Bản tóm tắt đã được chứng minh bằng silicon 224G Ethernet PHY IP đã tạo tiền đề cho Bộ điều khiển MAC và PCS 1.6T. Sử dụng các kỹ thuật thiết kế, phân tích, mô phỏng và đo lường hàng đầu, Synopsys tiếp tục mang lại tính toàn vẹn tín hiệu và hiệu suất jitter vượt trội, với giải pháp Ethernet hoàn chỉnh bao gồm MAC+PCS+PHY.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- truy cập

- có thể truy cập

- Kế toán

- chính xác

- Đạt được

- ngang qua

- hoạt động

- thêm

- thêm vào

- Ngoài ra

- Nhận nuôi

- tiến bộ

- thăng tiến

- chống lại

- Định hướng

- cho phép

- Đã

- Ngoài ra

- Mặc dù

- luôn luôn

- giữa

- số lượng

- khoa trương

- an

- phân tích

- và

- Dự đoán

- Các Ứng Dụng

- các ứng dụng

- phương pháp tiếp cận

- kiến trúc

- LÀ

- AS

- At

- tránh

- Back-end

- bối cảnh

- Băng thông

- BE

- trở thành

- giữa

- Ngoài

- Một chút

- Chặn

- tăng cường

- thúc đẩy

- Mang lại

- xây dựng

- nhưng

- by

- cáp

- cáp

- CAN

- năng lực

- mang

- thách thức

- kênh

- Chip

- Snacks

- lựa chọn

- hoàn cảnh

- khách hàng

- Đồng hồ

- đám mây

- điện toán đám mây

- mã

- kết hợp

- kết hợp

- Giao tiếp

- hoàn thành

- hoàn thành

- thành phần

- các thành phần

- toàn diện

- bao gồm

- máy tính

- Liên quan

- kết hợp

- kết nối

- Kết nối

- SỰ BẢO TỒN

- Hãy xem xét

- sự cân nhắc

- thích hợp

- liên tiếp

- liên tục

- Góp phần

- điều khiển

- điều khiển

- Chuyển đổi

- Copper

- Trung tâm

- Chi phí

- chống lại

- khóa học mơ ước

- chế tạo

- tạo ra

- Current

- dữ liệu

- Trung tâm dữ liệu

- ra mắt

- sự chậm trễ

- cung cấp

- Nhu cầu

- yêu cầu

- nhu cầu

- miêu tả

- Thiết kế

- thiết kế

- thiết kế

- Phát hiện

- Thiết bị (Devices)

- ra lệnh

- khác nhau

- kỹ thuật số

- siêng năng

- màn hình

- khoảng cách

- phân phối

- Không

- tăng gấp đôi

- hai

- thời gian

- suốt trong

- mỗi

- Sớm hơn

- hệ sinh thái

- Hiệu quả

- hiệu quả

- hiệu quả

- hiệu quả

- hiệu quả

- những nỗ lực

- sự xuất hiện

- nhấn mạnh

- nhấn mạnh

- việc làm

- thuê mướn

- cho phép

- cho phép

- bao trùm

- cuối

- Cuối cùng đến cuối

- đảm bảo

- Toàn bộ

- lôi

- lỗi

- leo thang

- bản chất

- thiết yếu

- chủ yếu

- Ether (ETH)

- Ngay cả

- Mỗi

- hiển nhiên

- phát triển

- ví dụ

- đặc biệt

- loại trừ

- mở rộng

- mở rộng

- dự kiến

- chuyên gia

- chuyên môn

- thêm

- mở rộng

- ngoài

- khai thác

- Mắt

- yếu tố

- các yếu tố

- xa

- nhanh hơn

- Tính năng

- Với

- Hình

- Tìm kiếm

- Tên

- Thế hệ đầu tiên

- dòng chảy

- tập trung

- sau

- Dấu chân

- Trong

- xây dựng

- Forward

- FRAME

- từ

- xa hơn

- thế hệ

- cho

- lớn hơn

- Nhóm

- Các nhóm

- Phát triển

- tay

- Xử lý

- Cao

- hiệu suất cao

- cao

- Tuy nhiên

- HTML

- HTTPS

- bắt buộc

- thực hiện

- tầm quan trọng

- quan trọng

- cải thiện

- in

- Mặt khác

- bao gồm

- Bao gồm

- tăng

- hệ thống riêng biệt,

- công nghiệp

- bị ảnh hưởng

- vốn có

- vốn có

- bắt đầu

- Sáng kiến

- ví dụ

- Tích hợp

- hội nhập

- tính toàn vẹn

- Giao thức

- giao diện

- Internet

- Khả năng cộng tác

- trong

- nội tại

- giới thiệu

- Giới thiệu

- giới thiệu

- liên quan đến

- IP

- IT

- sự lặp lại

- ITS

- chính nó

- jpg

- Đường nhỏ

- Độ trễ

- lớp

- lớp

- Chiều dài

- niveaux

- tận dụng

- Có khả năng

- Dòng

- dòng

- LINK

- liên kết

- sống

- còn

- Thấp

- mac

- Làm

- quản lý

- quản lý

- max-width

- tối đa

- Có thể..

- nghĩa là

- đo lường

- cơ chế

- trung bình

- Bộ nhớ

- tin nhắn

- phương pháp

- phương pháp

- tỉ mỉ

- tối thiểu

- giảm thiểu

- giảm thiểu

- giảm thiểu

- mô-đun

- Modules

- chi tiết

- hầu hết

- phải

- gần

- Cần

- mạng

- Tuy nhiên

- Không

- ghi

- tại

- Mục tiêu

- of

- thường

- on

- ONE

- có thể

- hoạt động

- tối ưu hóa

- Tối ưu hóa

- Tùy chọn

- or

- Nền tảng khác

- kết thúc

- tổng thể

- cặp

- thông số

- đặc biệt

- con đường

- máy tính

- mỗi

- hiệu suất

- biểu diễn

- vật lý

- Thể chất

- đường ống dẫn

- quan trọng

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- đóng

- thêm

- tiềm năng

- quyền lực

- thực hành

- chủ yếu

- chính

- quá trình

- xử lý

- bộ vi xử lý

- tiến triển

- dự

- bảo vệ

- giao thức

- xung

- mục đích

- Đẩy

- chất lượng

- radio

- ngẫu nhiên

- phạm vi

- Tỷ lệ

- Giá

- đạt

- đạt

- phản ứng

- Thực tế

- nhận

- nhận

- tiếp nhận

- giảm

- đáng tin cậy

- vẫn còn

- vẽ

- đòi hỏi

- hạn chế

- kết quả

- mạnh mẽ

- Vai trò

- Bắt nguồn

- chạy

- khả năng mở rộng

- Quy mô

- kịch bản

- liền mạch

- Thứ hai

- đã xem

- phân khúc

- nhạy cảm

- riêng biệt

- phục vụ

- dịch vụ

- định

- một số

- chia sẻ

- ngắn

- nên

- giới th

- Tín hiệu

- đáng kể

- Silicon

- mô phỏng

- Kích thước máy

- So

- giải pháp

- Giải pháp

- nhịp

- mũi nhọn

- riêng

- đặc biệt

- đặc điểm kỹ thuật

- tốc độ

- mùa xuân

- Traineeship

- Tiêu chuẩn

- tiêu chuẩn hóa

- tiêu chuẩn

- là gắn

- chiến lược

- trực tuyến

- tiếp theo

- đáng kể

- thành công

- như vậy

- phù hợp

- hỗ trợ

- biểu tượng

- hệ thống

- phù hợp

- mất

- kỹ thuật

- kỹ thuật

- Công nghệ

- hơn

- việc này

- Sản phẩm

- cung cấp their dịch

- Đó

- bằng cách ấy

- vì thế

- Kia là

- điều này

- Thông qua

- Như vậy

- đánh dấu

- Bị ràng buộc

- thời gian

- thời gian

- đến

- hàng đầu

- truyền thống

- giao thông

- chuyển

- truyền

- Gấp ba lần

- hai

- điển hình

- thường

- không thể tránh khỏi

- sự hiểu biết

- thực hiện

- đơn vị

- sắp tới

- trên

- sử dụng

- sử dụng

- thông qua

- hình dung

- Đường..

- we

- khi nào

- cái nào

- trong khi

- rộng hơn

- với

- ở trong

- sẽ

- nhưng

- zephyrnet

- không