Khắc plasma có lẽ là quy trình thiết yếu nhất trong sản xuất chất bán dẫn và có thể là phức tạp nhất trong tất cả các hoạt động chế tạo bên cạnh quang khắc. Gần một nửa tất cả các bước fab đều dựa vào plasma, một loại khí ion hóa năng lượng, để thực hiện công việc của chúng.

Mặc dù các ô nhớ và bóng bán dẫn ngày càng thu hẹp, các kỹ sư vẫn tiếp tục cung cấp các quy trình khắc đáng tin cậy.

Thomas Bondur, phó chủ tịch công ty cho biết: “Để tạo ra những con chip bền vững với độ chính xác ở cấp độ nano và cấu trúc chi phí phù hợp, các nhà sản xuất thiết bị wafer fab cần phải vượt qua ranh giới của vật lý plasma, kỹ thuật vật liệu và khoa học dữ liệu để cung cấp các giải pháp thiết bị cần thiết”. Tiếp thị nhóm sản phẩm Etch tại Nghiên cứu Lam. Điều này không ở đâu thể hiện rõ ràng hơn trong khắc plasma, hoạt động song song với kỹ thuật in thạch bản để tạo ra các tính năng chính xác, có thể lặp lại trên các tấm wafer.

Báo cáo này xem xét các bước khắc chính trong 3D NAND, DRAM, FET tấm nano và kết nối với nhau, với cái nhìn tương lai về các thiết bị 2D và quá trình xử lý phía sau ngân sách thấp. Ngành công nghiệp cũng đang theo đuổi các hóa chất ăn mòn bền vững hơn để giảm CO tương đương2 khí thải từ fabs của nó.

Đối với nhiều nhà chế tạo công cụ, mô hình hóa quy trình đóng một vai trò then chốt trong quá trình phát triển quy trình khắc. Mục tiêu là rút ngắn thời gian đưa sản phẩm ra thị trường đồng thời giảm chi phí tấm wafer và mặt nạ.

Barrett Finch, giám đốc tiếp thị cấp cao của Lam Research cho biết: “Việc tối ưu hóa quy trình khắc trên một số bước phức tạp nhất có thể mất một năm hoặc hơn để hoàn thành. “Gần đây, chúng tôi đã hoàn thành một số công việc mô phỏng quy trình trong ba tuần, dự kiến sẽ mất ba tháng bằng cách sử dụng thử nghiệm và phát triển dựa trên silicon thông thường.”

Con số này có thể lên tới hàng trăm nghìn, thậm chí hàng triệu đô la, chỉ tính riêng chi phí mặt nạ và tấm wafer cho một nhà sản xuất thiết bị.

khắc cơ bản

Quá trình khắc hoạt động song song với in thạch bản. Quá trình ăn mòn thường được thực hiện trước khi lắng đọng một lớp màng (bằng cách lắng đọng hơi epitaxy, hóa học hoặc vật lý, v.v.). Thông thường, một CVD phim được phủ bằng thợ quang học và sau đó tiếp xúc thông qua một mô hình kẻ ô (mặt nạ) sử dụng in thạch bản quang học (248nm hoặc 193nm UV, 13.5nm EUV). Chống lại sự phát triển sau đó tiết lộ khuôn mẫu. Trong một buồng ăn mòn plasma wafer duy nhất, điển hình là các hóa chất và ion ăn mòn bắn phá và loại bỏ màng CVD nơi thiếu chất cản quang (ở điện trở âm dương). Sau khi ăn mòn, chống tro hóa, làm sạch bằng hóa chất ướt và/hoặc ăn mòn ướt sẽ loại bỏ cặn.

Các quá trình ăn mòn plasma có thể được tạm nhóm thành các quá trình ăn mòn điện môi, silicon hoặc dây dẫn. Các chất điện môi như silicon dioxide và silicon nitride được khắc tốt nhất bằng cách sử dụng khí flo hóa trong khi các lớp silicon và kim loại phản ứng tốt nhất với hóa chất clo. Về cơ bản có ba chế độ ăn mòn khô - ăn mòn ion phản ứng, ăn mòn plasma và ăn mòn phún xạ (chùm ion). Các quy trình khắc đều liên quan đến sự tương tác phức tạp giữa các chất phản ứng hóa học, plasma và vật liệu wafer. Khi phân cực RF được áp dụng cho khí phản ứng, các electron và ion tích điện dương sẽ bắn phá tấm wafer để loại bỏ (etch) vật liệu một cách vật lý trong khi các loại hóa chất và gốc tự do phản ứng với vật liệu tiếp xúc để tạo thành các sản phẩm phụ dễ bay hơi. Khắc có thể là đẳng hướng (phản ứng như nhau theo chiều dọc và chiều ngang), dị hướng (chỉ theo chiều dọc) hoặc ở đâu đó ở giữa.

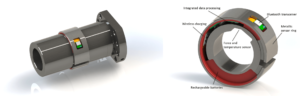

Hình 1: Sự chuyển đổi từ finFET sang GAA thúc đẩy các yêu cầu khắc chọn đẳng hướng quan trọng. Nguồn: Lâm Nghiên

Các chỉ số khắc mà các kỹ sư quan tâm nhất là tốc độ khắc, kiểm soát biên dạng, tính đồng nhất (trên tấm wafer) và tính chọn lọc của khắc, vì những điều này ảnh hưởng đến sản lượng và năng suất. Độ chọn lọc ăn mòn đơn giản là tỷ lệ loại bỏ vật liệu bạn muốn ăn mòn so với lớp bên dưới của nó – ví dụ, SiO2 trên silic. Trong quá trình khắc, cũng có lợi là không loại bỏ quá nhiều chất cản quang. Nhưng trong trường hợp đó, mẫu thường được chuyển sang mặt nạ cứng (silicon dioxide, silicon nitride, SiOC, TiN) trước khi nó được chuyển sang lớp phim bên dưới.

Thông số kỹ thuật chọn lọc thay đổi từ 2:1 lên đến 1,000:1 (etch chọn lọc cao). Với mỗi nút mới, các thông số kỹ thuật này sẽ chặt chẽ hơn. “Với việc EUV có hàm lượng NA cao sẽ bắt đầu thay thế EUV thông thường trong vòng 30 năm tới, tiêu điểm sẽ thấp hơn nhiều, vì vậy bạn không còn có thể phơi bày chất cản quang dày nữa – và theo ý tôi là độ dày là 2 nanomet,” Philippe Bézard, kỹ sư R&D khắc khô tại cho biết imec. “Nhưng bạn vẫn cần tạo mẫu có cùng độ dày màng bên dưới. Vì vậy, bây giờ bạn đang yêu cầu độ chọn lọc cao hơn nhiều theo nghĩa là thay vì 1:10, chúng tôi phải đạt tới tỷ lệ giống như 1:4, đây là một sự cải thiện đột ngột về độ chọn lọc từ 5X đến XNUMXX.”

Từ bằng chứng về khái niệm (POC) đến sản xuất khối lượng lớn (HVM)

Bézard mô tả ba giai đoạn phát triển quy trình etch:

- Xác định những gì máy ăn mòn, khí, lớp hỗ trợ, v.v., là cần thiết để thực hiện ăn mòn;

- Thể hiện hiệu suất trong việc loại bỏ hoàn toàn màng trong thông số kỹ thuật với tính đồng nhất của quy trình trên một tấm wafer và

- Xác định cách quy trình có thể được lặp lại trên hàng nghìn tấm wafer trong HVM với năng suất cao và độ lệch ít.

Thông thường, các kỹ sư tích hợp và etch lành nghề sẽ xử lý hai giai đoạn phát triển đầu tiên. Giai đoạn thứ ba một lần nữa có thể sử dụng chuyên môn kỹ thuật, nhưng học máy có thể hỗ trợ.

Ông nói: “Máy học và phân tích dữ liệu nói chung chỉ hữu ích trong giai đoạn thứ ba. “Nó rất mạnh mẽ vì nó có quyền truy cập vào rất nhiều dữ liệu và có thể hiểu được hàng triệu thứ nhỏ bé, đơn giản đang tương tác với nhau. Vì vậy, để bộ não con người cố gắng tìm ra điều này là rất khó, nhưng nó dễ quản lý hơn đối với một chương trình máy tính. Nhưng trong trường hợp bạn có một ứng dụng mới, vật liệu mới được khắc hoặc tích hợp mới, thì nó không cho thấy bất kỳ cải tiến nào so với con người.”

Việc sử dụng ML cũng liên quan đến chi phí sản xuất vì hàng nghìn tấm wafer được sử dụng trong giai đoạn ba — ít nhất là lớn hơn một bậc so với mức được sử dụng trong giai đoạn một và hai.

Barrett Finch, giám đốc cấp cao của Nhóm sản phẩm Etch tại Lam Research, mô tả quá trình tìm đường quy trình mới giống như lấy bằng chứng về khái niệm từ quy trình và bố cục quy trình danh nghĩa, đồng thời phát triển một hoặc nhiều thiết bị hoạt động trên một tấm wafer. POC này sau đó được chuyển đến nhóm phát triển sản phẩm trong xưởng để mở rộng quy trình và cải thiện năng suất.

Finch cho biết: “Khối lượng công việc cần thiết để biến một bằng chứng danh nghĩa thành một sản phẩm có năng suất khả thi thường bị đánh giá thấp và điều này tạo ra một khoảng cách lớn đối với khả năng sinh lời. “Mô hình hóa cửa sổ quy trình tìm cách thu hẹp khoảng cách này bằng cách đưa biến thể fab vào giai đoạn đầu của quá trình tìm đường R&D.” Ông gợi ý rằng các DOE ảo và phân tích dựa trên Monte Carlo trên một số tham số quy trình sẽ kiểm tra POC bằng cách mô phỏng độ biến thiên dự kiến.

“Mô hình hóa cửa sổ quy trình có thể trả lời câu hỏi, 'Tôi phải duy trì đĩa CD hoặc mức độ biến đổi nào để đạt được hiệu suất và năng suất thiết bị tối thiểu?' Ông nói: “Chúng tôi đã hoàn thành các thử nghiệm cửa sổ quy trình ảo với hơn 1 triệu tấm wafer ảo trong vài ngày, điều không thể thực hiện được trong đời thực”.

Nhiều tham số ảnh hưởng đến tốc độ khắc, biên dạng và độ chọn lọc. Một điều quan trọng là nhiệt độ. “Tác động của hiệu ứng nhiệt trong quá trình khắc được khách hàng của chúng tôi nhìn thấy khi họ kiểm soát tốc độ khắc, độ chọn lọc và cấu hình khắc. Tất cả các thông số này có thể ảnh hưởng đến cả năng suất thiết bị và năng suất fab,” Benjamin Vincent, quản lý cấp cao về quy trình bán dẫn và kỹ thuật tích hợp tại Lam Research cho biết. Ông cho rằng mô phỏng có thể đặc biệt hữu ích khi một bước quy trình có nhiều cấu hình khả thi (không gian quy trình lớn) hoặc khi kết quả xuôi dòng từ bước này rất khó đoán.

Alex Guermouche, giám đốc tiếp thị sản phẩm của Esgee Technologies, cho biết: “Quá trình ăn mòn phụ thuộc vào nhiệt độ bề mặt của tấm wafer, vốn phụ thuộc vào một số dòng nhiệt - bao gồm dẫn nhiệt, năng lượng va chạm ion, phản ứng bề mặt và dòng nhiệt bức xạ plasma”. Công ty Nghiên cứu Lâm. “Kết quả là, các mô hình plasma cần kết hợp tất cả các tính năng vật lý này để mô tả chính xác sự thay đổi nhiệt độ trên bề mặt của tấm wafer. Phần mềm mô phỏng quy trình có thể mô hình hóa một loạt các thuộc tính khắc, cho phép chúng tôi có được kết quả khắc tốt hơn nhanh hơn và đẩy nhanh khả năng tăng sản lượng hoặc tối ưu hóa năng suất của khách hàng.”

Thời gian chính xác của quá trình etch

Với hình học chặt chẽ hơn và màng mỏng hơn, cần phải cân bằng tốc độ ăn mòn với khả năng kiểm soát tốt các thông số vận hành khác.

Finch cho biết: “Với các quy tắc thiết kế được thu hẹp lại, nhiều quy trình etch đang chuyển sang các bước quy trình khắc plasma rất nhanh, đòi hỏi sự kiểm soát chính xác cao đối với tất cả các đầu vào phản ứng: năng lượng, áp suất, hóa học và nhiệt độ,” Finch cho biết, đồng thời lưu ý rằng cũng có xu hướng hướng tới plasma được tối ưu hóa. hành vi xung để tạo ra một tỷ lệ ion-trung tính cụ thể, sau đó quét sạch các sản phẩm phụ. “Mô hình hóa nâng cao của các điều kiện như vậy sẽ rất quan trọng để cho phép mở rộng quy mô thiết bị hơn nữa.”

Các nhà sản xuất hệ thống khắc đã sử dụng phần mềm lập mô hình trong một thời gian để tăng tốc độ phát triển nút tiếp theo hoặc năng suất dốc. Điều này không có gì ngạc nhiên, do tính phức tạp tuyệt đối của quy trình và tất cả các biến số của nó.

Finch cho biết: “Đơn giản là không có đủ thời gian hoặc đủ tấm wafer để thực hiện tất cả các thử nghiệm quy trình khả thi khi phát triển các công nghệ nút tiếp theo. “Số lượng kết hợp cài đặt thiết bị etch có thể lên tới hàng triệu, thậm chí hàng tỷ và việc phát triển wafer cưỡng bức bằng tất cả các khả năng của quy trình đơn giản là không thể.”

Tất nhiên, tất cả các mô hình tốt đều được xác minh trên chip thực tế. Finch cho biết: “Một mô hình chính xác phải có tính dự đoán và nó sẽ giải quyết vấn đề được nhắm mục tiêu mà người dùng muốn giải quyết. “Mỗi khi một quy trình hoặc thay đổi thiết kế được khuyến nghị dựa trên công việc mô phỏng, dữ liệu fab thực tế sẽ phản ánh kết quả của khuyến nghị. Trong trường hợp của chúng tôi, chúng tôi đã có thể dự đoán chính xác tác động của các thay đổi quy trình bằng cách sử dụng các kết quả dựa trên mô hình và nhanh chóng giải quyết các vấn đề phát triển công nghệ và quy trình khó.”

Các nhà cung cấp công cụ cũng đang làm việc trên các quy trình khắc tiên tiến để tích hợp chặt chẽ hơn các dây chuyền và biến quy trình từng là quy trình cấp độ hai mặt nạ (hai bước in thạch bản) thành một quy trình để đơn giản hóa quy trình và giảm chi phí.

Bézard cho biết: “Thay vì điều chỉnh phần cứng hiện có để làm cho con dao của Quân đội Thụy Sĩ được trang bị nhiều hơn, các công ty đang giới thiệu các công nghệ dành riêng cho ứng dụng, chẳng hạn như các hệ thống mới để giải quyết các vấn đề từ đầu đến cuối. Mục đích là làm cho hai đường đối diện nhau gần nhau hơn, hiện bao gồm bước tạo đường kẻ, sau đó là mặt nạ cắt. “Những gì Vật liệu ứng dụng và những thứ khác đang giới thiệu là một cách khắc trực tiếp theo hướng nằm ngang.” Các quy trình như vậy cũng có thể mở rộng thông qua các lỗ.

Các bước khắc cho FET nanosheet

Các bước khắc quan trọng nhất trong nanô các luồng quy trình bao gồm etch cổng giả, etch cột bất đẳng hướng, etch miếng đệm đẳng hướng và bước giải phóng kênh. [1] Cấu hình ăn mòn thông qua các lớp silicon và SiGe xen kẽ là không đẳng hướng và sử dụng hóa học flo hóa. Bước khắc (vết lõm) và giải phóng kênh bên trong được tối ưu hóa để loại bỏ SiGe với tổn thất silicon cực thấp.

Bước phát hành kênh là rất quan trọng. Bézard cho biết: “Việc phát hành tấm nano đòi hỏi tính chọn lọc cực cao. “Hầu hết các tấm nano là silicon, sau đó là silicon-gecmani và silicon. Bạn có các lớp xen kẽ và bạn cần xóa một lớp mà không sửa đổi lớp kia.” Một số ấn phẩm đã thảo luận về việc thực hiện ăn mòn SiGe nhiều bước để giảm ứng suất cho cấu trúc gây ra bởi một bước ăn mòn duy nhất.

Tiếp theo trong quá trình này là sự hình thành các liên hệ tự liên kết. “Ở đây, những gì chúng tôi đang cố gắng thực hiện về cơ bản là ăn mòn silicon dioxide và không chạm hoặc lõm silicon nitride. Bézard cho biết thông số kỹ thuật hiện tại là 3nm, nhưng mọi người đang yêu cầu độ hao hụt bằng không. “Trong trường hợp này, chúng tôi thậm chí không sử dụng từ chọn lọc. Chúng tôi chỉ nói về giờ ra chơi – và không có giờ giải lao nào cả.”

NỀN TẢNG

Trong NỀN TẢNG flash, số lớp tiếp tục tăng lên và đòi hỏi phải áp dụng nhiều lớp xếp chồng lên nhau trong tương lai, cuối cùng tạo ra các chuỗi thiết bị xếp chồng lên nhau theo chiều dọc. Robert Clark, thành viên cấp cao của nhân viên kỹ thuật và cho biết: “Ngoài ra, có rất nhiều nỗ lực để tăng tỷ lệ cao độ của dòng từ hoặc cao độ dọc/Z của các lớp khi số lượng lớp tăng lên để tiếp tục tăng mật độ bit. giám đốc công nghệ tại Điện thoại. “Từ góc độ quy trình, các quy trình ăn mòn và lắng đọng sẽ cần cải tiến liên tục để phù hợp với tỷ lệ khung hình ngày càng cao ở các kích thước tới hạn ngày càng nhỏ hơn mà quy mô tiếp tục đòi hỏi.”

Clark mô tả những thay đổi trong tương lai. “Hướng tới các nút nâng cao của thiết bị bẫy điện tích có nhiều tầng, kỹ thuật ngăn xếp cổng sẽ được yêu cầu để đạt được độ dài cổng ngắn hơn, nhiều cấp hơn trên mỗi ô và hiệu quả lập trình được cải thiện — có khả năng thông qua việc sử dụng vật liệu high-k. Các kênh có độ dẫn điện cao hơn cũng có thể sẽ được yêu cầu để thay thế các kênh poly-Si trong tương lai,” ông nói.

Một trong những quá trình khắc quan trọng nhất trong 3D NAND liên quan đến việc khắc sâu các lỗ có kích thước khoảng 100nm thông qua các ngăn oxit-nitrit đa lớp (hơn 200 lớp), có thể sâu tới 10µm. Bézard của Imec cho biết bước khắc này là một bước đặc biệt tốn kém.

Ông nói: “Chúng tôi có một hiện tượng vật lý xảy ra, được gọi là hiệu ứng tích điện chênh lệch. “Trong plasma, chúng ta có các electron, ion và các loại trung tính để đơn giản hóa rất nhiều. Các electron di chuyển theo mọi hướng, nhưng các ion được gia tốc vuông góc với bề mặt. Vì vậy, bạn có điện tích dương ở đáy lỗ và điện tích âm ở trên cùng, và bạn nhận được một điện trường đang cố gắng đẩy các ion đi tới.”

Do đó, cần có mức năng lượng cao để khắc hoàn toàn rãnh. Ông nói: “Chúng tôi đang cố gắng duy trì công suất từ 30 đến 50 gigawatt mà không cần phóng điện hồ quang, vì vậy mâm cặp phải được đánh bóng và sản xuất cực kỳ tốt.

Các vết khắc sâu cũng tạo ra các ứng suất cần được giảm thiểu, đặc biệt là do quá trình chế tạo NAND nhiều tầng sau đó yêu cầu làm mỏng tấm wafer, căn chỉnh chính xác và liên kết lai với tầng tiếp theo.

quy trình khác

Không phải tất cả các nhà sản xuất chip đều sản xuất chip hàng đầu yêu cầu kỹ thuật in khắc EUV. Nhiều nhà chế tạo đang mở rộng quy trình in khắc và in khắc 193nm của họ.

Brian Wilbur, giám đốc đa dạng hóa sản phẩm bán dẫn tại Khoa học nấu bia.

BEOL đối với các dòng kim loại chặt chẽ nhất dự kiến sẽ trải qua quá trình chuyển đổi mạnh mẽ từ sơ đồ tích hợp damascene kép sang lắng đọng trừ và ăn mòn các kết nối khác ngoài đồng. Ở đây, hai kim loại — rutheni và molypden — đã được phát triển triệt để nhất. Tuy nhiên, molypden có nhiều khả năng bị oxy hóa hơn trong quá trình ăn mòn, làm cho nó tương thích hơn với sơ đồ damascene kép. Ruthenium là một kim loại quý nên nó không có các vấn đề ăn mòn tương tự, nhưng nó đắt hơn.

Cấu trúc thiết bị cũng đang trở nên không dung nạp được lỗi vị trí cạnh. Theo Clark của TEL, sẽ cần có các kế hoạch mới để tự liên kết từ lớp này sang lớp khác và giữa các vias và lines. “Việc triển khai đầu tiên có thể sẽ dành cho những thứ như dòng chữ bị chôn vùi trong DRAM và các lớp kim loại MOL có bước sóng nhỏ dành cho logic khi cần có độ ổn định nhiệt cao hơn cũng như điện trở suất thấp hơn hoặc kim loại không có lớp lót.”

Phát triển thế hệ tiếp theo

Về lâu dài, lý tưởng nhất là ngành sẽ chuyển đổi sang các quy trình back-end có ngân sách nhiệt thấp hơn (gần 300°C hơn 400°C) để tích hợp các thiết bị vào các lớp kết nối phía sau.

Clark của TEL cho biết: “Ngành công nghiệp thực sự có nhu cầu bắt đầu xây dựng các thiết bị thành nhiều lớp hơn. “Điều đó có nghĩa là chúng tôi cần các thiết bị logic và bộ nhớ được tích hợp trong BEOL với ngân sách nhiệt BEOL.”

Cho đến nay, các thiết bị được tạo ra bằng cách sử dụng oxit bán dẫn có vẻ đầy hứa hẹn, cho cả việc tích hợp các thiết bị bộ nhớ vào luồng BEOL logic hoặc để xây dựng các mảng CMOS trên đỉnh mảng bộ nhớ trong DRAM.

Một sự thay đổi đáng kể khác liên quan đến việc tích hợp các vật liệu 2D, mà các nhà nghiên cứu và nhà sản xuất chip hàng đầu đã bắt đầu thử nghiệm. Các quy trình ăn mòn cho các vật liệu như vonfram disulfua hoặc molypden disulfide đang được xem xét. Các bộ phim bao gồm một lớp vật liệu đơn nên việc phát triển các quy trình fab để tích hợp chúng là vô cùng khó khăn.

Tính bền vững

Các nhà sản xuất chip và nhà cung cấp vật liệu đang theo đuổi các hóa chất thay thế để giảm lượng khí thải carbon. Trong khắc, thủ phạm chính là khí flo có tiềm năng nóng lên toàn cầu cao.

Bézard của imec cho biết: “Lý do tại sao bạn có PFOS (axit perfluorooctane sulfonic) lại có vấn đề là do phân tử này quá ổn định. “Ánh sáng hoặc phản ứng hóa học trong khí quyển không đủ để phá vỡ nó.”

Ông cho biết một số hỗn hợp khí thay thế có hàm lượng oxy cao hơn sẽ dễ dàng phân tách hơn và có GWP thấp hơn. “Tuy nhiên, bất kỳ ứng cử viên nào cũng phải thể hiện tốt hoặc thậm chí cao hơn để bắt đầu.”

Nhưng tính bền vững không đặc biệt là một thách thức ăn mòn hoặc lắng đọng. Đó là một thách thức toàn diện trong ngành từ in thạch bản cho đến đóng gói, trong đó tác động của vật liệu mới ảnh hưởng đến toàn bộ quá trình xử lý thiết bị.

Tài liệu tham khảo

1. K. Derbyshire, “Có gì khác biệt về bóng bán dẫn thế hệ tiếp theo”, Kỹ thuật bán dẫn, ngày 20 tháng 2022 năm XNUMX.

Liên quan đến chuyện

Cuộn ra có chọn lọc cao cho chip thế hệ tiếp theo

Sản xuất cấu trúc 3D sẽ yêu cầu kiểm soát cấp độ nguyên tử đối với những gì bị loại bỏ và những gì còn lại trên tấm wafer.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- Mua và bán cổ phần trong các công ty PRE-IPO với PREIPO®. Truy cập Tại đây.

- nguồn: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- Vật liệu 2D

- 30

- 3d

- 50

- a

- có khả năng

- Có khả năng

- Giới thiệu

- đẩy nhanh tiến độ

- tăng tốc

- truy cập

- chứa

- hoàn thành

- Theo

- chính xác

- chính xác

- ngang qua

- thực tế

- địa chỉ

- Nhận con nuôi

- tiên tiến

- thuận lợi

- ảnh hưởng đến

- một lần nữa

- nhằm mục đích

- alex

- Tất cả

- Cho phép

- Đã

- Ngoài ra

- thay thế

- số lượng

- an

- phân tích

- và

- Một

- trả lời

- bất kì

- xuất hiện

- Các Ứng Dụng

- ứng dụng cụ thể

- áp dụng

- LÀ

- Quân đội

- Mảng

- AS

- khía cạnh

- hỗ trợ

- At

- Bầu không khí

- thuộc tính

- xa

- Back-end

- Cân đối

- dựa

- Về cơ bản

- BE

- Chùm tia

- bởi vì

- trở thành

- được

- trước

- Bắt đầu

- được

- phía dưới

- cây bồ đề

- BEST

- Hơn

- giữa

- thiên vị

- lớn

- tỷ

- Một chút

- cả hai

- đáy

- ranh giới

- Brain

- Nghỉ giải lao

- Brian

- bạo lực

- ngân sách

- Ngân sách

- Xây dựng

- xây dựng

- nhưng

- by

- gọi là

- CAN

- ứng cử viên

- carbon

- lượng khí thải carbon

- mà

- trường hợp

- trường hợp

- CD

- Tế bào

- thách thức

- thách thức

- phòng

- thay đổi

- Những thay đổi

- Kênh

- kênh

- phí

- tính phí

- tải

- sạc

- hóa chất

- hóa chất

- hóa học

- Snacks

- Làm sạch

- Đóng

- chặt chẽ

- gần gũi hơn

- kết hợp

- Các công ty

- công ty

- tương thích

- hoàn thành

- Hoàn thành

- phức tạp

- phức tạp

- máy tính

- khái niệm

- điều kiện

- độ dẫn

- dẫn

- xem xét

- không thay đổi

- Liên hệ

- nội dung

- tiếp tục

- tiếp tục

- liên tiếp

- điều khiển

- Copper

- Doanh nghiệp

- ăn mòn

- Phí Tổn

- giảm chi phí

- Chi phí

- có thể

- khóa học mơ ước

- tạo

- tạo ra

- Tạo

- quan trọng

- Current

- Hiện nay

- khách hàng

- Cắt

- dữ liệu

- phân tích dữ liệu

- khoa học dữ liệu

- Ngày

- sâu

- cung cấp

- mật độ

- phụ thuộc

- mô tả

- Thiết kế

- phát triển

- phát triển

- Phát triển

- thiết bị

- Thiết bị (Devices)

- khác nhau

- khó khăn

- kích thước

- hướng

- trực tiếp

- Giám đốc

- thảo luận

- đa dạng hóa

- do

- làm

- đô la

- xuống

- đáng kể

- lái xe

- khô

- suốt trong

- mỗi

- Đầu

- dễ dàng

- hiệu lực

- hiệu ứng

- hiệu quả

- hay

- Điện

- điện tử

- Phát thải

- cho phép

- ky sư

- Kỹ Sư

- Kỹ sư

- đủ

- như nhau

- Trang thiết bị

- đã trang bị

- Tương đương

- đặc biệt

- thiết yếu

- chủ yếu

- vv

- Ngay cả

- cuối cùng

- Mỗi

- chính xác

- Kiểm tra

- thi hành

- hiện tại

- dự kiến

- đắt tiền

- thí nghiệm

- chuyên môn

- tiếp xúc

- mở rộng

- cực kỳ

- phải đối mặt với

- xa

- NHANH

- nhanh hơn

- Tính năng

- vài

- lĩnh vực

- Hình

- Phim ảnh

- phim

- Tên

- Đèn flash

- dòng chảy

- Chảy

- Tập trung

- sau

- tiếp theo

- Trong

- Buộc

- hình thức

- hình thành

- Forward

- 4

- Miễn phí

- từ

- đầy đủ

- xa hơn

- tương lai

- khoảng cách

- GAS

- Tổng Quát

- tạo ra

- được

- được

- Toàn cầu

- sự nóng lên toàn cầu

- mục tiêu

- tốt

- tuyệt vời

- Nhóm

- Phát triển

- Phát triển

- Một nửa

- xử lý

- Cứng

- phần cứng

- Có

- he

- hữu ích

- tại đây

- Cao

- Năng suất cao

- cao hơn

- cao

- Lô

- Holes

- toàn diện

- Ngang

- nhà

- Độ đáng tin của

- Tuy nhiên

- HTTPS

- Nhân loại

- Con người

- Hàng trăm

- Hỗn hợp

- i

- Va chạm

- không thể

- nâng cao

- cải thiện

- cải thiện

- in

- bao gồm

- Bao gồm

- Incoming

- kết hợp

- tăng

- ngành công nghiệp

- đầu vào

- ví dụ

- thay vì

- tích hợp

- Tích hợp

- hội nhập

- tương tác

- tương tác

- kết nối

- trong

- giới thiệu

- các vấn đề

- IT

- ITS

- jpg

- chỉ

- Key

- Lâm

- lớn

- lớn hơn

- lớp

- lớp

- Bố trí

- hàng đầu

- học tập

- ít nhất

- Cấp

- niveaux

- Cuộc sống

- Lượt thích

- Có khả năng

- Dòng

- dòng

- LITHO

- ít

- logic

- còn

- Xem

- sự mất

- Rất nhiều

- Thấp

- máy

- học máy

- thực hiện

- Chủ yếu

- duy trì

- làm cho

- Các nhà sản xuất

- Làm

- giám đốc

- sản xuất

- nhà chế tạo

- sản xuất

- nhiều

- thị trường

- Marketing

- Giám đốc tiếp thị

- mặt nạ

- vật liệu

- nguyên vật liệu

- max-width

- Có thể..

- nghĩa là

- có nghĩa

- hội viên

- Bộ nhớ

- kim loại

- Kim loại

- Metrics

- Might

- triệu

- hàng triệu

- tối thiểu

- mất tích

- kiểu mẫu

- người mẫu

- mô hình

- chế độ

- MOL

- phân tử

- tháng

- chi tiết

- hầu hết

- di chuyển

- di chuyển

- nhiều

- nhiều

- gần

- Cần

- cần thiết

- nhu cầu

- tiêu cực

- Neutral

- Mới

- tiếp theo

- Không

- Noble

- nút

- các nút

- tại

- con số

- Tháng Mười

- of

- thường

- on

- hàng loạt

- ONE

- có thể

- hoạt động

- Hoạt động

- tối ưu hóa

- Tối ưu hóa

- tối ưu hóa

- or

- gọi món

- Nền tảng khác

- Khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- ra

- kết thúc

- Ôxy

- bao bì

- thông số

- riêng

- đặc biệt

- Họa tiết

- người

- thực hiện

- hiệu suất

- biểu diễn

- có lẽ

- quan điểm

- giai đoạn

- hiện tượng

- Philippe

- vật lý

- Thể chất

- Vật lý

- cột

- Pitch

- quan trọng

- Plasma

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- đóng

- PoC

- tích cực

- khả năng

- có thể

- có thể

- tiềm năng

- có khả năng

- quyền lực

- mạnh mẽ

- cần

- Độ chính xác

- dự đoán

- Chủ tịch

- áp lực

- Vấn đề

- vấn đề

- quá trình

- Quy trình

- xử lý

- sản xuất

- Sản phẩm

- phát triển sản phẩm

- Sản lượng

- năng suất

- Sản phẩm

- Hồ sơ

- Profiles

- lợi nhuận

- chương trình

- Lập trình

- hứa hẹn

- bằng chứng

- bằng chứng về khái niệm

- ấn phẩm

- Đẩy

- câu hỏi

- Mau

- R & D

- Giốc

- phạm vi

- Tỷ lệ

- Giá

- tỉ lệ

- đạt

- Phản ứng

- phản ứng

- phản ứng

- thực

- đời thực

- lý do

- gần đây

- Khuyến nghị

- đề nghị

- giảm

- giảm

- giảm

- phản ánh

- đều đặn

- phát hành

- đáng tin cậy

- dựa

- loại bỏ

- tẩy

- Đã loại bỏ

- loại bỏ

- có thể lặp lại

- lặp đi lặp lại

- thay thế

- báo cáo

- yêu cầu

- cần phải

- Yêu cầu

- đòi hỏi

- nghiên cứu

- kết quả

- Kết quả

- Tiết lộ

- ngay

- ROBERT

- Vai trò

- dạng cuộn

- khoảng

- quy tắc

- chạy

- Nói

- tương tự

- nói

- Quy mô

- mở rộng quy mô

- đề án

- Khoa học

- Tìm kiếm

- đã xem

- chọn lọc

- bán dẫn

- cao cấp

- ý nghĩa

- thiết lập

- một số

- thay đổi

- nên

- Silicon

- Đơn giản

- đơn giản hóa

- đơn giản

- mô phỏng

- duy nhất

- lành nghề

- nhỏ

- So

- Phần mềm

- Giải pháp

- động SOLVE

- một số

- một nơi nào đó

- nguồn

- Không gian

- riêng

- thông số kỹ thuật

- thông số kỹ thuật

- tốc độ

- Tính ổn định

- ổn định

- xếp chồng lên nhau

- Stacks

- Nhân sự

- giai đoạn

- Bắt đầu

- bắt đầu

- Bước

- Các bước

- Vẫn còn

- căng thẳng

- cấu trúc

- Sau đó

- đáng kể

- như vậy

- đột ngột

- đủ

- Gợi ý

- nhà cung cấp

- Bề mặt

- bất ngờ

- Tính bền vững

- bền vững

- Sweep

- Thụy Sĩ

- hệ thống

- Hãy

- dùng

- Thảo luận

- nhắm mục tiêu

- nhóm

- Kỹ thuật

- Công nghệ

- Công nghệ

- Sự phát triển công nghệ

- kỳ hạn

- thử nghiệm

- Kiểm tra

- kiểm tra

- hơn

- việc này

- Sản phẩm

- Tương lai

- cung cấp their dịch

- Them

- sau đó

- Đó

- nhiệt

- Kia là

- họ

- điều

- Thứ ba

- điều này

- triệt để

- hàng ngàn

- số ba

- Thông qua

- tầng

- chặt chẽ hơn

- thời gian

- thời gian

- đến

- bên nhau

- tấn

- TẤN

- quá

- hàng đầu

- chạm

- đối với

- chuyển

- Chuyển đổi

- quá trình chuyển đổi

- khuynh hướng

- thử

- hai

- điển hình

- thường

- cơ bản

- không thể đoán trước

- trên

- trở lên

- us

- sử dụng

- đã sử dụng

- người sử dang

- sử dụng

- sử dụng

- xác minh

- thẳng đứng

- theo chiều dọc

- rất

- thông qua

- khả thi

- Phó Chủ Tịch

- vincent

- ảo

- Dễ bay hơi

- muốn

- muốn

- là

- Đường..

- we

- tuần

- TỐT

- Điều gì

- khi nào

- liệu

- cái nào

- trong khi

- toàn bộ

- tại sao

- sẽ

- với

- ở trong

- không có

- Từ

- Công việc

- đang làm việc

- công trinh

- sẽ

- năm

- năm

- Năng suất

- năng suất

- sản lượng

- bạn

- zephyrnet

- không