Trong hoạt động của thiết bị CPU hiện đại, 80% đến 90% mức tiêu thụ năng lượng và độ trễ thời gian là do chuyển động dữ liệu giữa CPU và bộ nhớ ngoài chip. Để giảm bớt mối lo ngại về hiệu năng này, các nhà thiết kế đang bổ sung thêm bộ nhớ trên chip cho CPU của họ. Theo truyền thống, SRAM là loại bộ nhớ CPU trên chip được sử dụng rộng rãi nhất. Thật không may, SRAM hiện bị giới hạn ở kích thước hàng trăm megabyte. Hạn chế bộ nhớ trên chip này có thể không đủ cho các ứng dụng hàng đầu.

Các ứng dụng CPU trong tương lai, chẳng hạn như lập trình Mô hình ngôn ngữ AI và xử lý hình ảnh cho video 8K UHD, sẽ yêu cầu băng thông truy cập bộ nhớ I/O trong khoảng 10 terabyte/giây. Để đáp ứng các yêu cầu về băng thông này, bộ nhớ CPU trên chip sẽ cần có kích thước lớn hơn 1 terabyte. Có thể cần một giải pháp thay thế SRAM để đáp ứng các yêu cầu về bộ nhớ trên chip trong tương lai. Một giải pháp khả thi cho vấn đề này là sử dụng Bộ nhớ truy cập ngẫu nhiên điện trở (ReRAM). [1,2,3]

Thiết bị ReRAM là một ô nhớ cố định có chứa vật liệu điện trở nhớ. Những vật liệu này hoạt động như một chất cách điện. Khi đặt một điện áp đủ cao, đường dẫn sẽ được hình thành. Các vật liệu bộ nhớ điển hình được sử dụng làm điện trở nhớ bao gồm HfO2, Tạ2O5và TiO2. [4] Trạng thái điện trở của ô nhớ có thể được đọc bằng cách sử dụng các mạch điện tử để xác định xem ô nhớ đã được lập trình hay bị xóa hay chưa, từ đó xác định trạng thái của bit bộ nhớ. Các ô nhớ ReRAM có thể được xếp chồng lên nhau theo chiều dọc, giống như kiến trúc 3D-NAND, để tăng mật độ lưu trữ.

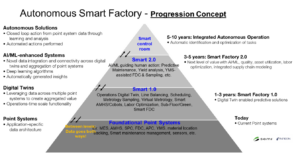

Trong bài viết này, Chế tạo ảo SEMulator3D sẽ được sử dụng để tìm đường dẫn quy trình và trực quan hóa các kiến trúc ReRAM 3D tiềm năng. Chúng tôi sẽ ước tính điện trở của ô như một hàm của hình dạng ô nhớ, cùng với hiệu suất Id-Vg của bóng bán dẫn kênh nhúng trong thiết bị ReRAM.

Mô hình 3D ReRAM được hiển thị trong hình 1. Thiết bị có 64 lớp wordline (WL) với các cột được đặt trong một mảng cách đều nhau hình lục giác. Các dòng từ được hình thành với các lớp dây dẫn kim loại và chất điện môi oxit xen kẽ. Các cột được khắc qua WL và sau đó một lớp vật liệu bộ nhớ mỏng được đặt lên các thành bên của cột. Vật liệu bộ nhớ được loại bỏ khỏi phần dưới và phần trên của cột, chỉ để lại vật liệu ở thành bên của cột. Các cột trụ sau đó được lấp đầy bằng kim loại chịu lửa và vonfram.

Bên dưới các lớp mảng là các điểm tiếp xúc và kim loại kết nối với nguồn, cống và cổng của các bóng bán dẫn hiệu ứng trường toàn cổng (GAA FET). Cống bóng bán dẫn kết nối với trụ mảng bộ nhớ và kết hợp với mạch WL để cung cấp chức năng cho từng ô nhớ.

Ô nhớ bao gồm hai điện cực kim loại: đường dây dẫn kim loại và điện cực kim loại chịu lửa (hình 2). Trong quá trình mô phỏng quy trình ảo của thiết bị này, chúng tôi sẽ sử dụng các biến quy trình để thiết lập và đặt lại memristor. Một điện áp được áp dụng có chủ ý sẽ tạo ra những đường dẫn cực nhỏ gọi là dây dẫn điện. Khi các tín hiệu điện có cực tính khác nhau được đưa vào, các ion tích điện bên trong memristor sẽ di chuyển để tạo thành (đặt) hoặc hòa tan (đặt lại) dây tóc dẫn điện.

Điện trở dây tóc dẫn điện thay đổi ở các điện áp chương trình khác nhau. Trạng thái điện trở thấp nằm trong khoảng 10k ohm (đặt lại) và trạng thái điện trở cao nằm trong khoảng 1M ohm (đặt lại). [5] Chúng tôi đã phát triển một mô hình ảo để chứng minh điện trở chuyển mạch của thiết bị 3D ReRAM, với kết quả được hiển thị trong hình 3. Trạng thái điện trở cao của điện trở nhớ có điện trở cao hơn khoảng 100 lần so với trạng thái điện trở thấp.

Sau đó, Thiết kế thí nghiệm ảo (DOE) đã được thực thi để hiểu rõ hơn mối tương quan giữa tỷ lệ điện trở của ô nhớ với kích thước và hình dạng của ô nhớ. Các biến của thí nghiệm là trụ CD, độ dày WL và độ dày điện trở nhớ. Phân tích kết quả DOE chỉ ra rằng CD trụ và độ dày của điện trở nhớ dẫn đến phản hồi đáng kể nhất. Hình 4 hiển thị biểu đồ đường viền của tỷ lệ điện trở của ô nhớ so với hai biến này. Có sự thay đổi gấp 3 lần về điện trở của tế bào bộ nhớ đối với các giá trị cao về bán kính trụ và độ dày điện trở nhớ. Sự khác biệt về hình dạng của ô nhớ trong phạm vi được nghiên cứu sẽ không ảnh hưởng đến khả năng đọc trạng thái bộ nhớ của điện trở nhớ nhưng có thể ảnh hưởng đến khả năng phân biệt trạng thái chương trình trong multibit trên mỗi thiết bị ô.

Memristor có thể được lập trình bằng dòng điện < 0.10 uA và điện áp < 0.5V. Các cài đặt điện áp và dòng điện này sẽ cho phép các memristor (bộ nhớ ReRAM) dễ dàng tích hợp dưới dạng bộ nhớ trên chip vào các thiết bị logic tiên tiến. Mô phỏng thiết bị SEMulator3D trước đây đã chứng minh rằng bóng bán dẫn dưới mảng GAA FET có thể điều khiển điện áp và dòng điện theo yêu cầu của trạng thái đặt và đặt lại của ô nhớ điện trở nhớ. [6]

Hai vấn đề chính của các thiết bị CPU hiện đại là tiêu thụ năng lượng và thời gian trễ do chuyển động dữ liệu giữa CPU và bộ nhớ ngoài chip. Việc tăng kích thước bộ nhớ trên chip có thể giải quyết được những vấn đề này. Trong nghiên cứu này, chúng tôi đã sử dụng SEMulator3D để nghiên cứu việc tích hợp giải pháp thay thế SRAM (ReRAM) cho CPU cho bộ nhớ trên chip. Chúng tôi đã sử dụng mô hình ảo để hiểu rõ hơn các bước của quy trình và các vấn đề tiềm ẩn về bố cục đối với từng tế bào điện trở nhớ riêng lẻ. Chúng tôi cũng thực hiện các nghiên cứu để kiểm tra trạng thái thiết lập và thiết lập lại của điện trở nhớ cũng như ảnh hưởng của kích thước thiết bị (hình dạng và kích thước ô nhớ) đến điện trở dòng từ. Chúng tôi đã nhấn mạnh rằng bộ nhớ trên bo mạch ReRAM có thể được tích hợp với logic nâng cao bằng cách sử dụng đầu ra điện của bóng bán dẫn GAA pFET để thiết lập và đặt lại các ô điện trở nhớ. Những kết quả này xác nhận rằng Bộ nhớ truy cập ngẫu nhiên điện trở (ReRAM) là giải pháp thay thế đầy hứa hẹn cho bộ nhớ SRAM tích hợp cho các ứng dụng logic băng thông cao trong tương lai.

dự án

- Lanza, Mario (2014). “Đánh giá về chuyển mạch điện trở trong chất điện môi K cao: Quan điểm cấp nano sử dụng kính hiển vi lực nguyên tử dẫn điện”. Tài liệu, tập. 7, số 3, trang 2155-2182, doi:10.3390/ma7032155.

- N. Sedghi và cộng sự, “Vai trò của pha tạp nitơ trong ALD Ta2O5 và ảnh hưởng của nó đối với việc chuyển đổi tế bào đa cấp trong RRAM”, tháng 2017 năm 10.1063, Thư Vật lý Ứng dụng, DOI:1.4978033/XNUMX

- Y. Bai, Et Al, “Nghiên cứu các đặc tính đa cấp cho bộ nhớ chuyển mạch điện trở dọc 3D” Báo cáo khoa học tập 4, Số bài viết: 5780 (2014)

- Chen, YC, Sarkar, S., Gibbs, JG, Huang, Y., Lee, JC, Lin, CC, & Lin, CH (2022). “Bộ nhớ điện trở kép chức năng hình xoắn ốc Nano dành cho ứng dụng mảng thanh ngang công suất thấp.”, Vật liệu kỹ thuật ứng dụng ACS, 1(1), 252-257.

- Y. Wu, et al, “HfOx RRAM quy mô nanomet”, Thư thiết bị điện tử IEEE, Tập: 34, Số phát hành: 8, tháng 2013 năm 10.1109), doi:2013.2265404/LED.XNUMX

- V. Sreenivasulu và cộng sự, “Phân tích mạch và tối ưu hóa FET dây nano GAA hướng tới công suất thấp và chuyển mạch cao”, ngày 11 tháng 2021 năm 10.1007, Khoa học máy tính, doi:12633/s022-01777-6-XNUMX.

Brett Lowe

Brett Lowe là người quản lý nhóm tích hợp và quy trình bán dẫn tại Coventor, một Công ty nghiên cứu của Lam. Ông đã làm việc trong lĩnh vực phát triển công nghệ bán dẫn hơn 35 năm. Ông bắt đầu sự nghiệp của mình tại Philips Semiconductors, nơi ông làm việc trong lĩnh vực sản xuất và phát triển quy trình với tư cách là kỹ sư quy trình trong lĩnh vực quang khắc, ăn mòn khô và quy trình ướt. Sau đó, ông dành tám năm tại Zilog, làm việc về phát triển quy trình đơn vị. Sau đó, Brett gia nhập Micron Technology, nơi anh làm việc trong lĩnh vực phát triển và tích hợp quy trình DRAM và 3D NAND. Tại Coventor, trọng tâm của anh là hỗ trợ khách hàng của công ty đáp ứng các yêu cầu phát triển công nghệ và mô hình hóa quy trình bán dẫn 3D của họ.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- : có

- :là

- :không phải

- :Ở đâu

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35%

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- có khả năng

- Có khả năng

- truy cập

- ngang qua

- Hành động

- thêm

- thêm vào

- tiên tiến

- ảnh hưởng đến

- AI

- AL

- Tất cả

- Tất cả bài viết

- giảm bớt

- cho phép

- dọc theo

- Ngoài ra

- thay thế

- an

- phân tích

- và

- Các Ứng Dụng

- các ứng dụng

- áp dụng

- khoảng

- kiến trúc

- LÀ

- khu vực

- Mảng

- bài viết

- AS

- At

- nguyên tử

- Tháng Tám

- b

- Băng thông

- BE

- được

- bắt đầu

- Hơn

- giữa

- Một chút

- Đen

- đáy

- nâu

- Bó lại

- nhưng

- by

- gọi là

- CAN

- Tuyển Dụng

- gây ra

- CD

- pin

- Tế bào

- Trung tâm

- thay đổi

- Kênh

- đặc điểm

- tính phí

- kết hợp

- công ty

- Của công ty

- so

- máy tính

- Khoa học Máy tính

- Liên quan

- dẫn

- Xác nhận

- connect

- bao gồm

- tiêu thụ

- Liên hệ

- chứa

- Tương quan

- có thể

- CPU

- tạo

- tạo ra

- Vượt qua

- Current

- Hiện nay

- khách hàng

- tối

- dữ liệu

- chậm trễ

- sự chậm trễ

- chứng minh

- chứng minh

- mật độ

- ký gửi

- Thiết kế

- thiết kế

- Xác định

- phát triển

- phát triển

- Phát triển

- thiết bị

- Thiết bị (Devices)

- sự khác biệt

- sự khác biệt

- khác nhau

- kích thước

- phân biệt

- hiển thị

- màn hình

- DOE

- mương

- vẽ

- lái xe

- khô

- suốt trong

- E&T

- mỗi

- dễ dàng

- Cạnh

- hiệu lực

- tám

- điện tử

- nhúng

- năng lượng

- Tiêu thụ năng lượng

- ky sư

- Kỹ Sư

- ước tính

- Ether (ETH)

- kiểm tra

- Thực thi

- thử nghiệm

- thí nghiệm

- FET

- lĩnh vực

- Hình

- đầy

- Tập trung

- Trong

- Buộc

- hình thức

- hình thành

- các hình thức

- tìm thấy

- từ

- chức năng

- tương lai

- cửa khẩu

- Gates

- thế hệ

- đồ thị

- lớn hơn

- màu xanh lá

- Có

- he

- Cao

- cao hơn

- Nhấn mạnh

- của mình

- HTTPS

- huang

- Hàng trăm

- ID

- xác định

- IEEE

- if

- hình ảnh

- in

- bao gồm

- Tăng lên

- tăng

- chỉ

- hệ thống riêng biệt,

- ảnh hưởng

- trong

- tích hợp

- tích hợp

- hội nhập

- trong

- điều tra

- vấn đề

- ITS

- gia nhập

- Lâm

- Ngôn ngữ

- một lát sau

- lớp

- lớp

- Bố trí

- hàng đầu

- học tập

- để lại

- Lee

- trái

- Lượt thích

- Hạn chế

- lin

- logic

- Thấp

- máy

- học máy

- chính

- giám đốc

- sản xuất

- Tháng Ba

- Mario

- vật liệu

- nguyên vật liệu

- max-width

- Có thể..

- Gặp gỡ

- Bộ nhớ

- kim loại

- micron

- kiểu mẫu

- người mẫu

- hiện đại

- chi tiết

- hầu hết

- di chuyển

- phong trào

- Cần

- cần thiết

- tiếp theo

- Tháng mười một

- con số

- of

- OM

- on

- ONE

- có thể

- hoạt động

- tối ưu hóa

- or

- Nền tảng khác

- đầu ra

- con đường

- đường dẫn

- mỗi

- hiệu suất

- Philips

- Vật lý

- cột

- trụ cột

- Hồng

- đặt

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Điểm

- Quan điểm

- có thể

- bài viết

- tiềm năng

- quyền lực

- trước đây

- Vấn đề

- vấn đề

- quá trình

- xử lý

- chương trình

- lập trình

- Lập trình

- hứa hẹn

- cho

- ngẫu nhiên

- phạm vi

- tỉ lệ

- Đọc

- đỏ

- Đã loại bỏ

- Báo cáo

- yêu cầu

- cần phải

- Yêu cầu

- nghiên cứu

- Sức đề kháng

- phản ứng

- Kết quả

- xem xét

- ngay

- Vai trò

- s

- Khoa học

- khoa học

- Phần

- bán dẫn

- Chất bán dẫn

- định

- thiết lập

- Hình dạng

- nên

- thể hiện

- bên

- tín hiệu

- có ý nghĩa

- mô phỏng

- Kích thước máy

- giải pháp

- động SOLVE

- nguồn

- tiêu

- xếp chồng lên nhau

- Tiểu bang

- Bang

- Các bước

- là gắn

- nghiên cứu

- nghiên cứu

- Học tập

- như vậy

- Hỗ trợ

- nhóm

- Công nghệ

- Sự phát triển công nghệ

- hơn

- việc này

- Sản phẩm

- Đồ thị

- Nguồn

- Nhà nước

- cung cấp their dịch

- sau đó

- Đó

- Kia là

- điều này

- Thông qua

- Như vậy

- thời gian

- thời gian

- thời gian

- đến

- hàng đầu

- đối với

- theo truyền thống

- hai

- kiểu

- điển hình

- Dưới

- hiểu

- không may

- đơn vị

- sử dụng

- đã sử dụng

- sử dụng

- Các giá trị

- khác nhau

- Versus

- thẳng đứng

- theo chiều dọc

- Video

- Xem

- ảo

- hình dung

- điện áp

- khối lượng

- vs

- là

- we

- webp

- là

- khi nào

- trong khi

- trắng

- rộng rãi

- sẽ

- với

- làm việc

- đang làm việc

- sẽ

- wu

- năm

- zephyrnet