Một bài báo kỹ thuật có tiêu đề “Song song tập trung vào dữ liệu lớn trong kỷ nguyên Chiplet” đã được các nhà nghiên cứu tại Đại học Princeton xuất bản.

Tóm tắt:

“Theo truyền thống, các ứng dụng song song ồ ạt được thực thi trên các hệ thống phân tán, trong đó các nút tính toán đủ xa để các sơ đồ song song hóa phải giảm thiểu giao tiếp và đồng bộ hóa để đạt được khả năng mở rộng. Việc ánh xạ các khối lượng công việc đòi hỏi nhiều giao tiếp tới các hệ thống phân tán đòi hỏi phải phân vùng vấn đề phức tạp và xử lý trước tập dữ liệu. Với xu hướng dựa trên AI hiện nay là có hàng nghìn bộ xử lý được kết nối với nhau trên mỗi chip, có cơ hội để suy nghĩ lại về khối lượng công việc bị tắc nghẽn truyền thông này. Nút thắt cổ chai này thường phát sinh từ việc truyền tải cấu trúc dữ liệu, gây ra tình trạng truy cập bộ nhớ không đều và vị trí bộ nhớ đệm kém.

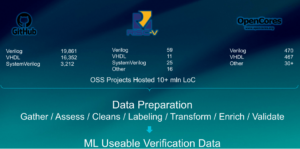

Các công trình gần đây đã giới thiệu các sơ đồ song song hóa dựa trên nhiệm vụ để tăng tốc quá trình truyền tải đồ thị và các khối lượng công việc thưa thớt khác. Việc truyền tải cấu trúc dữ liệu được chia thành các nhiệm vụ và được dẫn truyền qua các đơn vị xử lý (PU). Dalorex đã thể hiện khả năng mở rộng cao nhất (lên tới hàng nghìn PU trên một chip) bằng cách có toàn bộ tập dữ liệu trên chip, rải rác trên các PU và thực thi các tác vụ tại PU nơi dữ liệu cục bộ. Tuy nhiên, nó cũng đặt ra câu hỏi về cách mở rộng quy mô sang các tập dữ liệu lớn hơn khi tất cả bộ nhớ đều nằm trên chip và với chi phí bao nhiêu.

Để giải quyết những thách thức này, chúng tôi đề xuất một kiến trúc có thể mở rộng bao gồm một lưới các chiplet Mảng có thể cấu hình lại tập trung dữ liệu (DCRA). Cấu hình lại theo thời gian đóng gói cho phép tạo ra các sản phẩm chip tối ưu hóa cho các số liệu mục tiêu khác nhau, chẳng hạn như thời gian tạo ra giải pháp, năng lượng hoặc chi phí, trong khi cấu hình lại phần mềm tránh bão hòa mạng khi mở rộng tới hàng triệu PU trên nhiều gói chip. Chúng tôi đánh giá sáu ứng dụng và bốn bộ dữ liệu, với một số cấu hình và công nghệ bộ nhớ, để cung cấp phân tích chi tiết về hiệu suất, công suất và chi phí thực thi dữ liệu cục bộ trên quy mô lớn. Sự song song hóa Tìm kiếm theo chiều rộng đầu tiên của chúng tôi với RMAT-26 trên một triệu PU đạt tới 3323 GTEPS.”

Tìm kỹ thuật giấy ở đây. Xuất bản tháng 2023 năm XNUMX (bản in trước).

Orenes-Vera, Marcelo, Esin Tureci, David Wentzlaf và Margaret Martonosi. “Song song tập trung vào dữ liệu lớn trong kỷ nguyên Chiplet.” arXiv bản in trước arXiv: 2304.09389 (2023).

Sản phẩm liên quan

Mini-Consortia hình thành xung quanh Chiplets

Thị trường chiplet thương mại vẫn còn ở rất xa, nhưng các công ty đang bắt đầu sớm với nhiều mối quan hệ đối tác hạn chế hơn.

Rủi ro bảo mật chiplet bị đánh giá thấp

Mức độ của những thách thức bảo mật đối với các chiplet thương mại là rất khó khăn.

Cuộc đua hướng tới chiplets hỗn hợp

Những thách thức trong việc lắp ráp chiplets từ các xưởng đúc khác nhau mới bắt đầu xuất hiện.

Những cân nhắc về thiết kế và những tiến bộ gần đây trong Chiplets (UC Berkeley/Đại học Bắc Kinh)

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- nguồn: https://semiengineering.com/data-centric-reconfigurable-array-dcra-chiplets-princeton/

- :là

- :Ở đâu

- $ LÊN

- 2023

- a

- đẩy nhanh tiến độ

- Đạt được

- ngang qua

- địa chỉ

- tiến bộ

- Tất cả

- Ngoài ra

- an

- phân tích

- và

- các ứng dụng

- Tháng Tư

- kiến trúc

- LÀ

- xung quanh

- Mảng

- AS

- At

- Bắt đầu

- nhưng

- by

- bộ nhớ cache

- Nguyên nhân

- thách thức

- Chip

- thương gia

- Giao tiếp

- Các công ty

- phức tạp

- sáng tác

- máy tính

- sự cân nhắc

- Phí Tổn

- Tạo

- Current

- dữ liệu

- bộ dữ liệu

- David

- chứng minh

- chi tiết

- khác nhau

- Xa xôi

- phân phối

- hệ thống phân phối

- Đầu

- cho phép

- năng lượng

- đủ

- Toàn bộ

- Kỷ nguyên

- đánh giá

- thi hành

- thực hiện

- Trong

- 4

- từ

- nhận được

- đồ thị

- lưới

- Có

- có

- cao nhất

- chân trời

- Độ đáng tin của

- Hướng dẫn

- Tuy nhiên

- HTTPS

- in

- kết nối với nhau

- trong

- giới thiệu

- IT

- chỉ

- lớn hơn

- Hạn chế

- địa phương

- nhiều

- lập bản đồ

- chợ

- ồ ạt

- Bộ nhớ

- Metrics

- triệu

- hàng triệu

- chi tiết

- mạng

- các nút

- of

- on

- Cơ hội

- Tối ưu hóa

- or

- Nền tảng khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- gói

- Giấy

- Song song

- quan hệ đối tác

- Bắc Kinh

- hiệu suất

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- người nghèo

- quyền lực

- princeton

- Vấn đề

- xử lý

- bộ vi xử lý

- Sản phẩm

- đề xuất

- cho

- công bố

- Câu hỏi

- Cuộc đua

- nâng lên

- Đạt

- gần đây

- đòi hỏi

- nhà nghiên cứu

- rủi ro

- khả năng mở rộng

- khả năng mở rộng

- Quy mô

- mở rộng quy mô

- rải rác

- đề án

- an ninh

- Rủi ro bảo mật

- một số

- duy nhất

- Six

- Phần mềm

- chia

- Bắt đầu

- Vẫn còn

- cấu trúc

- như vậy

- đồng bộ hóa

- hệ thống

- Mục tiêu

- nhiệm vụ

- Kỹ thuật

- Công nghệ

- việc này

- Sản phẩm

- Đó

- Kia là

- điều này

- hàng ngàn

- có tiêu đề

- đến

- đối với

- khuynh hướng

- các đơn vị

- trường đại học

- là

- we

- Điều gì

- cái nào

- trong khi

- với

- công trinh

- zephyrnet