Chiplets đang bắt đầu tác động đến thiết kế chip, mặc dù chúng chưa phổ biến và chưa có thị trường thương mại nào tồn tại cho loại IP cứng này.

Hiện đang có các cuộc thảo luận về quản lý vòng đời silicon, cách tốt nhất để mô tả đặc tính và kết nối các thiết bị này cũng như cách giải quyết các vấn đề như lão hóa không đồng đều và không khớp nhiệt. Ngoài ra, một nỗ lực lớn đang được tiến hành để cải thiện khả năng quan sát của bánh bao theo thời gian, điều này đặc biệt quan trọng vì những thiết bị này được sử dụng trong các ứng dụng quan trọng về an toàn và sứ mệnh.

Tất cả những vấn đề này cần phải được giải quyết để có thể áp dụng rộng rãi và ngành công nghiệp chip đã nhận ra rằng sự chậm lại của Định luật Moore kết hợp với kích thước kẻ ô cố định sẽ đòi hỏi những thay đổi trong cách thiết kế, sản xuất và đóng gói chip. Về mặt vật lý, không thể đưa tất cả các chức năng cần thiết cho nhiều ứng dụng vào một SoC duy nhất và mục tiêu hiện nay là tạo ra một cách tiếp cận có trật tự, có thể dự đoán và lặp lại để phân chia nhiều thành phần này. Về lý thuyết, điều này sẽ cho phép các thiết bị được tùy chỉnh dễ dàng hơn, rút ngắn thời gian đưa ra thị trường và tránh việc mở rộng quy mô đắt tiền của các thành phần không yêu cầu, chẳng hạn như các chức năng tương tự.

Tuy nhiên, để đạt được mục tiêu đó sẽ đòi hỏi phải giải quyết một số vấn đề phức tạp và gai góc. Thứ nhất, nó sẽ đòi hỏi khả năng quan sát, giám sát và phân tích tốt hơn nhiều về những gì được đưa vào một gói. Trong khi khái niệm đưa nhiều chip vào một gói đã có từ những năm 1990 với mô-đun đa chip, với chiplets, khuôn thường nhỏ hơn và mỏng hơn, đồng thời động lực về cách mô tả đặc tính, kiểm tra và quan sát chúng đã thay đổi đáng kể.

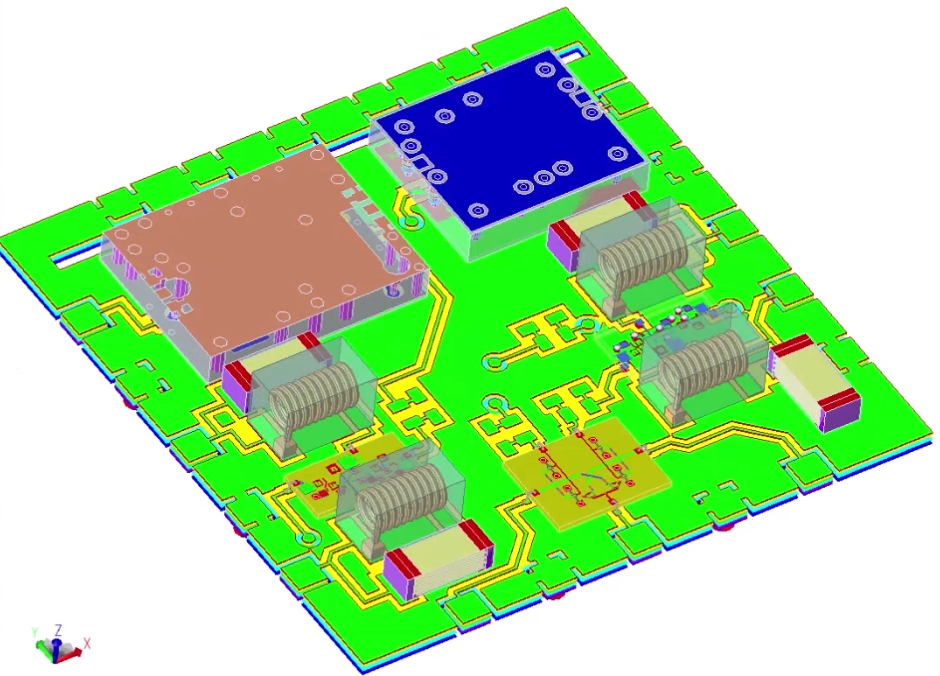

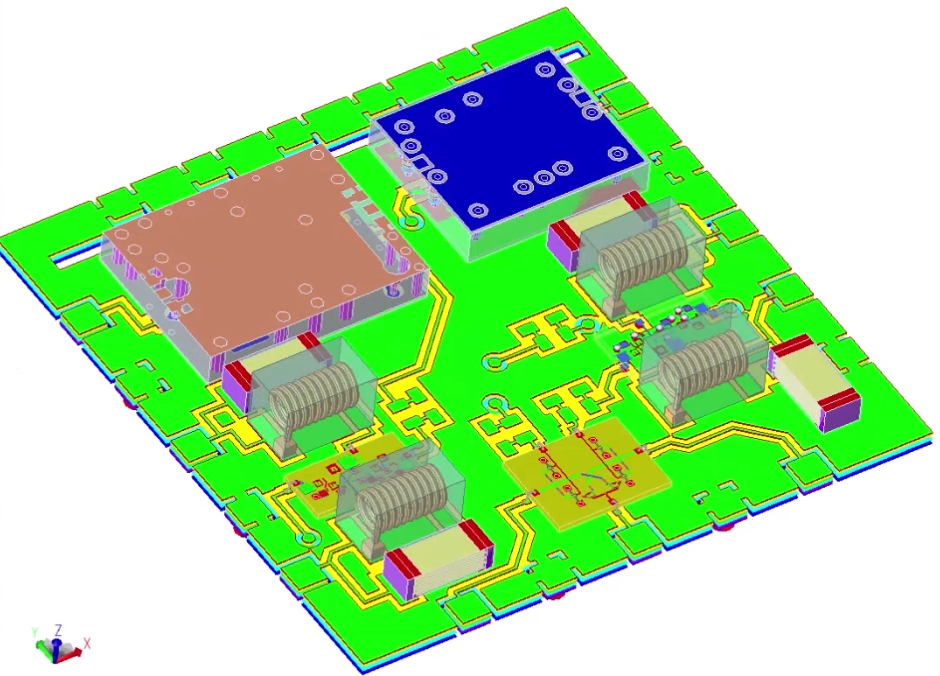

Nilesh Kamdar, người đứng đầu danh mục RF/vi sóng tại Chìa khóa. “Bạn cầm bất kỳ chiếc điện thoại thông minh nào lên và phần không dây của điện thoại thông minh là một mô-đun ngoại vi gồm 20 đến 30 con chip được ép lại với nhau trên một không gian nhỏ hơn móng tay. Điều đó đã xảy ra trong ngành ít nhất một thập kỷ, nếu không muốn nói là lâu hơn. Ngoài ra, một số vấn đề về hàng không vũ trụ và tần số cao khác cũng yêu cầu loại tích hợp này, vì vậy chúng tôi đã thực hiện việc này trước đây.”

Hình 1. Bố cục mô-đun RF đa chip được hiển thị trong PathWave ADS của Keysight. Nguồn: Keysight

Sự thay đổi lớn hiện đang diễn ra liên quan đến ứng dụng rộng hơn nhiều cho phương pháp này, cũng như những cải tiến trong thiết kế chiplet và các cách tiêu chuẩn để kết nối, kiểm tra và đo lường những gì đang xảy ra bên trong các chiplet cũng như gói nâng cao bao quanh chúng.

Kamdar nói: “Ô tô là một ví dụ tuyệt vời về những gì đang thay đổi. “Tại một hội nghị gần đây, phó chủ tịch của một OEM lớn đã nói về việc không thể đặt một trung tâm dữ liệu vào ghế sau của một chiếc ô tô, bởi vì đó là những gì cần có để có một chiếc xe tự hành ngày nay. Nếu bạn tích hợp nhiều hơn - và nếu bằng cách nào đó bạn làm cho tấm ván biến mất và mọi thứ bị ép lại với nhau - có thể theo chiều dọc, chúng ta có thể ép nó vào ghế sau của một chiếc ô tô. Có nhiều trường hợp sử dụng tương tự. Nhu cầu năng lượng cho chiplet có thể thấp hơn nếu bạn xem xét các trung tâm dữ liệu vật lý. Có rất nhiều lợi ích và đó chính là điều đang thúc đẩy các con chiplet ngày nay.”

Tuy nhiên, những thay đổi này có vẻ phức tạp và ngành công nghiệp có thể cần phải xem xét lại vấn đề này. Ông nói: “Xây dựng chiplets trên quy mô lớn là một mô hình khác biệt đến mức tất cả chúng ta cần phải đánh giá lại kỹ năng của mình. “Chúng ta cần đánh giá lại cách các tổ chức được thành lập và kiến trúc diễn ra như thế nào. Chúng ta cần đánh giá lại vai trò của người thiết kế hệ thống. Họ có thể đã nhìn mọi thứ theo một cách khác và họ có thể đã nói, 'Tôi là nhà thiết kế hệ thống. Tôi thiết kế thông số kỹ thuật cho hệ thống. Tôi chia nó thành các thành phần cấp độ nhỏ hơn, các IC riêng lẻ và phân phối các thông số kỹ thuật. Tôi bỏ đi và quay lại sáu tháng sau và xem mọi người đã làm như thế nào.' Có lẽ điều đó thậm chí là không thể. Có thể có nhiều nhà thiết kế hệ thống cần tồn tại trong chuỗi. Đó là những cuộc trò chuyện cần phải diễn ra. Với những người chơi lớn nhất trong ngành, những cuộc trò chuyện đó đã diễn ra nhưng không phải ở khắp mọi nơi.”

Số lượng tương tác tiềm năng trong bối cảnh thiết kế nhiều chiplet là đáng kể và trong nhiều trường hợp là dành riêng cho thiết kế. Shekhar Kapoor, giám đốc cấp cao về quản lý dòng sản phẩm của công ty cho biết: “Nếu bạn tin vào multi-die, nếu bạn tin vào chiplet, bạn phải tin rằng nó sẽ chỉ làm trầm trọng thêm toàn bộ vấn đề [thiết kế và tích hợp]”. Tóm tắt nội dung Nhóm EDA. “Chiplets sẽ đến từ nhiều nơi, nhiều nguồn. Sẽ có rất nhiều sự lựa chọn, rất nhiều lựa chọn cho tất cả mọi người. Vấn đề lớn nhất là cách sử dụng hiện tại xung quanh tất cả điều này. Các công ty lớn đang thực hiện việc này theo cách riêng và tùy chỉnh. Nhưng nếu bạn đi theo hướng tiêu chuẩn hóa rộng rãi, làm sao bạn biết chiplet sắp ra mắt sẽ phù hợp với môi trường, trong sản phẩm mà bạn đang cố gắng xây dựng?”

Mặc dù tập trung vào các tiêu chuẩn như UCIe và Bunch of Wires, vẫn có những sắc thái khác nhau về cách đặc trưng của các chiplet riêng lẻ trong bối cảnh của một hệ thống. “Làm thế nào bạn thực sự biết được hồ sơ của nó? Đó là lúc mà nhiều hoạt động giám sát hơn sẽ xuất hiện, gần giống như một chữ ký,” Kapoor nói. “Bạn có thể đọc nó và biết liệu nó có lý tưởng cho môi trường của bạn hay không. Do ngành đang hướng tới việc hỗ trợ nhiều chiplet hơn nên đây sẽ là vấn đề cốt lõi cần cân nhắc. Nhiều yêu cầu hơn sẽ xuất hiện, nhiều tiêu chuẩn hơn sẽ xuất hiện, vì vậy bạn có thể xem liệu thứ gì đó có phù hợp hay không.”

Ngoài ra còn có những thách thức khác cần phải vượt qua.

Sue Hung Fung, giám đốc tiếp thị dòng sản phẩm của UCIe tại cho biết: “Với chiplets, tất cả các tín hiệu tốc độ cao đều nằm trong gói, do đó khả năng quan sát khó khăn hơn nhiều”. Nhịp. “Điều này có thể được thực hiện thông qua kiểm tra lỗi liên kết, quét mắt, BiST, v.v., để có được một con súc sắc đã biết (KGD). Tất cả các phương pháp thử nghiệm đều được xây dựng xung quanh vấn đề này. Ngoài ra, việc có những công cụ giám sát tốt về tình trạng của liên kết sẽ rất có giá trị và sẽ có những đề xuất mới và khác biệt từ các nhà cung cấp khác nhau.”

Điều quan trọng là giám sát chất lượng tín hiệu trong bối cảnh các thành phần còn lại trong gói, điều này trở nên khó khăn hơn khi có nhiều chức năng được phân tách thành các chiplet.

“Chúng ta có thể theo dõi tín hiệu và chất lượng của những tín hiệu này trong quá trình truyền dữ liệu không? Các kỹ thuật đào tạo được thực hiện trước chế độ nhiệm vụ để cải thiện khả năng truyền dữ liệu mạnh mẽ”, Hung Fung lưu ý. “Việc đào tạo lại là không mong muốn vì nó có thể gây gián đoạn dữ liệu. Chúng tôi cần có khả năng giám sát và báo cáo liên tục từng làn đường cũng như phát hiện bất kỳ sự kiện nào có thể gây ra lỗi trước khi lỗi xảy ra. Việc ngăn ngừa lỗi hệ thống và sửa chữa những lỗi đó bao gồm việc lập bản đồ lại làn đường dự phòng hoặc các phương pháp sửa chữa khác để phát hiện các làn đường bị lỗi nhẹ. Việc đào tạo và giám sát liên tục các tín hiệu chiplet nội bộ này là những thách thức để phân tích hành vi liên kết.”

Các nhóm làm việc của UCIe đang tìm cách chuẩn hóa một số khả năng quan sát này để có một hệ sinh thái liên kết mở. Tuy nhiên, việc bổ sung khả năng quan sát và giám sát cũng có thể khác nhau rất nhiều tùy theo phân khúc dọc.

Randy Fish, giám đốc quản lý dòng sản phẩm của Synopsys EDA Group, giải thích rằng do không có cách tiếp cận tiêu chuẩn và có ít nhà cung cấp thương mại cho các giải pháp có thể quan sát nên hầu hết các giải pháp đều được đặt riêng. Anh ấy nói: “Nếu bạn tham gia bất kỳ trận bán kết chính nào, họ sẽ làm điều gì đó. “Câu hỏi đặt ra là liệu có các chức năng xung quanh khuôn đa năng sẽ buộc chúng tôi phải tiêu chuẩn hóa để có cơ sở hạ tầng gắn kết hoặc mạch lạc để giám sát và gỡ lỗi — về cơ bản là để xem điều gì đang diễn ra, đặc biệt nếu bạn nhận được nhiều khuôn từ nhiều nhà cung cấp. Một số giải pháp khuôn đa năng đang được ứng dụng vào ô tô và ở đó họ quan tâm đến những thứ như lão hóa và điều gì đang xảy ra với những khuôn này. Và như chúng ta biết, đó là các nút nâng cao. Không phải là bạn có 6 cái chết vì công nghệ 10 tuổi đã trưởng thành. Đây là những nút nâng cao không có lịch sử lâu dài. Vì lý do đó, có một số yếu tố buộc điều này phải xảy ra.”

Chiplets cũng đưa ra một số sự tương phản thú vị. Kamdar của Keysight lưu ý rằng trong một cuộc họp CEO gần đây, một trong những thành viên tham gia hội thảo đã nói rằng các chiplet có sự phân đôi độc đáo. “Một mặt, mỗi chiplet có thể là một IP độc lập mà bạn có thể mua từ nhà cung cấp IP và tích hợp nó vào hệ thống của mình với chi phí tương đối thấp, tương đối dễ dàng. Tuy nhiên, toàn bộ khối tài sản mà bạn đang cố gắng xây dựng đột nhiên buộc bạn phải biết mọi thứ. Trước đây, bạn có thể chỉ nói: 'Tôi cần sáu thứ. Tôi sẽ mua 5 chiếc từ một nhà cung cấp IP và họ sẽ tìm ra thứ nó cần. Tôi sẽ tập trung vào một cái.” Nhưng bây giờ bạn có thể không thành công khi làm điều đó. Bạn thực sự có thể cần biết cách thực hiện cả sáu điều đó và tìm ra cách tất cả những điều đó xảy ra vì độ phức tạp của vấn đề ngày càng tăng lên. Điều này có thể buộc ngành ban đầu chỉ cho phép những công ty lớn tìm ra điều này. Có thể phải mất nhiều thời gian hơn nữa để các nhà cung cấp nhỏ hơn có thể thành công trong môi trường này.”

Tuy nhiên, sẽ cần nhiều hơn một công ty để tăng tốc việc tích hợp và áp dụng chiplet.

“Keysight đã tham dự Hội nghị chuyên đề TSMC, một sự kiện công khai hơn và sau đó là một hội thảo chỉ có các đối tác là thành viên của Liên minh Vải 3D,” Kamdar cho biết. “TSMC bắt đầu và kết thúc cả ngày bằng cách nói về cách tất cả chúng ta cần phải cùng nhau giải quyết vấn đề này, điều này cũng được những người tham gia khác, bao gồm cả AMD và Qualcomm, đồng tình. Diễn giả của cả hai công ty cho biết không một công ty EDA nào biết cách tự mình giải quyết vấn đề chiplet. Toàn bộ ngành phải làm việc cùng nhau.”

Những thách thức kỹ thuật

Một mối quan tâm quan trọng khác với chiplets là khả năng tản nhiệt. Đây là một phần của đặc tính, nhưng nó cũng phụ thuộc nhiều vào các trường hợp sử dụng, lựa chọn đóng gói và kiến trúc tổng thể của hệ thống trong gói.

Rishi Chugh, phó chủ tịch tiếp thị sản phẩm, IP Group tại Cadence cho biết: “Đối với các chiplet, biên độ biên trong thiết kế rất mỏng nhờ PPA tối ưu (nhắm mục tiêu pj/bit mạnh mẽ và mật độ bên bờ biển), điều này rất quan trọng khi thiết kế PHY chiplet”. “Độ tin cậy là yếu tố then chốt và khả năng quan sát để sàng lọc KGD cũng như đưa KGD đạt được thành công trong hoạt động thương mại cũng vậy. Các sơ đồ toàn vẹn dữ liệu như CRC (kiểm tra dự phòng theo chu kỳ), quét mắt, BiST và các mạch giám sát được triển khai trong thiết kế để đảm bảo độ bền và thiết kế phải được cung cấp quá mức các cơ chế lỗi để đảm bảo đường dữ liệu có khả năng phục hồi.”

Chugh cho biết thêm, toàn bộ chương trong giao thức UCIe được dành riêng cho việc khởi tạo và đào tạo liên quan đến giao thức UCIe, bao gồm khía cạnh khả năng quan sát của giao thức.

Ngoài ra, còn có tranh luận về việc liệu các nguyên tắc cơ bản thực tế của việc thêm khả năng quan sát vào hệ thống có phải là phần khó nhất hay không, hay liệu sự thay đổi trong suy nghĩ xung quanh các khái niệm này có khó khăn hơn hay không.

“Nó thực sự không quá phức tạp so với những thứ khác vì nó 'chỉ' là một khối khác được kết nối. Có sự quan sát và chúng tôi có khả năng theo dõi mọi thứ,” Frank Schirrmeister, phó chủ tịch giải pháp và phát triển kinh doanh tại động mạch IP. “Người dùng đã yêu cầu những thứ như xem sổ đăng ký từ góc độ phần mềm. Vì vậy, thách thức bây giờ là làm cho các sổ đăng ký đó có sẵn trong NoC. Từ góc độ NoC, bản thân có các giao thức như CHI, ACE, AMBA, OCP hoặc các giao thức khác và đó là cơ chế của ngôn ngữ - cách chúng nói chuyện và cách chúng tương tác. Trong NoC, với các giao thức phức tạp hơn, có những điều xảy ra qua nhiều chu kỳ, vì vậy bạn cần chờ phản hồi, bạn sẽ đưa mọi thứ vào quy trình.”

Điều này tương tự như việc thực thi suy đoán trong bộ xử lý. Schirrmeister giải thích: “Chúng tôi nói về những khoản tín dụng này, chẳng hạn như tôi phải đợi phản hồi trong bao lâu, v.v. “Đó là tất cả các phần của giao thức. Trong NoC, bạn cần hiểu các vấn đề như bộ đệm sâu đến mức nào? Khi nào tôi thực sự đang chờ dữ liệu? Đó là một phần hiệu suất. Sau đó, để có khả năng quan sát, bạn có thể kết nối với dữ liệu và các cảm biến có thể sử dụng mạng riêng tùy thuộc vào cách bạn muốn định cấu hình nó. Ví dụ: trong trường hợp màn hình trên chip, bạn cần quyết định xem có nên đặt thiết bị này trên một bus có khả năng quan sát đặc biệt hay không. Luôn có một cuộc thảo luận về việc tôi thực sự có bao nhiêu lần gỡ lỗi? Vào cuối ngày, nó 'chỉ' là một kết nối khác của các thành phần đó và bạn cần quyết định cách xuất nó ra khỏi chip, v.v. Bạn lưu trữ bao nhiêu trên chip chỉ là vấn đề tôi sẵn sàng chi bao nhiêu cho việc đó?”

Điều đó trở nên đặc biệt quan trọng khi ghép các chiplets lại với nhau. “Làm cách nào để đảm bảo tôi có đủ không gian cho thực thể tính toán trông giống như dữ liệu này, thực thể này không thực sự thêm bất kỳ giá trị nào vào hàm ngay lập tức?” Gajinder Panesar, kiến trúc sư trưởng tại Picocom hỏi. “Ngoài ra, tôi có thể không phải là chuyên gia giám sát, nhưng tôi biết mình cần nó. Vì vậy tôi cần điều gì đó có nội dung: 'Chỉ cần nhấn nút đó.' Bạn có một môi trường, chúng tôi đang thiết kế và 'điều này' xảy ra. Lý tưởng nhất là chúng ta nên quan sát hành vi của hiệu suất CPU và sau đó điều chỉnh linh hoạt các khía cạnh nhất định của lõi để có được hiệu suất tốt hơn.”

Một trong những phần vẫn chưa được phát triển là khả năng điều khiển động của thiết bị và những điều chỉnh có thể được thực hiện trong suốt vòng đời của thiết bị.

Lee Harrison, giám đốc tiếp thị sản phẩm của nhóm Tessent tại Phần mềm Công nghiệp Kỹ thuật số Siemens. “Chúng tôi đã tích hợp tất cả các màn hình để thực hiện các công việc trong hệ thống, nhưng nó đang đóng vòng lặp đó. Đối với các dạng hình học mới hơn, vẫn còn phải học hỏi nhiều để thực sự tối ưu hóa cách chúng ta có thể điều chỉnh các thông số khác nhau của thiết bị nhằm nâng cao độ tin cậy đó. Phần kết thúc vòng lặp đó với hệ thống trong cuộc sống là nơi chứa đựng một lượng giá trị khổng lồ. Tuy nhiên, vẫn còn nhiều việc phải làm.

Thay đổi vai trò trách nhiệm

Chiplet thương mại còn bổ sung thêm một vấn đề hóc búa khác, đó là ai chịu trách nhiệm khi quan sát thấy có điều gì đó không mong muốn hoặc xảy ra sự cố.

“Nếu tôi là một nhà sản xuất chip, tôi tạo ra con chip và tôi có thể trải qua một OSAT để thử nghiệm,” Paul Karazuba, phó chủ tịch tiếp thị tại nhà thám hiểm. “Tôi có thể sử dụng ASE làm nhà đóng gói nhưng tôi bán nó với tên và giấy bảo hành của mình. Sẽ thú vị hơn khi chúng ta có con nhỏ. Trong tất cả các cuộc họp của chúng tôi liên quan đến chiplets, câu hỏi luôn được đặt ra là ai sẽ chịu trách nhiệm về việc gì. Giả sử tôi tạo ra một chiplet AI và tôi bán vào một hệ thống và đóng gói cùng với các chiplet của sáu công ty khác. Công ty nào sẽ bảo hành? Công ty nào sẽ thực hiện dịch vụ trên đó? Hiện tại không có sự đồng thuận thực sự.”

Karazuba cho biết ý tưởng thực hiện là công ty có tên bên ngoài gói hàng sẽ chịu trách nhiệm. “Công ty đó có thể sẽ là công ty chịu trách nhiệm cuối cùng về dịch vụ dành cho khách hàng của mình, nhưng nó mang đến một lớp dịch vụ khác mà các nhà sản xuất chiplet cần cung cấp, và điều đó sẽ rất thú vị. Điều đáng sợ là vào khoảng năm 2000, tam giác Intel-Microsoft-Dell mọi người chỉ tay vào nhau. Đó là nỗi sợ hãi thầm lặng trong ngành hiện nay.”

Và có lẽ nó không phải là một trong những đứa con nhỏ. Điều gì xảy ra nếu chất nền hoặc kết nối vật lý bị lỗi?

Karazuba nói: “Từ quan điểm thử nghiệm, một chiplet có thể thử nghiệm hoàn toàn tốt”. “Nhưng khi có vấn đề về kết nối vật lý, nhà sản xuất chiplet hiểu điều đó như thế nào so với nhà sản xuất mô-đun đa chip? Nó sẽ rất thú vị. Cách duy nhất để giải quyết những vấn đề này là thử và sai. Với tư cách là nhà sản xuất chất bán dẫn, chúng tôi có thể thiết kế bao nhiêu hợp đồng pháp lý tùy thích, nhưng chúng tôi đang ở trong vùng nước chưa được khám phá ở đây và mọi thứ sẽ phải được điều chỉnh. Các mô hình hỗ trợ sẽ phải được điều chỉnh để phản ánh thực tế mới về việc silicon nguyên khối không phải là phương tiện chính để bán chất bán dẫn.”

Kapoor của Synopsys đã nhìn thấy những phản ánh trong hệ sinh thái. “Luôn luôn có các hệ sinh thái, nhưng hệ sinh thái đang hoạt động của bạn dù bạn ở đâu có thể là vòng tròn tiếp theo xung quanh nó. Nếu bạn đang thiết kế, bạn sẽ chỉ quan tâm đến các quy tắc thiết kế đúc và sổ tay quy tắc thiết kế. Điều đó đang thay đổi khi bạn nói về các chiplets. Ngay cả với thiết kế, giờ đây bạn thậm chí còn nghĩ về việc kiểm tra nhiều hơn trước đây. Bạn đang nói chuyện với Thuận lợi và đất nước. Mặc dù bạn chỉ là một nhà thiết kế, nhưng bạn phải tìm ra những gì bạn cần đưa vào theo quan điểm ATPG và cách nó sẽ được kiểm tra. Quy mô hệ sinh thái liên quan đang tăng lên.”

Tuy nhiên, ngành không có lựa chọn nào khác ngoài việc giải quyết những vấn đề này. “Chúng ta đã nói về thị trường chiplet. Bạn sẽ có thể lấy xúc xắc ra và chuẩn bị sẵn sàng. Chúng ta vẫn còn cách xa mục tiêu đó, nhưng các bước thực hiện đang trở nên rõ ràng hơn về những gì chúng ta cần đạt được. Kết nối là cơ bản. Các tiêu chuẩn UCIe là bắt buộc, cùng với đó là các giao thức và quy tắc theo quan điểm kết nối mà bạn phải thiết lập. Tiếp theo sẽ là những mô hình được xác định rất rõ ràng. Những thách thức mà chúng ta đang nói đến bị ảnh hưởng bởi nhiệt, đặc biệt là và năng lượng. Một số tiêu chuẩn đã tồn tại xung quanh vấn đề đó và chúng tôi sẽ chuyển từ khả năng kết nối sang mô hình đặc trưng để chúng tôi có thể sử dụng tiêu chuẩn đó một cách đáng tin cậy hơn. Sau đó, chúng tôi sẽ cần một số loại chữ ký, đó là nơi chúng tôi có thể nhìn thấy từ quan điểm có thể kiểm tra được tuổi thọ và cách tất cả các người chết sẽ thay đổi khác nhau như thế nào.”

Đầu vào của tất cả những thứ này sẽ đến từ chip và màn hình hệ thống, những thứ này cũng cần phải dựa trên các tiêu chuẩn.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- Mua và bán cổ phần trong các công ty PRE-IPO với PREIPO®. Truy cập Tại đây.

- nguồn: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 1

- 20

- 30

- 3d

- a

- có khả năng

- Có khả năng

- Giới thiệu

- đẩy nhanh tiến độ

- Đạt được

- hoạt động

- thực tế

- thực sự

- thêm vào

- thêm

- thêm

- Ngoài ra

- Điều chỉnh

- điều chỉnh

- Nhận con nuôi

- quảng cáo

- tiên tiến

- Không gian vũ trụ

- tích cực

- Lão hóa

- AI

- Tất cả

- Liên minh

- cho phép

- Đã

- Ngoài ra

- luôn luôn

- am

- AMD

- số lượng

- an

- phân tích

- phân tích

- và

- Một

- bất kì

- Các Ứng Dụng

- các ứng dụng

- phương pháp tiếp cận

- kiến trúc

- LÀ

- xung quanh

- AS

- khía cạnh

- các khía cạnh

- liên kết

- At

- ô tô

- tự trị

- xe tự trị

- có sẵn

- tránh

- xa

- trở lại

- dựa

- Về cơ bản

- BE

- bởi vì

- trở thành

- trở thành

- được

- trước

- Bắt đầu

- được

- Tin

- Lợi ích

- BEST

- Hơn

- lớn

- lớn nhất

- Một chút

- Chặn

- bảng

- cả hai

- Nghỉ giải lao

- Mang lại

- rộng

- rộng hơn

- xây dựng

- xây dựng

- xăn lên

- xe buýt

- kinh doanh

- phát triển kinh doanh

- nhưng

- nút

- mua

- by

- Nhịp

- gọi là

- CAN

- khả năng

- xe hơi

- mà

- trường hợp

- trường hợp

- Nguyên nhân

- Trung tâm

- Trung tâm

- giám đốc điều hành

- nhất định

- chuỗi

- thách thức

- thách thức

- thách thức

- thay đổi

- thay đổi

- Những thay đổi

- thay đổi

- Chương

- đặc trưng

- đặc trưng

- kiểm tra

- Séc

- chánh

- Chip

- Snacks

- sự lựa chọn

- lựa chọn

- Vòng tròn

- rõ ràng hơn

- Rõ ràng

- Đóng

- đóng cửa

- mạch lạc

- kết dính

- kết hợp

- Đến

- đến

- đến

- thương gia

- Các công ty

- công ty

- phức tạp

- phức tạp

- phức tạp

- các thành phần

- khái niệm

- khái niệm

- Liên quan

- quan tâm

- Hội nghị

- Kết nối

- kết nối

- Kết nối

- Sự đồng thuận

- Hãy xem xét

- xem xét

- bối cảnh

- liên tục

- liên tục

- hợp đồng

- Ngược lại

- tương phản

- điều khiển

- cuộc hội thoại

- Trung tâm

- Phí Tổn

- có thể

- bìa

- CPU

- CRC

- tín

- quan trọng

- Current

- khách hàng

- tùy chỉnh

- chu kỳ

- dữ liệu

- Trung tâm dữ liệu

- các trung tâm dữ liệu

- Ngày

- ngày

- nhiều

- tranh luận

- thập kỷ

- quyết định

- dành riêng

- sâu

- xác định

- mật độ

- phụ thuộc

- Tùy

- Thiết kế

- thiết kế

- nhà thiết kế

- thiết kế

- thiết kế

- mong muốn

- phát triển

- Phát triển

- thiết bị

- Thiết bị (Devices)

- ĐÃ LÀM

- Die

- khác nhau

- khó khăn

- kỹ thuật số

- Giám đốc

- biến mất

- thảo luận

- thảo luận

- phân phát

- do

- làm

- làm

- thực hiện

- dont

- xuống

- lái xe

- suốt trong

- năng động

- năng động

- động lực

- mỗi

- dễ dàng

- hệ sinh thái

- Hệ sinh thái

- nỗ lực

- xuất hiện

- cho phép

- kích hoạt

- cuối

- đủ

- đảm bảo

- Toàn bộ

- thực thể

- Môi trường

- lôi

- đặc biệt

- thành lập

- bất động sản

- vv

- Ngay cả

- Sự kiện

- sự kiện

- BAO GIỜ

- mọi người

- tất cả mọi thứ

- ví dụ

- thực hiện

- tồn tại

- tồn tại

- đắt tiền

- chuyên gia

- Giải thích

- xuất khẩu

- thêm

- mắt

- vải

- các yếu tố

- không

- Không

- xa

- Thời trang

- sợ hãi

- vài

- Sung

- Hình

- Cá

- phù hợp với

- cố định

- Tập trung

- Trong

- Buộc

- Lực lượng

- Ra

- Foundry

- từ

- trước mặt

- chức năng

- chức năng

- cơ bản

- Nguyên tắc cơ bản

- hộp số

- được

- nhận được

- được

- Go

- mục tiêu

- Đi

- đi

- tốt

- tuyệt vời

- rất nhiều

- Nhóm

- Các nhóm

- tay

- xảy ra

- Xảy ra

- xảy ra

- Có

- có

- he

- cho sức khoẻ

- tại đây

- Cao

- Tân sô cao

- cao

- lịch sử

- House

- Độ đáng tin của

- Hướng dẫn

- Tuy nhiên

- HTTPS

- lớn

- i

- ICS

- ý tưởng

- lý tưởng

- if

- lập tức

- Va chạm

- tác động

- thực hiện

- quan trọng

- không thể

- nâng cao

- cải tiến

- in

- bao gồm

- Bao gồm

- tăng

- độc lập

- hệ thống riêng biệt,

- các ngành công nghiệp

- ngành công nghiệp

- Cơ sở hạ tầng

- ban đầu

- đầu vào

- tích hợp

- hội nhập

- tính toàn vẹn

- tương tác

- tương tác

- thú vị

- nội bộ

- trong

- giới thiệu

- IP

- vấn đề

- các vấn đề

- IT

- ITS

- chỉ

- Kapoor

- Key

- Kicks

- Loại

- Biết

- nổi tiếng

- Đường nhỏ

- Ngôn ngữ

- lớn

- một lát sau

- Luật

- lớp

- Bố trí

- dẫn

- hàng đầu

- học tập

- ít nhất

- Lee

- Hợp pháp

- Cấp

- vòng đời

- tuổi thọ

- đời

- Lượt thích

- Dòng

- LINK

- dài

- còn

- tìm kiếm

- Rất nhiều

- Thấp

- thực hiện

- Mainstream

- chính

- làm cho

- nhà sản xuất

- Các nhà sản xuất

- Làm

- quản lý

- giám đốc

- nhãn hiệu

- sản xuất

- nhiều

- thị trường

- Marketing

- thị trường

- trưởng thành

- max-width

- Có thể..

- đo

- cơ chế

- các cuộc họp

- phương pháp

- Might

- Sứ mệnh

- Chế độ

- kiểu mẫu

- mô hình

- mô-đun

- Modules

- Màn Hình

- giám sát

- màn hình

- Monolithic

- tháng

- chi tiết

- di chuyển

- nhiều

- nhiều

- phải

- my

- tên

- Cần

- nhu cầu

- mạng

- Mới

- tiếp theo

- Không

- các nút

- lưu ý

- tại

- con số

- tuân theo

- of

- off

- on

- ONE

- đang diễn ra

- có thể

- mở

- hoạt động

- tối ưu

- Tối ưu hóa

- Các lựa chọn

- or

- gọi món

- tổ chức

- Nền tảng khác

- Những người tham gia khác

- Khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- ra

- bên ngoài

- kết thúc

- tổng thể

- Vượt qua

- riêng

- gói

- đóng gói

- bao bì

- bảng điều khiển

- thông số

- một phần

- tham gia

- riêng

- đặc biệt

- Đối tác

- các bộ phận

- qua

- paul

- hiệu suất

- quan điểm

- vật lý

- Thể chất

- chọn

- hình ảnh

- mảnh

- miếng

- đường ống dẫn

- Nơi

- lập kế hoạch

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- người chơi

- Điểm

- Quan điểm

- Phổ biến

- danh mục đầu tư

- có thể

- tiềm năng

- quyền lực

- Dự đoán

- Chủ tịch

- nhấn

- Phòng chống

- trước đây

- chính

- Trước khi

- có lẽ

- Vấn đề

- vấn đề

- bộ vi xử lý

- Sản phẩm

- Hồ sơ

- Đề xuất

- giao thức

- giao thức

- cho

- công khai

- đặt

- Đặt

- qualcomm

- chất lượng

- câu hỏi

- nâng lên

- Đọc

- sẵn sàng

- thực

- bất động sản

- Thực tế

- có thật không

- lý do

- gần đây

- công nhận

- phản ánh

- Những phản ánh

- đăng ký

- tương đối

- có liên quan

- độ tin cậy

- sửa

- có thể lặp lại

- báo cáo

- yêu cầu

- cần phải

- Yêu cầu

- đàn hồi

- phản ứng

- phản ứng

- trách nhiệm

- chịu trách nhiệm

- REST của

- ngay

- sự mạnh mẽ

- Vai trò

- Quy tắc

- quy tắc

- Nói

- bán

- nói

- nói

- nói

- Quy mô

- mở rộng quy mô

- quét

- đề án

- Trường học

- Màn

- xem

- đã xem

- phân khúc

- bán

- Bán

- bán dẫn

- cao cấp

- cảm biến

- dịch vụ

- định

- một số

- kệ

- thay đổi

- nên

- thể hiện

- bên

- Tín hiệu

- tín hiệu

- có ý nghĩa

- đáng kể

- Silicon

- tương tự

- duy nhất

- Six

- Sáu tháng

- Kích thước máy

- kích thước

- kỹ năng

- Chậm

- nhỏ

- nhỏ hơn

- điện thoại thông minh

- So

- Phần mềm

- Giải pháp

- động SOLVE

- Giải quyết

- một số

- một cái gì đó

- nguồn

- nguồn

- Không gian

- diễn giả

- đặc biệt

- thông số kỹ thuật

- đầu cơ

- tốc độ

- tiêu

- Bóp

- ngăn xếp

- Tiêu chuẩn

- tiêu chuẩn

- bắt đầu

- Các bước

- Vẫn còn

- hàng

- thành công

- thành công

- như vậy

- kiện

- nhà cung cấp

- hỗ trợ

- Hội nghị chuyên đề

- hệ thống

- hệ thống

- Hãy

- mất

- Thảo luận

- nói

- nhắm mục tiêu

- kỹ thuật

- Công nghệ

- về

- thử nghiệm

- Kiểm tra

- hơn

- việc này

- Sản phẩm

- cung cấp their dịch

- Them

- tự

- sau đó

- lý thuyết

- Đó

- nhiệt

- Kia là

- họ

- điều

- điều

- Suy nghĩ

- điều này

- những

- Tuy nhiên?

- Thông qua

- thời gian

- đến

- bây giờ

- bên nhau

- đối với

- theo dõi

- Hội thảo

- chuyển

- thử nghiệm

- phep thử va lôi sai

- tsmc

- thường

- hiểu

- Đường dưới

- Bất ngờ

- độc đáo

- us

- sử dụng

- đã sử dụng

- Quý báu

- giá trị

- khác nhau

- xe

- nhà cung cấp

- nhà cung cấp

- Versus

- thẳng đứng

- theo chiều dọc

- rất

- Phó Chủ Tịch

- Xem

- chờ đợi

- Đợi

- muốn

- là

- Waters

- Đường..

- cách

- we

- TỐT

- đi

- Điều gì

- Là gì

- khi nào

- liệu

- cái nào

- trong khi

- CHÚNG TÔI LÀ

- toàn bộ

- có

- phổ biến rộng rãi

- sẽ

- sẵn sàng

- không dây

- với

- ở trong

- Công việc

- làm việc cùng nhau

- đang làm việc

- hội thảo

- thế giới

- sẽ

- Sai

- nhưng

- bạn

- trên màn hình

- zephyrnet