Các cấu trúc lồi mới đang được phát triển để cho phép mật độ kết nối cao hơn trong bao bì chip lật, nhưng chúng phức tạp, đắt tiền và ngày càng khó sản xuất.

Đối với những sản phẩm có số lượng pin cao, con chip lật [1] gói từ lâu đã là một lựa chọn phổ biến vì chúng tận dụng toàn bộ khu vực khuôn để kết nối. Công nghệ này đã được sử dụng từ những năm 1970, bắt đầu với C4 của IBM (kết nối chip thu gọn có điều khiển), nhưng nó thực sự được sử dụng rộng rãi vào những năm 1990.

Kể từ đó, công nghệ Bump đã phát triển để xử lý mật độ kết nối tín hiệu và công suất ngày càng tăng theo yêu cầu của bộ nhớ, điện toán hiệu năng cao và các thiết bị điện toán di động. Để đáp ứng nhu cầu đó đòi hỏi công nghệ kết nối mới cho phép các bước nhảy nhỏ hơn, hiện đang được sản xuất.

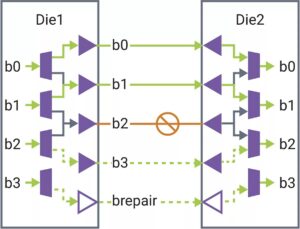

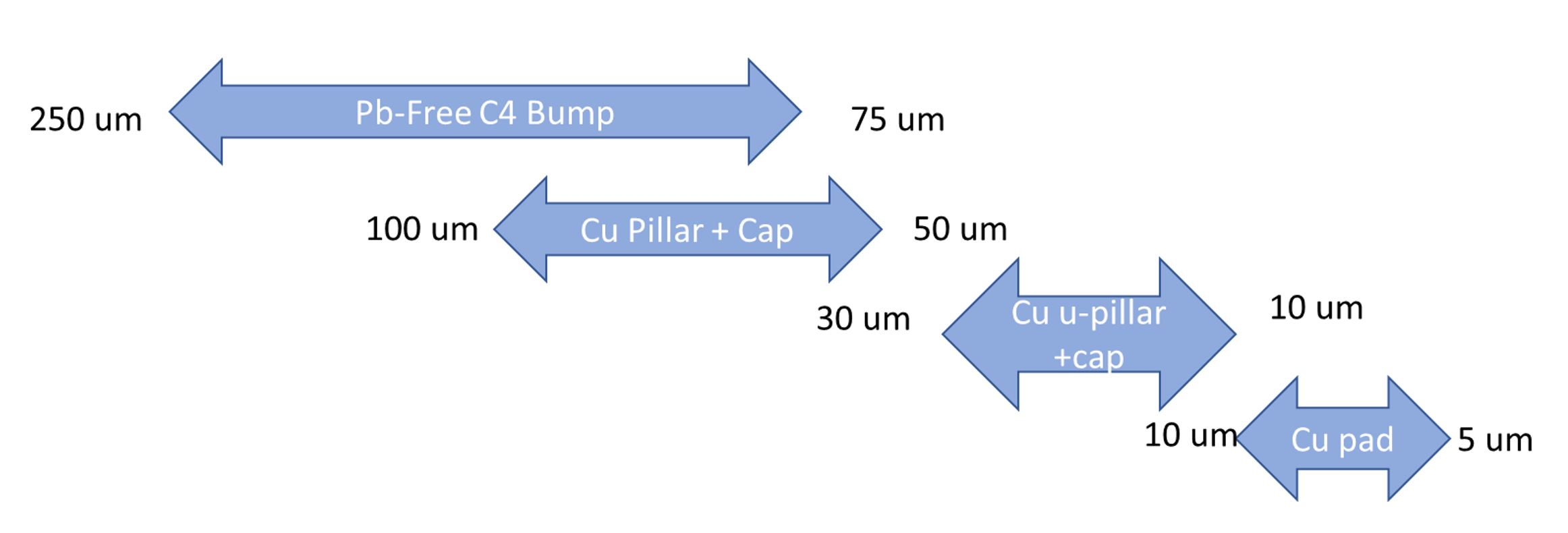

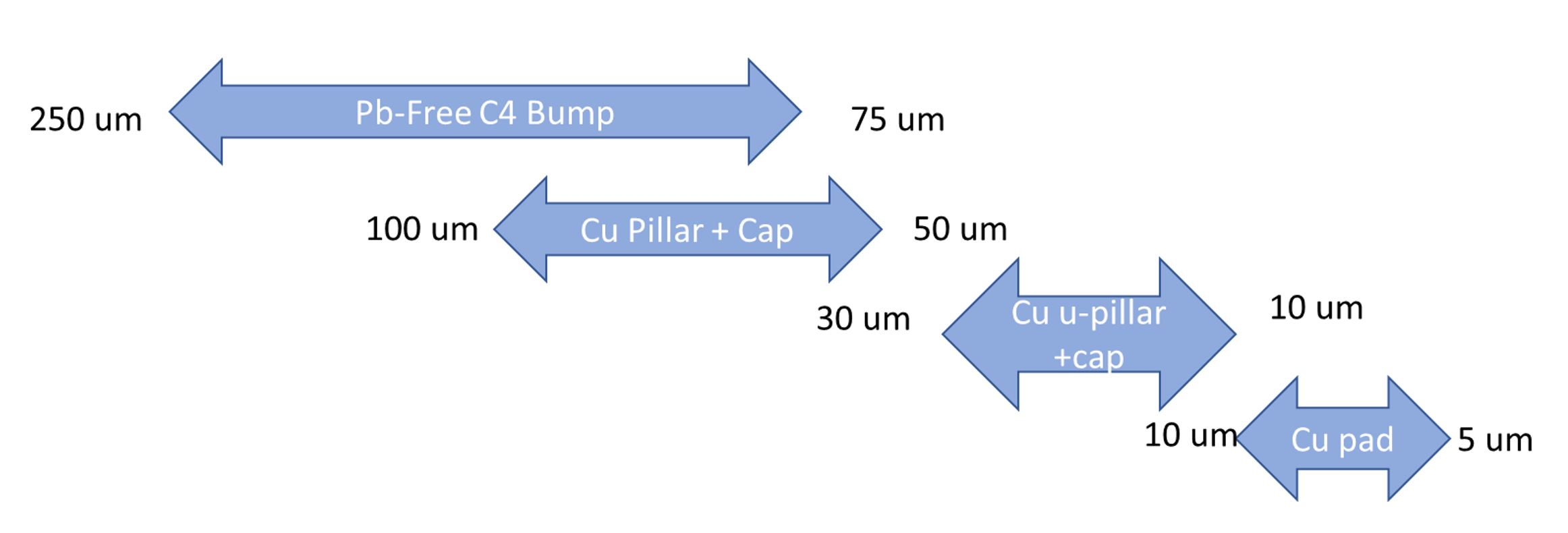

Nhìn theo thời gian, lộ trình kết nối chip lật tiến triển từ các va chạm không chì đến các cột đồng và sau đó đến các vi mạch đồng. Kích thước bước tiếp tục giảm, do đó đã tạo ra những thách thức trong sản xuất về va đập và liên kết.

Hình 1: Phạm vi quảng cáo của công nghệ chip lật. Nguồn: A. Meixner/Kỹ thuật bán dẫn

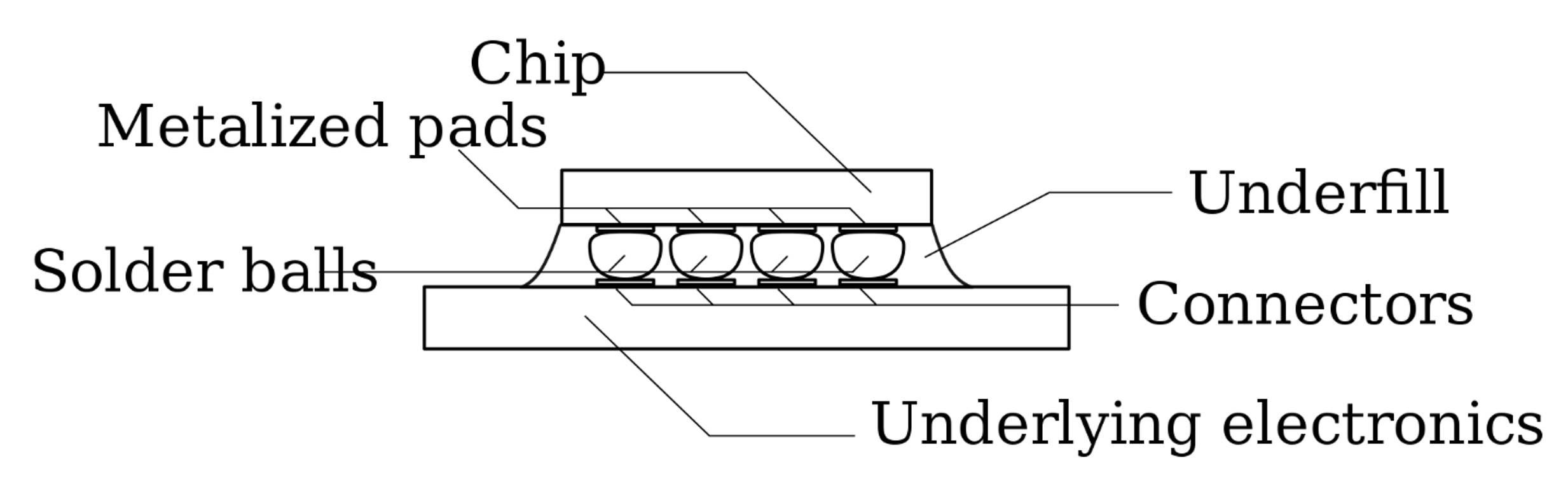

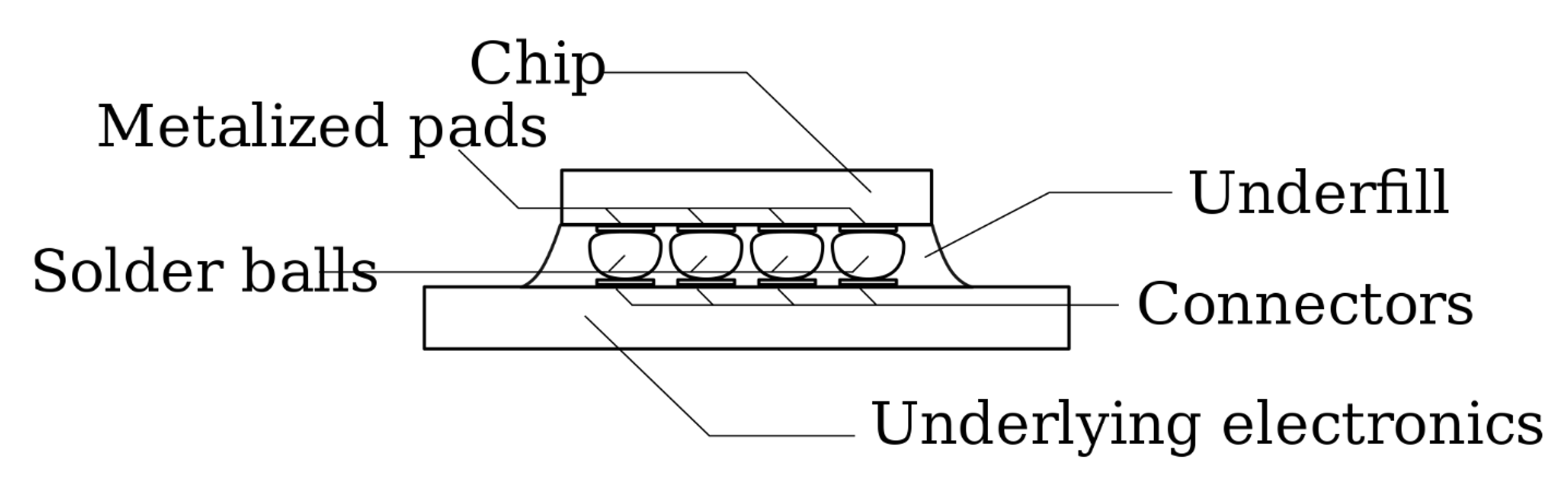

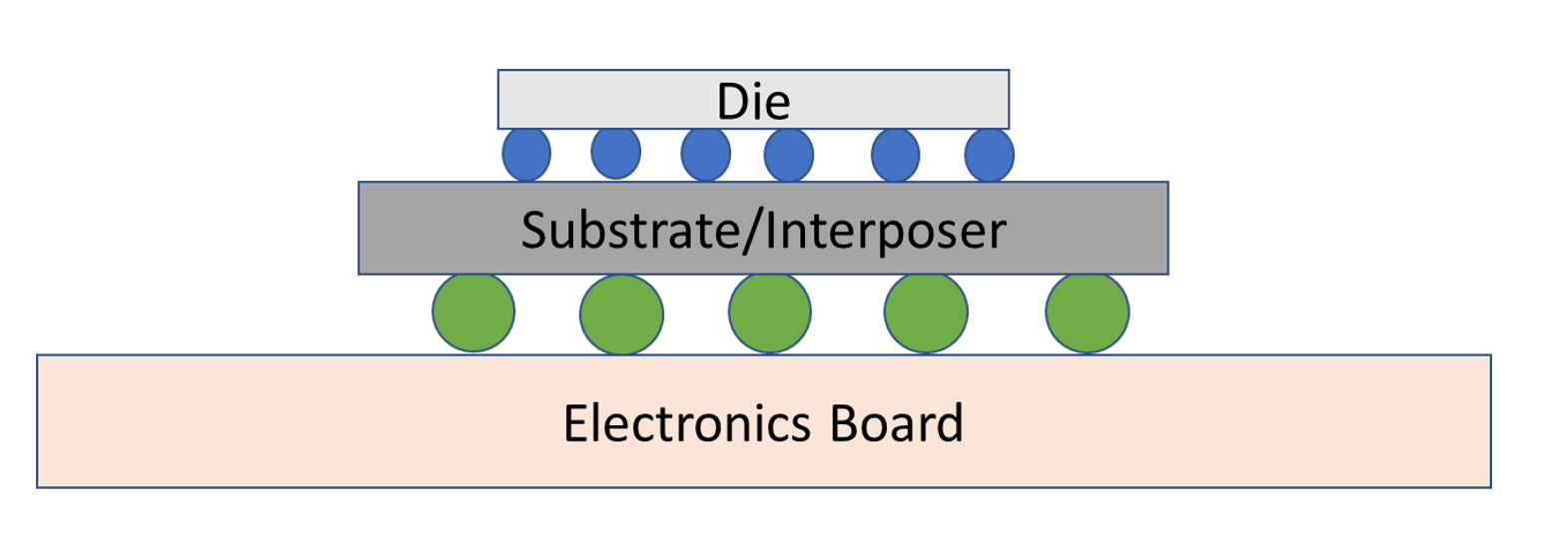

Hình 2: Các thành phần của chip lật. Nguồn: Wikipedia

“Trong lĩnh vực chip lật - có bước sóng từ 250 micron trở xuống - ban đầu nó là những va chạm bằng thiếc và một trong những bước chuyển lớn là không có chì. Nhưng khi bạn bắt đầu đạt tới 100 micron hoặc thấp hơn, bạn bắt đầu nhìn thấy nhiều cột đồng hơn, mặc dù có sự chồng chéo khi chúng tôi thấy các cột đồng lên tới 250 micron,” Jeff Schaefer, kỹ sư quy trình cấp cao tại Công nghiệp Promex. “Với khoảng cách 250 micron, chúng tôi thấy kích thước vết lồi 130 micron hoặc đường kính trụ đồng. Khi chúng tôi đạt được khoảng cách 100 micron, nó sẽ có đường kính 80 micron. Nhỏ nhất mà tôi từng thấy là khoảng cách 62.5 micron với cột 40 micron. Tôi hy vọng sẽ sớm bắt đầu nhìn thấy kích thước 50 micron.”

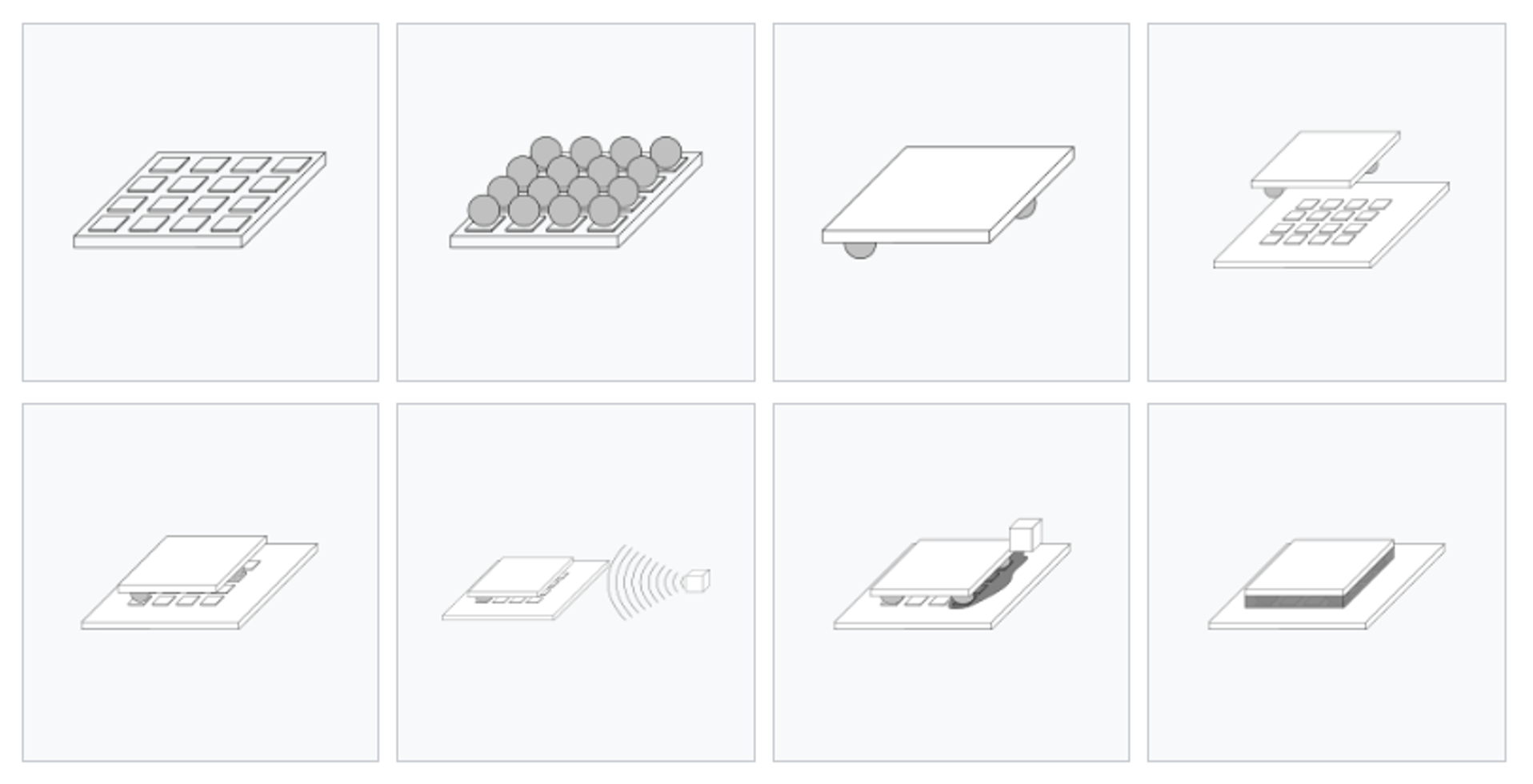

Quá trình flip-chip cơ bản bắt đầu sau khi chế tạo mạch, khi các miếng kim loại được tạo ra trên bề mặt khuôn để kết nối với I/O. Tiếp theo là va chạm wafer, trong đó một quả bóng hàn được đặt trên mỗi miếng đệm. Sau đó, tấm wafer được cắt hạt lựu và những khuôn đó được lật và định vị sao cho các viên hàn thẳng hàng với các miếng đệm nền. Các quả bóng hàn sau đó được nấu chảy/nấu chảy lại, thường sử dụng không khí nóng và khuôn gắn được đổ đầy chất kết dính cách điện, thường sử dụng tác động mao dẫn. [1]

Hình 3: Quy trình sản xuất Flip-chip. Nguồn: Wikipedia

Việc di chuyển đến một cột đồng hoặc một khối vi mô đòi hỏi kỹ thuật in thạch bản để tạo ra các cấu trúc này.

Doug Scott, phó chủ tịch cấp cao về bao bì cấp độ wafer tại cho biết: “Trụ đồng thường được sử dụng với khoảng cách dưới 130µm, vì thay vì là một mối hàn hình tròn, cột đồng chủ yếu là trụ Cu có mối hàn ở trên”. Công nghệ Amkor. “Điều này cho phép các trụ cột đồng được đặt gần nhau hơn mà không có nguy cơ mối hàn kết nối với nhau trong quá trình lắp ráp lại - nói chung là ~40 µm Cu + ~25 µm.”

Có nhiều biến thể về chủ đề. Mark Gerber, giám đốc cấp cao về kỹ thuật/tiếp thị kỹ thuật cho biết: “Microbump, một thuật ngữ phổ biến được sử dụng khi bạn có mối liên kết giữa silicon với silicon, hơi khác một chút vì CTE (hệ số giãn nở nhiệt) nhìn chung giống nhau”. Tại Nhóm ASE. “Một số quy tắc thiết kế chung được sử dụng cho cột đồng là giống nhau, nhưng địa hình bề mặt phẳng và các mối nối có ứng suất thấp cho phép sử dụng lớp lót dưới một cách linh hoạt. Điều này cũng có thể thúc đẩy cú va chạm của cá nhân. Ngày nay, có thể thực hiện được bước đệm toàn mảng 35µm do các cân nhắc về định tuyến đã đề cập trước đó đối với định tuyến cấp độ wafer hoặc cấp độ fab được sử dụng.”

Lộ trình tích hợp không đồng nhất [2] mô tả tất cả các khía cạnh của bao bì, bao gồm các kết nối từ khuôn đến nền, từ liên kết dây đến via xuyên silicon. Với các kết nối khuôn-bề mặt của gói chip lật, các khu vực phân phối lại chất nền và các kết nối từ nền-bảng mạch đều đóng một vai trò trong giới hạn sản xuất.

Hình 4: Sơ đồ khái niệm về đóng gói flip-chip. Nguồn: A. Meixner/Kỹ thuật bán dẫn

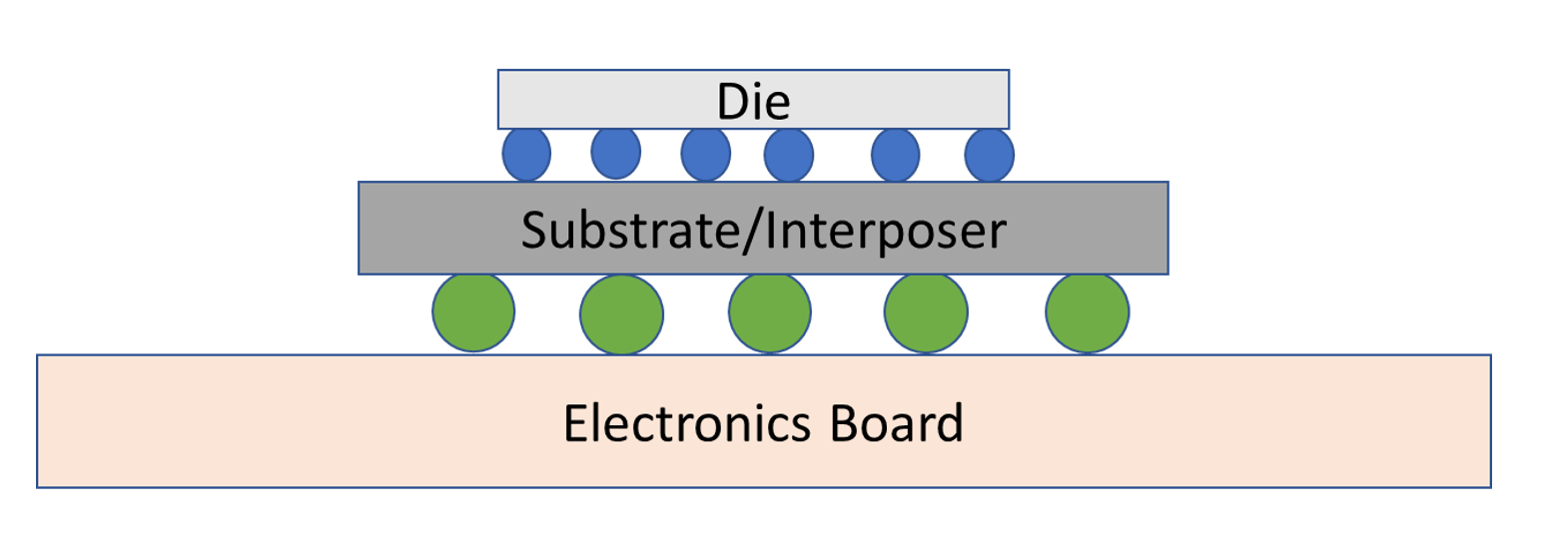

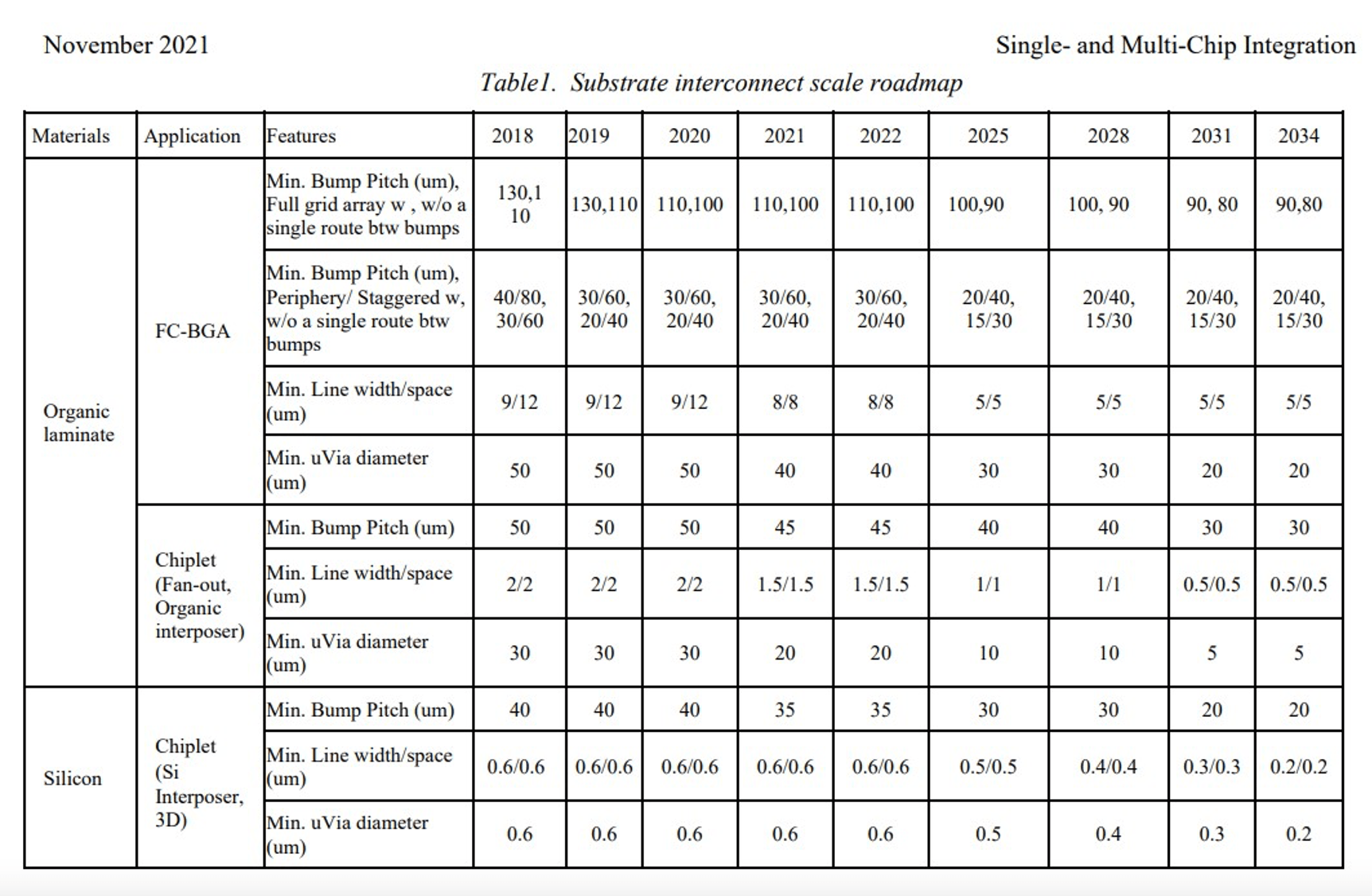

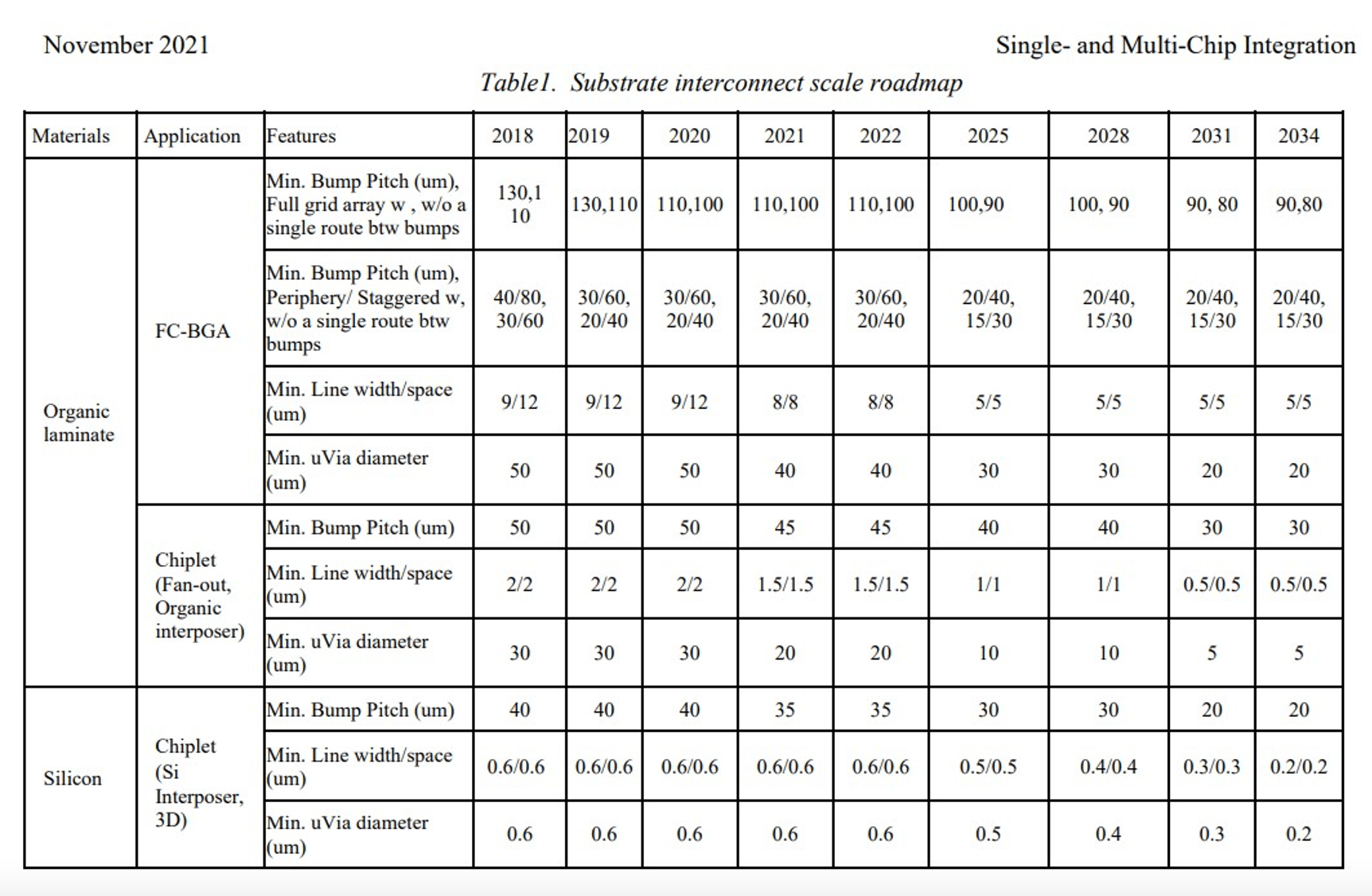

Chương 8 của Lộ trình tích hợp không đồng nhất [3] ghi lại bối cảnh của các giai đoạn công nghệ đóng gói hiện tại và dự kiến. Khoảng cách tối thiểu của mỗi công nghệ kết nối flip-chip được nêu trong Bảng 1 của tiểu mục 8.7 (trang 41).

![Chương 8 của Lộ trình tích hợp không đồng nhất [3] ghi lại bối cảnh của các giai đoạn công nghệ đóng gói hiện tại và dự kiến. Khoảng cách tối thiểu của mỗi công nghệ kết nối flip-chip được nêu trong Bảng 1 của tiểu mục 8.7 (trang 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Chương 8 của Lộ trình tích hợp không đồng nhất [3] ghi lại bối cảnh của các giai đoạn công nghệ đóng gói hiện tại và dự kiến. Khoảng cách tối thiểu của mỗi công nghệ kết nối flip-chip được nêu trong Bảng 1 của tiểu mục 8.7 (trang 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

Bảng tương ứng về kết nối chất nền (phần kết nối gói với bo mạch) được tìm thấy trong tiểu mục 8.8 (trang 43).

Mỗi thay đổi trong công nghệ kết nối đều xuất hiện các quy trình mới và những giới hạn của chúng, thúc đẩy sự đổi mới, quản lý năng suất và kiểm tra lỗi.

Giới hạn công nghệ va chạm

Công nghệ va đập được đo bằng cao độ, kích thước, chiều cao và các tính chất cơ và điện. Các cân nhắc về nhiệt khác nhau tùy thuộc vào sự không phù hợp của CTE của vật liệu. Cong vênh là mối lo ngại đối với khuôn và tấm bán dẫn lớn hơn, tình trạng này càng trở nên trầm trọng hơn do việc mài lại tấm bán dẫn trước khi gắn khuôn.

Gerber của ASE cho biết: “Có một số yếu tố dẫn đến giới hạn cao độ cho từng loại kết nối”. “Bắt đầu với kết nối chip lật va chạm hàn truyền thống, khả năng bước được xác định bằng chiều cao thu gọn để lấp đầy, ghi lại bước đệm để định tuyến dấu vết, ghi lại bước đệm để tránh rủi ro va đập ngắn và một số độ nhạy khác liên quan đến bước. Chiều cao của phần lồi được gắn sẵn có chiều cao xác định, nhưng như IBM đã xác định thuật ngữ C4 - Kết nối chip thu gọn có kiểm soát - đường kính của phần lồi hàn và kích thước miếng đệm sẽ xác định 'độ thu gọn hoặc chiều cao cuối cùng' của kết nối. Đây là yếu tố hạn chế bước chính khi sử dụng các mối hàn liên quan đến bước cao độ.”

Chiều cao vết sưng được xác định bởi thiết kế, nhưng cũng có những lựa chọn xử lý.

“Đối với các gờ hàn được mạ tiêu chuẩn và các gờ trụ đồng, chiều cao của gờ trước khi lắp ráp thường vào khoảng 70µm đến 75 µm, với chiều cao của gờ được thu gọn sau khi lắp ráp là ~50 µm để cho phép không gian x, y, z cho dòng chảy lấp đầy giữa các gờ. Các vết va chạm nhỏ sẽ có chiều cao vết va chạm thấp hơn nhiều và liên quan đến lớp mạ ít hơn nhiều. Cụ thể, các vết va chạm nhỏ có thể cao dưới 10µm với chiều cao Cu và mối hàn giảm tùy thuộc vào nhu cầu về bước và đầu cuối,” Scott của Amkor cho biết. “Các mối hàn được mạ tiêu chuẩn thường được sử dụng trên các bước có bước răng từ 130µm đến 250µm. Dưới 130µm, không có đủ khoảng cách x-y giữa các va chạm khi bắt đầu với chiều cao va đập trước khi lắp ráp là 70µm.”

Việc tạo ra các trụ đồng đòi hỏi nhiều bước xử lý hơn so với việc hàn các vết hàn.

“Khi chúng ta chuyển sang thế giới die-to-die, công nghệ đã khác vì bây giờ bạn đang xử lý một tấm wafer và các planit rất tốt so với die trên chất nền. Trước tiên, bạn tạo cột đồng, trên tấm bán dẫn ban đầu sẽ lấy chất hàn hoặc cột đồng, trước tiên phải có một kim loại bên dưới va chạm (UBM). Đó là một cái nắp nhỏ trên lỗ đi xuống silicon. Sau đó, chúng tôi chế tạo một lõi đồng từ đó và đậy nắp thiếc lên trên. Vì vậy, tấm wafer tiếp nhận, chúng trông giống như có một miếng đệm UBM ở đó và nó thường được mạ một số loại vàng niken trên đó để trông đẹp và nguyên sơ,” Schaefer của Promex Industries giải thích. Vì vậy, thay vì có một vết lõm nhẹ như bề mặt laminate, bạn sẽ có một vết lõm nhẹ. Chúng tôi nhận thấy rằng chúng tôi thực sự có thể hàn chúng ướt mà không cần 'hàn trên miếng đệm'. Đó là cách chúng được thiết kế và chế tạo. Nó gần như hoạt động giống như một vật hàn và miếng đệm vì nó là một mái vòm nhỏ thay vì cố gắng chui xuống bên trong một cái lỗ.”

Các bước quang khắc cần thiết cho quá trình hình thành cột Cu đều có những giới hạn cũng như các quy tắc thiết kế chất nền.

“Đối với cột đồng, bao gồm một cột đồng và một nắp hàn ở đầu, chiều cao của cột đồng có thể được xác định theo giới hạn của một hoặc nhiều độ dày lớp chống ảnh và khi bạn giảm bước, tỷ lệ khung hình của Chiều cao của cu post đến cao độ trở thành hạn chế cùng với khả năng của vật liệu chống ảnh và công cụ chụp ảnh,” Gerber nói. “Hạn chế thứ hai đối với kết nối trụ đồng là các quy tắc thiết kế nền được sử dụng. Đối với bước cao độ >110um, 2 phương pháp chính được sử dụng- BOT (Liên kết trên dấu vết) hoặc ET - Dấu vết nhúng, trong đó nắp hàn của cột đồng được đặt lên trên dấu vết thay vì tấm chụp truyền thống. Kích thước và hình dạng cột đồng, bao gồm cả những hạn chế ở trên, có thể tạo ra giới hạn về khả năng và lộ trình tiếp tục thu nhỏ các bước. Nhiều hạn chế trong số này là do khả năng định tuyến các dấu vết ở giữa các trụ trên mặt nền. Khi có các công nghệ mới, chẳng hạn như RDL cấp độ wafer, lộ trình kết nối sẽ được đẩy mạnh hơn nữa, nhưng vẫn còn những hạn chế về tỷ lệ chiều cao/khung hình đối với các quy trình sản xuất chẳng hạn như lấp đầy.”

Những người khác đồng ý rằng quá trình điền thiếu đi kèm với những thách thức. “Khi bạn có được những vết va chạm nhỏ hơn, chúng sẽ ngắn hơn. Hiện nay việc tìm phần đệm để chui vào bên dưới ngày càng khó khăn. Schaefer cho biết, các lớp lót trước đây được thiết kế để có khoảng cách dưới 5 triệu, và bây giờ chúng giảm xuống còn 3 triệu, tức là 75 micron”. “Bây giờ chúng tôi bắt đầu thấy những khoảng trống 60 và 25 micron. Tôi chắc chắn rằng mọi người đang làm việc trên các phần đệm mới. Nhưng có rất nhiều việc phải làm. Thứ nhất, khi bạn thu được các hạt mịn hơn, nó sẽ trở nên giống bùn hơn, khiến nó khó chảy hơn. Đây là rào cản cần được dỡ bỏ”.

Quản lý sản lượng

Khi công nghệ va chạm ngày càng nhỏ hơn, các bước xử lý bổ sung - ví dụ, in thạch bản để tạo ra các cột đồng - mở ra những cơ hội mới cho máy dò năng suất. Để có một quá trình liên kết thành công, các hạt, chất gây ô nhiễm bề mặt và vết hở của mối hàn là những vấn đề ảnh hưởng đến năng suất. Những điều này yêu cầu kiểm soát quy trình, đo lường và kiểm tra.

Kiểm soát ô nhiễm một cách tự nhiên là cần thiết. Scott của Amkor cho biết: “OSAT cấp 1 đầu tư để giảm mức độ ô nhiễm của nhà máy và do đó giảm tỷ lệ lỗi”. “Pitch không góp phần gây ra khiếm khuyết. Mức độ khiếm khuyết tương tự tồn tại bất kể cao độ.”

Nhưng cao độ cũng có thêm một số thách thức riêng. “Khi bước răng trở nên nhỏ hơn và kích thước vết sưng giảm, việc quản lý ô nhiễm hạt là rất quan trọng. Đối với các loại kết nối khác như liên kết lai, trong đó các bước giảm xuống dưới 30µm và tiếp xúc bề mặt với bề mặt là quan trọng, thì môi trường phòng sạch dựa trên tấm bán dẫn rất quan trọng đối với năng suất,” Gerber của ASE cho biết.

Không nên đánh giá thấp việc chuẩn bị cho quá trình điền đầy.

Schaefer của Promex cho biết: “Nói chung với tấm cán mỏng, bạn sẽ thực hiện thao tác lấp đầy phần dưới sau khi thực hiện lật chip. “Chúng tôi xác định nơi chúng tôi sẽ đặt nó và cách chỉnh lại nó. Chúng tôi làm sạch nó để loại bỏ bất kỳ vật liệu trợ dung nào dưới khe hở giữa khuôn và chất nền. Sau đó, chúng tôi sẽ lấp đầy bằng lớp epoxy chảy. Nó được thiết kế để làm ướt và không để lại khoảng trống và những thứ tương tự. Nhưng có một thách thức khi chúng tôi đạt được những cao độ tốt hơn. Các vết lồi ngắn hơn một chút và khi chúng ngắn hơn thì khoảng cách giữa chip và chất nền cũng nhỏ hơn, do đó khó làm sạch hơn. Hãy tưởng tượng dán hai tấm kính lại với nhau để cố gắng loại bỏ bụi bẩn giữa chúng.”

Nhu cầu đo lường và kiểm tra

Để quản lý việc kiểm soát và sản lượng quy trình, các công cụ đo lường và kiểm tra đóng một vai trò quan trọng. Gerber của ASE cho biết: “Có những công cụ hiện có trên thị trường có thể giúp cung cấp hướng dẫn về tính toàn vẹn của kết nối, ngoài việc phân tích mặt cắt ngang trong quá trình được sử dụng khi thiết lập và tại các khoảng thời gian sản xuất xác định”.

Mỗi quá trình va đập và quá trình liên kết đều có những đặc điểm cụ thể cần được theo dõi. Đối với các va chạm, phép đo tập trung vào đường kính, chiều cao và độ đồng phẳng. Các bước nhỏ hơn yêu cầu kiểm soát nghiêm ngặt hơn về đường kính va đập và kiểm soát chiều cao. Tương tự, khi chiều cao chỗ lồi co lại, cửa sổ đồng phẳng sẽ nhỏ hơn. Thông thường, cho phép sai số 10%. Ví dụ: chiều cao chỗ lồi lõm là 30µm dẫn đến sai số cho phép là ±3µm. Vượt quá mức này góp phần vào việc liên kết không thành công hoặc kém.

Mike Kelly, phó chủ tịch phụ trách tích hợp công nghệ và gói tiên tiến tại Amkor cho biết: “Việc liên kết thường được thực hiện bằng lò nung lại hàng loạt. “Đặc tính ban đầu của quá trình chỉnh lại dòng được thiết lập bằng cách sử dụng Shadow-Moire để định lượng độ cong vênh trong quá trình chỉnh lại dòng và lập bản đồ nhiệt độ của lò để đảm bảo kiểm soát nhiệt độ nhất quán của chính bộ phận chip lật. Trong quá trình thiết lập, nâng khuôn cơ học và kiểm tra để đảm bảo thực hiện làm ướt mối hàn tốt. Ngoài ra, từ thông thường được áp dụng với 'thông lượng nhúng', trong đó các khối khuôn được 'nhúng' vào các bể chứa từ thông mỏng, được kiểm soát chặt chẽ. Việc kiểm tra trực quan các hạng mục này được thực hiện trên cơ sở lấy mẫu.”

Việc tăng cường tự động hóa kiểm tra trực quan giúp giảm sự phụ thuộc vào người vận hành để xem hình ảnh và đưa ra quyết định. Sự gia tăng theo cấp số nhân của các kết nối va chạm là một yếu tố thúc đẩy. Những thay đổi trong quá trình liên kết mang lại một điều khác. Quá trình hàn nóng chảy tự liên kết là một công nghệ trưởng thành. Với liên kết nén nhiệt thường được sử dụng trong bao bì tiên tiến, có những cơ chế độ tin cậy đã vượt qua thử nghiệm về điện. Điều đó dẫn đến việc sử dụng các công cụ đo lường và kiểm tra bằng tia X để xem các vết lồi lõm sau khi liên kết.

“Đối với việc đóng gói có độ phức tạp thấp, các cơ sở có thể không cần người vận hành và kiểm tra thủ công. Đối với một bộ phận có 100 va chạm, phương pháp này có thể thực hiện được. Ở mức 1,000 va chạm, đó chắc chắn là một sự căng thẳng. Một khi một bộ phận có 10,000 va chạm thì sẽ không có cơ hội. Chúng ta đã vượt qua điểm này và cần chuyển sang phương pháp tiếp theo,” Frank Chen, giám đốc ứng dụng và quản lý sản phẩm tại Người dùng. “Chất lượng và độ phức tạp luôn đi đôi với nhau, bởi vì khi bạn cố gắng tạo ra thứ gì đó phức tạp hơn, năng suất của bạn sẽ bị ảnh hưởng và sẽ cần có một số công cụ mới. Và công cụ có nghĩa là cả công cụ xử lý và công cụ đo lường, vì vậy cả hai đều cần được phát triển song song. Từ nghiên cứu của chính mình, chúng tôi thấy rằng khi bạn vượt qua 1,000 va chạm đó, đó là lúc bạn cần bắt đầu suy nghĩ ‘Kỹ thuật thủ công của tôi chưa đủ và tôi cần thứ gì đó mới.’”

Hiện có nhiều công cụ kiểm tra và đo lường khác nhau để hỗ trợ sản xuất bao bì.

“Có một số phương pháp có thể hoặc nên được sử dụng để đạt được sự kiểm soát quá trình. Đầu tiên, kiểm tra 2D truyền thống (AOI) để kiểm tra 100% khuyết tật bề mặt trên mỗi quy trình (tức là IQC, OQA, ảnh, làm sạch, mạ, v.v.). Tiếp theo, có thể sử dụng phép đo 2D (AOI) để kiểm soát kích thước vết sưng và kích thước đường kính điều khiển. Hơn nữa, đo lường 3D (AOI) có thể được sử dụng để thu thập thông tin đo lường chiều cao vết sưng lấy mẫu/đồng phẳng (điều này thường được thực hiện bằng công nghệ dựa trên tam giác laser),” Nathan Peng, giám đốc tiếp thị sản phẩm tại Để đổi mới. “Hơn nữa, đo lường 3D có thể nhắm mục tiêu các đặc điểm chiều cao va đập riêng lẻ, thường được thu thập bằng công nghệ giao thoa kế ánh sáng trắng. Ngoài ra, còn có các phương pháp cho phép phát hiện dư lượng hữu cơ trên phần đầu lồi có thể dẫn đến hỏng kết nối giữa các tấm đệm.”

Kết luận

Các sản phẩm yêu cầu số lượng kết nối cao hơn tiếp tục thúc đẩy lộ trình kết nối. Mỗi công nghệ chip lật đều có các giới hạn sản xuất liên quan đến đặc tính vật liệu, thu nhỏ kích thước thách thức các công nghệ lấp đầy và tăng cường sử dụng kỹ thuật in thạch bản để tạo ra các cấu trúc kết nối. Bất kỳ thay đổi nào trong quy trình liên kết đều dẫn đến sự gia tăng các bước đo lường và kiểm tra để đáp ứng các mục tiêu về năng suất và chất lượng.

dự án

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Chương 8 Tích hợp chip đơn và đa chip, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Nhưng câu chuyện liên quan:

Tính đồng phẳng và sự không nhất quán gây ra các vấn đề về năng suất, độ tin cậy

Những thách thức về đóng gói nâng cao ngày càng tăng khi chip và kích thước gói hàng ngày càng thu hẹp; thiết bị, công nghệ khác nhau đạt được sức hút.

Độ tin cậy của Bump bị thách thức bởi các lỗi tiềm ẩn

Các giải pháp tự động đang được triển khai nhưng sẽ mất thời gian để phát triển.

Những thay đổi lớn phía trước trong việc cung cấp điện, vật liệu và kết nối

Sản xuất và đóng gói sẽ thay đổi như thế nào trong vài thập kỷ tới

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Đúc kết tương lai với Adryenn Ashley. Truy cập Tại đây.

- Mua và bán cổ phần trong các công ty PRE-IPO với PREIPO®. Truy cập Tại đây.

- nguồn: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- : có

- :là

- :không phải

- :Ở đâu

- $ LÊN

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- có khả năng

- Có khả năng

- ở trên

- Đạt được

- mua lại

- Hoạt động

- hành vi

- thực sự

- Ngoài ra

- thêm vào

- Thêm

- tiến

- tiên tiến

- Sau

- trước

- KHÔNG KHÍ

- sắp xếp

- Tất cả

- cho phép

- cho phép

- dọc theo

- Ngoài ra

- an

- phân tích

- và

- Một

- bất kì

- các ứng dụng

- áp dụng

- LÀ

- KHU VỰC

- khu vực

- xung quanh

- AS

- khía cạnh

- các khía cạnh

- hợp ngữ

- At

- đính kèm

- Tự động hóa

- có sẵn

- xa

- trở lại

- banh

- cơ bản

- cơ sở

- BE

- bởi vì

- trở thành

- được

- trước

- được

- phía dưới

- giữa

- Ngoài

- lớn

- bảng

- trái phiếu

- Bot

- cả hai

- xây dựng

- xây dựng

- nhưng

- by

- đến

- CAN

- mũ lưỡi trai

- khả năng

- nắm bắt

- Nguyên nhân

- thách thức

- thách thức

- thách thức

- cơ hội

- thay đổi

- Những thay đổi

- Chương

- đặc điểm

- chen

- Chip

- Snacks

- sự lựa chọn

- lựa chọn

- gần gũi hơn

- Sự sụp đổ

- sụp đổ

- Đến

- đến

- Chung

- thông thường

- so

- phức tạp

- phức tạp

- các thành phần

- máy tính

- khái niệm

- Liên quan

- Kết nối

- Kết nối

- liên quan

- Kết nối

- connect

- sự cân nhắc

- thích hợp

- liên lạc

- chất gây ô nhiễm

- tiếp tục

- tiếp tục

- Góp phần

- điều khiển

- kiểm soát

- kiểm soát

- điều khiển

- Copper

- Trung tâm

- Tương ứng

- có thể

- Couple

- tạo

- tạo ra

- Tạo

- quan trọng

- Current

- Hiện nay

- dữ liệu

- xử lý

- thập kỷ

- quyết định

- xác định

- chắc chắn

- giao hàng

- Nhu cầu

- mật độ

- Tùy

- ký gửi

- Thiết kế

- thiết kế

- Phát hiện

- Xác định

- xác định

- phát triển

- phát triển

- Thiết bị (Devices)

- Die

- khác nhau

- khó khăn

- Giám đốc

- bụi bẩn

- do

- tài liệu

- làm

- thực hiện

- xuống

- lái xe

- trình điều khiển

- trình điều khiển

- hai

- suốt trong

- e

- E&T

- mỗi

- hay

- nhúng

- cho phép

- cho phép

- cuối

- ky sư

- Kỹ Sư

- đủ

- đảm bảo

- Môi trường

- Trang thiết bị

- thành lập

- vv

- Ether (ETH)

- phát triển

- ví dụ

- tồn tại

- mở rộng

- mong đợi

- đắt tiền

- Giải thích

- số mũ

- cơ sở

- yếu tố

- nhà máy

- Không

- Sung

- cuối cùng

- Tìm kiếm

- cuối

- Tên

- bằng phẳng

- Linh hoạt

- Lật

- dòng chảy

- Chảy

- Tuôn ra

- tập trung

- Trong

- cho năng suất

- hình thành

- tìm thấy

- từ

- xa hơn

- Hơn nữa

- Thu được

- khoảng cách

- khoảng trống

- Tổng Quát

- nói chung

- được

- nhận được

- ly

- Go

- Đi

- đi

- Gói Vàng

- tốt

- mài

- Phát triển

- hướng dẫn

- xử lý

- Cứng

- Có

- có

- cao

- chiều cao

- giúp đỡ

- Cao

- hiệu suất cao

- cao hơn

- lịch sử

- Lô

- NÓNG BỨC

- Độ đáng tin của

- Hướng dẫn

- HTML

- HTTPS

- Hỗn hợp

- i

- IBM

- IEEE

- hình ảnh

- hình ảnh

- Hình ảnh

- tác động

- quan trọng

- in

- Bao gồm

- Tăng lên

- tăng

- tăng

- lên

- hệ thống riêng biệt,

- thông tin

- ban đầu

- sự đổi mới

- thay vì

- hội nhập

- tính toàn vẹn

- kết nối

- trong

- Đầu tư

- liên quan

- IT

- mặt hàng

- ITS

- chính nó

- cảnh quan

- lớn hơn

- tia laser

- lớp

- dẫn

- Rời bỏ

- ít

- Cấp

- niveaux

- ánh sáng

- Lượt thích

- LIMIT

- giới hạn

- hạn chế

- giới hạn

- ít

- dài

- Xem

- giống như

- Rất nhiều

- Thấp

- Chủ yếu

- làm cho

- LÀM CHO

- quản lý

- giám đốc

- quản lý

- nhãn hiệu

- thủ công

- sản xuất

- nhiều

- lập bản đồ

- dấu

- thị trường

- Marketing

- vật liệu

- nguyên vật liệu

- trưởng thành

- max-width

- có nghĩa

- cơ khí

- cơ chế

- Gặp gỡ

- cuộc họp

- Bộ nhớ

- đề cập

- kim loại

- phương pháp

- phương pháp

- Đo lường

- micron

- làm biếng

- tối thiểu

- di động

- theo dõi

- chi tiết

- chủ yếu

- di chuyển

- di chuyển

- nhiều

- đa

- Thiên nhiên

- Cần

- cần thiết

- nhu cầu

- Mới

- Công nghệ mới

- tiếp theo

- tốt đẹp

- Nickel

- Không

- lưu ý

- tại

- con số

- mục tiêu

- of

- on

- hàng loạt

- ONE

- mở

- mở

- nhà điều hành

- khai thác

- Cơ hội

- phản đối

- or

- hữu cơ

- ban đầu

- Nền tảng khác

- vfoXNUMXfipXNUMXhfpiXNUMXufhpiXNUMXuf

- ra

- kết thúc

- riêng

- gói

- gói

- bao bì

- tập giấy

- trang

- Song song

- một phần

- hạt

- vượt qua

- người

- cột

- Pitch

- nốt

- Nơi

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- Play

- Điểm

- người nghèo

- Phổ biến

- sự lựa chọn phổ biến

- định vị

- có thể

- Bài đăng

- quyền lực

- Chủ tịch

- chính

- Trước khi

- quá trình

- Quy trình

- xử lý

- Sản phẩm

- quản lý sản phẩm

- Sản lượng

- Sản phẩm

- dự

- tài sản

- cho

- đẩy

- đặt

- chất lượng

- khác nhau,

- tỉ lệ

- đạt

- có thật không

- nhận

- giảm

- Giảm

- làm giảm

- Bất kể

- liên quan

- độ tin cậy

- sự phụ thuộc

- Đã loại bỏ

- yêu cầu

- cần phải

- đòi hỏi

- Kết quả

- Nguy cơ

- lộ trình

- lộ trình

- Vai trò

- Phòng

- Route

- định tuyến

- quy tắc

- Nói

- tương tự

- trung học

- xem

- nhìn thấy

- đã xem

- bán dẫn

- cao cấp

- thiết lập

- một số

- Hình dạng

- thay đổi

- ngắn

- nên

- bên

- Tín hiệu

- Silicon

- tương tự

- Tương tự

- kể từ khi

- duy nhất

- Kích thước máy

- kích thước

- Slides

- hơi khác nhau

- nhỏ hơn

- So

- Giải pháp

- một số

- một cái gì đó

- Chẳng bao lâu

- nguồn

- nguồn

- Không gian

- riêng

- đặc biệt

- Tiêu chuẩn

- Bắt đầu

- Bắt đầu

- Các bước

- dính

- Vẫn còn

- Những câu chuyện

- căng thẳng

- nghiên cứu

- thành công

- như vậy

- hỗ trợ

- Bề mặt

- SVG

- bàn

- Hãy

- Mục tiêu

- Công nghệ

- Công nghệ

- kỳ hạn

- Kiểm tra

- hơn

- việc này

- Sản phẩm

- Phong cảnh

- cung cấp their dịch

- Them

- chủ đề

- sau đó

- Đó

- vì thế

- nhiệt

- Kia là

- họ

- điều

- Suy nghĩ

- điều này

- những

- Tuy nhiên?

- chặt lấy

- thời gian

- tip

- đến

- bây giờ

- bên nhau

- công cụ

- công cụ

- hàng đầu

- theo dõi

- lực kéo

- truyền thống

- thử

- XOAY

- hai

- kiểu

- loại

- thường

- Dưới

- trên

- sử dụng

- đã sử dụng

- sử dụng

- thường

- sử dụng

- nhiều

- rất

- Phó Chủ Tịch

- Xem

- vô hiệu

- là

- we

- TỐT

- khi nào

- cái nào

- trắng

- toàn bộ

- phổ biến rộng rãi

- Wikipedia

- sẽ

- với

- không có

- Công việc

- đang làm việc

- công trinh

- thế giới

- X

- X-quang

- Năng suất

- sản lượng

- bạn

- trên màn hình

- zephyrnet