S2C є світовим лідером у створенні прототипів FPGA вже майже два десятиліття, і його платформи для створення прототипів FPGA уважно відстежують доступність найновіших FPGA, включаючи найновіші FPGA від Xilinx і Intel. І вони точно виконують обіцянку просувати свої рішення для прототипування для прототипування гіпермасштабного дизайну – нарощування прототипування можливостей платформи та можливостей для підтримки багатомільярдних конструкцій воріт.

Озираючись на початок 4-го кварталу 2020 року, S2C оголосила про підтримку нових на той час ПЛІС Xilinx VU19P UltraScale+, що пропонують платформи для створення прототипів ПЛІС з одинарною, подвійною та четвірною платформами. Потім, у грудні 2020 року, S2C оголосила про свою високощільну сімейство платформ прототипування Prodigy Logic Matrix з 8 FPGA на логічну матрицю, 8 логічних матриць на одну серверну стійку (64 FPGA) і з’єднанням кількох серверні стійки разом. Перші ітерації Logic Matrix були доставлені з Xilinx VU440 FPGA (названі LX1) першим клієнтам, які не могли дочекатися версії VU19P (названої LX2).

Тепер S2C розширює свою гру Logic Matrix із LX2, що збільшує корисну пропускну здатність прототипу на 60% порівняно з версією VU440! Більше корисних вентилів на FPGA означає менше FPGA, менше з’єднань FPGA та вищу продуктивність для того самого прототипу. З орієнтовною пропускною здатністю 392 мільйони воріт на LX2, повністю заповнена стандартна серверна стійка з 8 LX2 дозволяє створювати прототипи понад 3 мільярдів ASIC-шлюзів!

Рисунок 1: Prodigy Logic Matrix LX2

| Prodigy Logic Matrix Family | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Приблизні ворота ASIC (M) | 240 | 392 |

| Кількість ПЛІС | 8 | 8 |

| Системні логічні комірки (K) | 44,328 | 71,504 |

| Пам'ять FPGA (Мб) | 709 | 1,327.2 |

| Зрізи DSP | 23,040 | 30,720 |

| Зовнішні користувачі введення/виведення | 9,216 | 10,368 |

| Трансивери SerDes | 384 GTH | 640 GTY |

| Роз'єми Prodigy | 64 | 72 |

| Роз'єми PGT | 8 | 0 |

| Роз'єми трансиверів | 80 MSAS кожен з 4 GTH + 8 IO | 160 MCIO кожен з 4 GTY + 8 IO |

| Продуктивність SerDes | 16 Gbps | 28 Gbps |

Рисунок 2: Сімейство логічних матриць

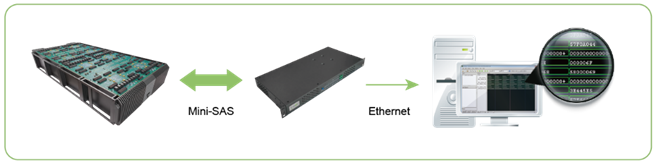

Гнучке високошвидкісне з’єднання є ключовим для створення прототипів FPGA з високою щільністю, а Logic Matrix підтримує ієрархічну 3-рівневу стратегію з’єднання: ШортБрідж для з'єднання між сусідніми FPGA; SysLink для з'єднання кабелю FPGA з високою пропускною здатністю та TransLink для з’єднання FPGA SerDes на великій відстані через кабелі MCIO. Щоб спростити з’єднання FPGA і максимізувати цінність TransLink, потік розділення S2C підтримує нещодавно представлену Xilinx високошвидкісну трансиверну пін-мультиплексацію (HSTPM), що спрощує передачу сигналу з точністю до циклу, пін-мультиплексування та підключення SerDes FPGA з низькою затримкою.

Щоб мінімізувати час створення прототипів і максимально підвищити продуктивність створення прототипів, інші інструменти S2C для підвищення продуктивності прототипування розроблені з урахуванням логічної матриці, включаючи Player Pro Runtime програмне забезпечення та додаткові інструменти створення прототипів S2C ProtoBridge, MDM Proі S2C Готовий прототип IP.

Player Pro Runtime програмне забезпечення входить до складу LX2, що забезпечує такі зручні функції, як розширене керування годинником, інтегроване самотестування, автоматичне виявлення плати, програмування напруги вводу/виводу, кілька завантажень FPGA, а також віддалений моніторинг і керування системою. Також включено AXEVision, вбудований інструмент налагодження AXI-over-Ethernet для спрощення віддаленого налагодження проектів, пов’язаних з AXI.

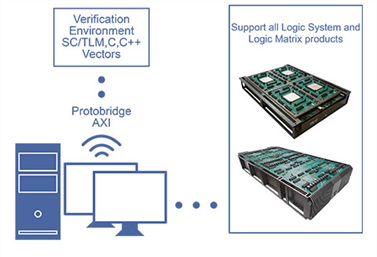

ProtoBridge підтримує високу пропускну здатність передачі даних (до 1 ГБ/с) між головним ПК і LX2 – можливість передачі великої кількості транзакцій, змодельованих програмним забезпеченням, відеопотоків або інших тестових стимулів для перевірки системи.

Рисунок 3: ProtoBridge

MDM Pro включає глибоке налагодження трасування з перехресними тригерами до восьми FPGA, перегляд трасування сигналу кількох FPGA з одного вікна перегляду, 64 ГБ зовнішнього сховища сигналів трасування, частоту дискретизації трасування до 125 МГц і підтримку мов кінцевих автоматів тригерів для складних захоплень трасування вимоги.

Рисунок 4: MDM Pro

S2C також пропонує багату бібліотеку Готовий прототип IP для LX2 – дочірні карти plug-and-play, що прискорюють створення середовища прототипування навколо прототипу FPGA.

Малюнок 5: Прототип готових дочірніх карт IP

Prodigy Logic Matrix LX2 доступний зараз. Щоб отримати додаткову інформацію, зверніться до місцевого торгового представника S2C або відвідайте веб-сайт www.s2ceda.com.

Поділитися цим дописом через: Джерело: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Додатковий

- оголошений

- Оголошення

- навколо

- Основниеопераціі

- наявність

- Мільярд

- рада

- Кабелі

- потужність

- зв'язку

- зв'язок

- Клієнти

- дані

- надання

- дизайн

- Виявлення

- відстань

- Рано

- Навколишнє середовище

- сім'я

- риси

- Фіга

- Перший

- потік

- FPGA

- гра

- Гейтс

- Глобальний

- HTTPS

- У тому числі

- інформація

- Intel

- IP

- ключ

- мови

- великий

- останній

- бібліотека

- місцевий

- управління

- Матриця

- мільйона

- моніторинг

- пропонує

- Пропозиції

- Інше

- PC

- продуктивність

- платформа

- Платформи

- Pro

- продуктивність

- Інструменти для

- Програмування

- макетування

- ставки

- Вимога

- продажів

- нарощувати

- Софтвер

- Рішення

- стан

- стимул

- зберігання

- Стратегія

- потоки

- підтримка

- Опори

- система

- тест

- Transactions

- значення

- Відео

- чекати

- ВООЗ