Розробники аналогових мікросхем можуть витрачати занадто багато часу та зусиль на повторне використання старих, знайомих методів ручної ітерації для проектування схем, лише тому, що це завжди робилося. Оптимізація ланцюга – це підхід EDA, який може автоматично підбирати розміри всіх транзисторів у комірці, запускаючи моделювання SPICE через кути PVT і варіації процесу, щоб відповідати вимогам до дизайну аналогових і змішаних сигналів. Звучить багатообіцяюче, чи не так?

Отже, який оптимізатор схеми мені слід розглянути щодо використання?

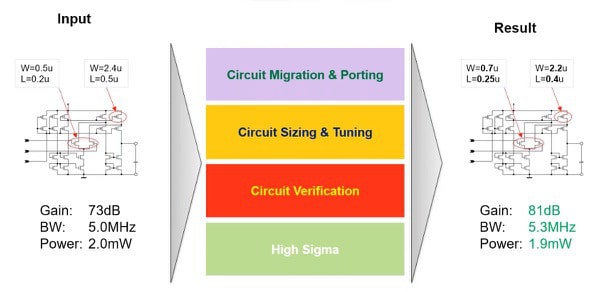

Щоб відповісти на це запитання, планується вебінар, організований MunEDA, компанія EDA розпочала роботу ще в 2001 році, і вся справа в оптимізаторі схем під назвою WiCkeD. Вхідними даними є список з’єднань SPICE разом із вимогами до дизайну, як-от коефіцієнт підсилення, пропускна здатність та енергоспоживання. Виходи — це список з’єднань розміром, який відповідає або перевищує вимоги до дизайну.

Секрет WiCkeD полягає в тому, як він створює модель машинного навчання (ML) для запуску Design Of Experiments (DOE) для обчислення найгіршого кута PVT, визначення чутливості геометрії транзистора та навіть обчислення варіації On Chip (OCV). ) чутливість. Цей підхід створює та оновлює нелінійну багатовимірну модель машинного навчання із змодельованих даних.

Наявність моделі ML дозволяє інструменту вирішити проблему оптимізації, а потім виконати остаточну перевірку за допомогою моделювання SPICE. Виконуються автоматичні ітерації, доки не будуть виконані всі вимоги. Тепер це звучить набагато швидше, ніж старі методи ручної ітерації. Навчання моделі ML відбувається автоматично й досить ефективно.

Розробники схем також дізнаються:

- Де використовувати оптимізацію схеми

- Які типи схем добре оптимізувати

- Яку цінність оптимізація ланцюга приносить у процес проектування

Інженери STMicroelectronics використали оптимізацію схеми в WiCkeD, і MunEDA розповідає про їхні конкретні результати щодо економії часу та покращення виконання вимог. Компанія з виробництва підсилювачів потужності Inplay Technologies показала результати оптимізації схеми на конференції DAC 2018.

Деталі веб-семінару

Перегляньте вебінар 11 квітня о 10:XNUMX за тихоокеанським літнім часом реєстрація онлайн.

Блоги, пов'язані

Поділитися цим дописом через:

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- Платоблокчейн. Web3 Metaverse Intelligence. Розширені знання. Доступ тут.

- джерело: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :є

- $UP

- 2001

- 2018

- a

- МЕНЮ

- через

- ВСІ

- завжди

- та

- відповідь

- підхід

- квітня

- ЕСТЬ

- At

- Автоматизований

- автоматичний

- автоматично

- назад

- ширина смуги

- оскільки

- Приносить

- Будує

- by

- обчислювати

- CAN

- виклик

- чіп

- майбутній

- компанія

- конференція

- Вважати

- споживання

- Кут

- кути

- створює

- дані

- дизайн

- Дизайнери

- DOE

- ефективний

- зусилля

- дозволяє

- Навіть

- перевищувати

- знайомий

- швидше

- остаточний

- знайти

- потік

- для

- від

- Отримувати

- геометрія

- добре

- Мати

- відбувся

- Як

- HTTPS

- i

- поліпшення

- in

- IT

- ітерація

- ітерації

- JPG

- УЧИТЬСЯ

- вивчення

- як

- машина

- навчання за допомогою машини

- керівництво

- макс-ширина

- Зустрічатися

- засідання

- відповідає

- методика

- ML

- модель

- Названий

- of

- Старий

- on

- оптимізація

- plato

- Інформація про дані Платона

- PlatoData

- пошта

- влада

- процес

- продуктивність

- перспективний

- питання

- Вимога

- результати

- прогін

- біг

- Економія

- секрет

- Повинен

- моделювання

- Розмір

- конкретний

- витрачати

- спеції

- почалася

- Переговори

- Технології

- Що

- Команда

- їх

- час

- до

- занадто

- інструмент

- Навчання

- Типи

- Updates

- використання

- значення

- перевірка

- через

- шлях..

- webinar

- який

- волі

- з

- зефірнет