Коли ви думаєте «FPGA», що спадає на думку? Масивні, дорогі деталі, здатні вмістити багато логіки, але також споживають багато енергії. Реконфігуровані платформи, які можуть проковтнути RTL для дизайну SoC під час попереднього тестування кремнію. Великі гучні корпоративні придбання, на яких інвестори заробили купу грошей. Екзотична 3D-упаковка та передові з’єднання. Але, мабуть, недешево, невелика упаковка, мала кількість контактів, низький рівень живлення в режимі очікування, чи не так? eFPGA від Flex Logix повертається до основ програмованої логіки з низьким енергоспоживанням, яка може працювати з пристроями меншої вартості, більшого об’єму та розміру.

На вибір представлені дві програмовані дороги

Ризикую почати зустрічатися з собою. Моє перше знайомство з тим, що тоді називалося технологією FPGA, відбулося тоді, коли Altera випустила сімейство EPROM EP1200 на основі EPROM у 40-контактному корпусі DIP із тактовою частотою 16 МГц, активною потужністю 400 мВт і 15 мВт у режимі очікування. потужність. Він поставлявся з редактором схем і бібліотекою макросів воріт. Дизайнери малювали свою логіку, «спалювали» свою деталь, тестували її, кидали під УФ-лампу і стирали, якщо вона не працювала, і пробували знову.

Незабаром після цього в іншій нашій лабораторії з’явилася плата з одними з перших FPGA Xilinx. Вони базувалися на оперативній пам’яті замість EPROM – більші, швидші та перепрограмування без очікування УФ-лампи чи видалення деталі з плати. Внутрішня логіка також була складнішою із запровадженням швидких множників. Ці частини могли б не тільки підмітати логіку, але також могли б бути використані для дослідження можливостей нестандартної обробки цифрового сигналу за допомогою швидких циклів редизайну.

Це поклало початок гонці програмованих кремнієвих озброєнь і роздвоєнню між PLD – програмованим логічним пристроєм – і FPGA. Виробники зробили вибір: Altera та Xilinx пішли на шлях масштабованості FPGA, а Actel, Lattice та інші вибрали нижчий шлях гнучкості PLD для «з’єднувальної логіки», щоб зменшити витрати на перелік матеріалів.

eFPGA змінює малопотужне програмоване логічне рівняння

Все це схоже на зрілий ринок, з високим бар’єром для входу на один кінець і більш товарною пропозицією з іншого. Але що, якби програмована логіка була блоком IP, який можна було б спроектувати в будь-який чіп у цю епоху безпереробних технологій, включаючи невелику малопотужну FPGA? Це дозволить обійти бар’єр (принаймні в пропозиціях низького та середнього цінового діапазону) і комодитизацію.

Компанія Flex Logix впоралася з цим викликом із плиткою EFLX 1K eFPGA. Кожна логічна плитка має 560 таблиць пошуку з шістьма входами (LUT) з оперативною пам’яттю, синхронізацією та з’єднанням. Розміщення фрагментів EFLX дає можливість працювати з різними логікою та ролями DSP. Але найвидатнішими характеристиками можуть бути його розмір і керування живленням.

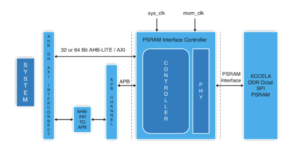

Виготовлена з TSMC 40ULP плитка EFLX 1K вміщується в 1.5 мм2 і пропонує блокування живлення для режимів глибокого сну зі збереженням стану – набагато агресивніше, ніж традиційні PLD. EFLX 1K також має готові до виробництва функції, запозичені з FPGA. Він представляє інтерфейси AXI або JTAG для конфігурації бітового потоку, схему зворотного зчитування, що забезпечує м’яку перевірку помилок, і тестовий режим із спрощеними векторами, що покращує охоплення та скорочує час тестування.

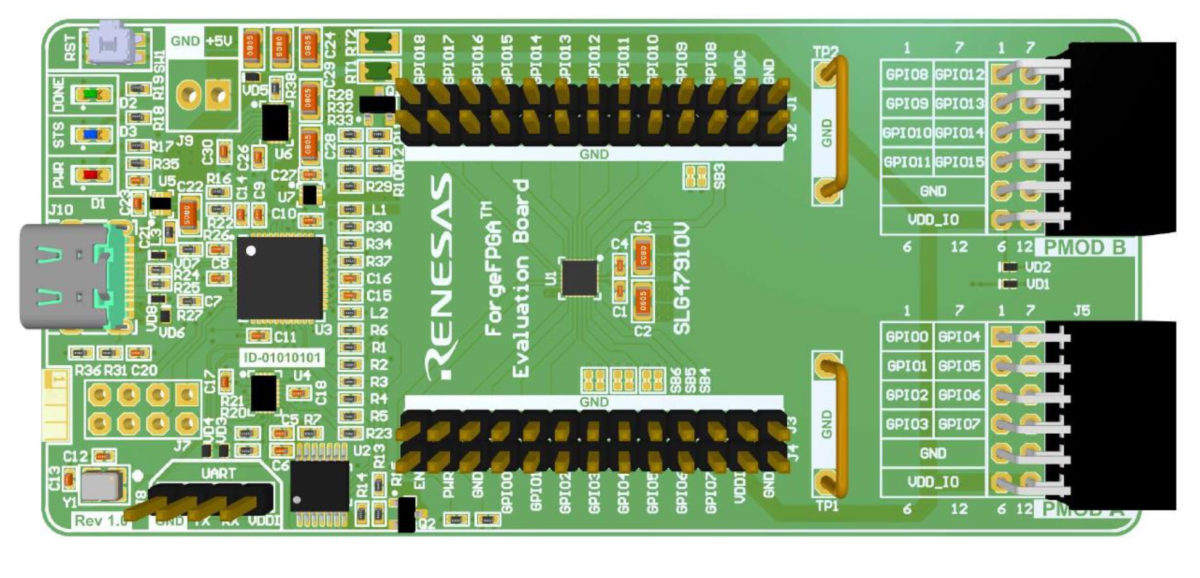

Бачите мікросхему в центрі наступного зображення? Це ForgeFPGA від Renesas у пакеті QFN-24 на основі EFLX 1K IP, який Renesas пропонує за ціною нижче 1 долара. Його цільовий струм очікування становить менше 20 мкА. Менший розмір, менша вартість і менша потужність відкривають двері, раніше закриті для FPGA. Родовід ForgeFPGA веде свій початок від Silego Technology, а потім від Dialog Semiconductor, придбаної Renesas у 2021 році.

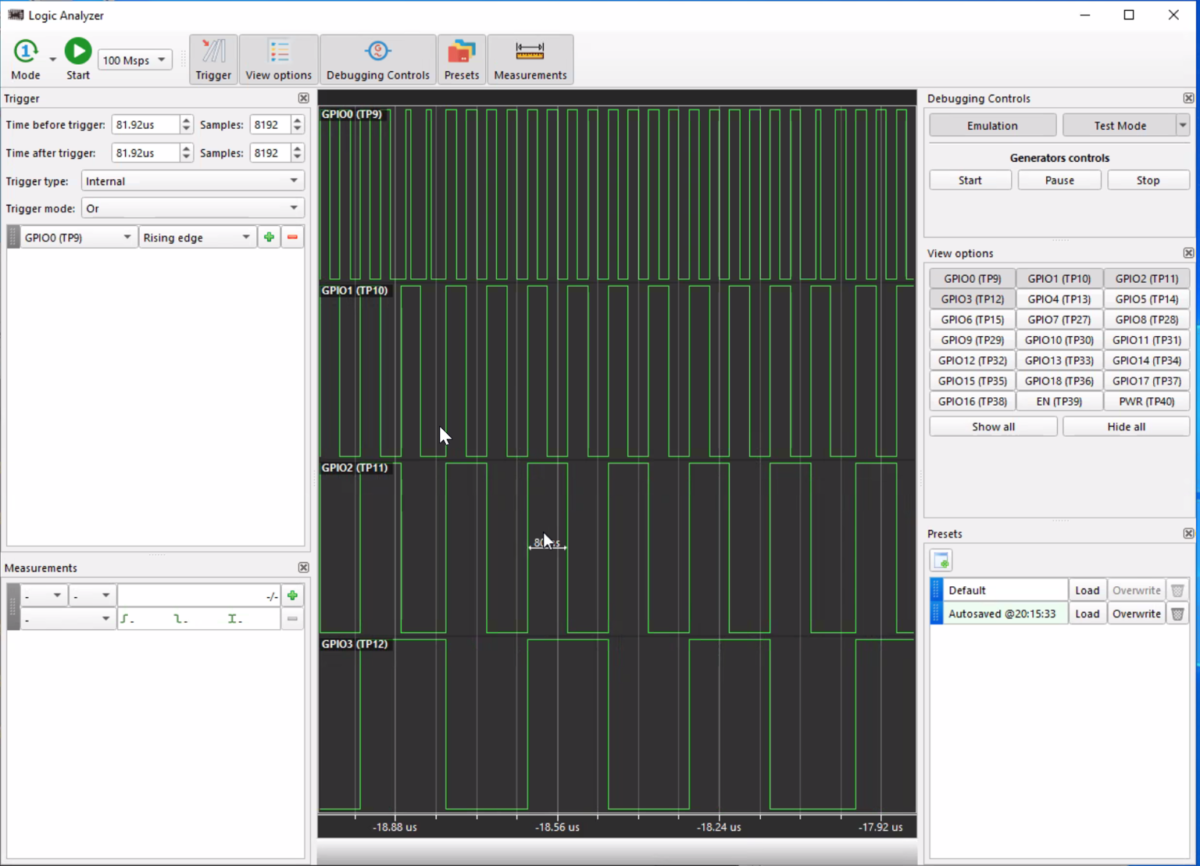

Renesas пропонує середовище Go Configure IDE, розміщуючи графічний інтерфейс користувача поверх компілятора Flex Logix EFLX. Він підтримує відображення контактів ForgeFPGA, компіляцію Verilog, генерацію бітового потоку та має легкий логічний аналізатор.

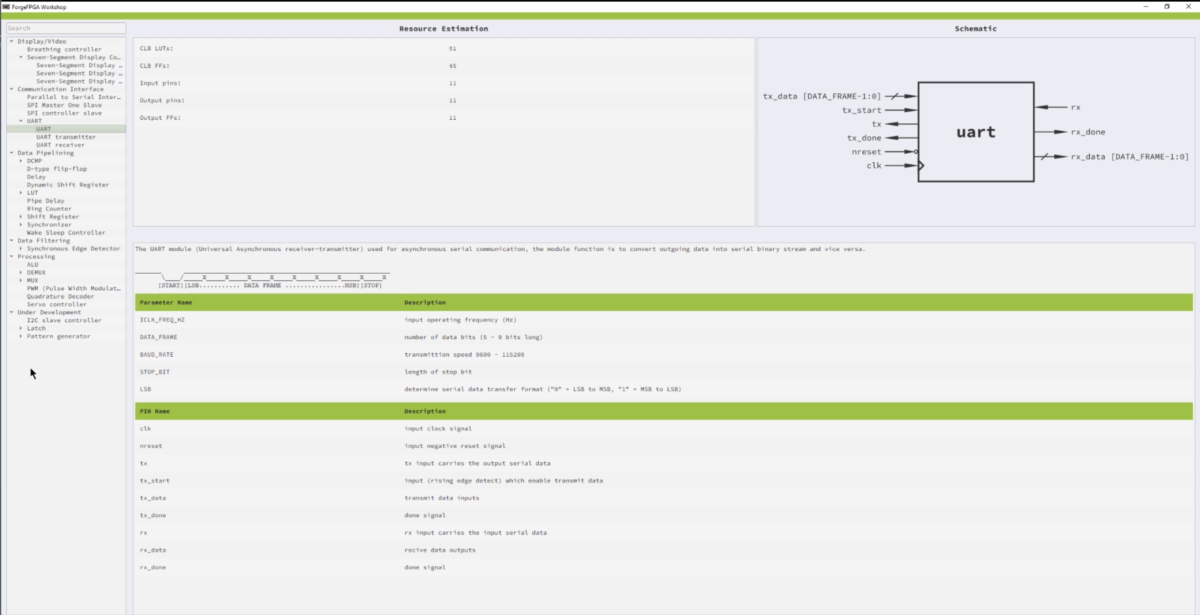

Попередньо створені блоки додатків для ForgeFPGA мають цікавий, на який вказує Джефф Тейт з Flex Logix: UART. Створити UART за логікою не так вже й складно, але виявилося, що всі підійшли до цього по-різному, і логіки достатньо, щоб бути більше, ніж пара дискретних мікросхем. ForgeFPGA — це частина реконфігурованої логіки, яка може вирішити цю проблему, дозволяючи одній апаратній реалізації швидко адаптуватися до різних конфігурацій.

ForgeFPGA є лише одним із прикладів того, що можна зробити за допомогою Flex Logix EFLX 1K eFPGA Tile. Flex Logix може адаптувати IP-адресу для різних вузлів процесу, а можливість комбінування та підбору плиток забезпечує масштабованість. Він досягає нових низьких показників для програмованої логіки з низьким енергоспоживанням і дозволяє виробникам чіпів дивовижно диференціювати рішення. Для отримання додаткової інформації відвідайте:

Сімейство Flex Logix EFLX eFPGA

Також читайте:

eFPGA, що обробляють крипто-гнучкість для SoC з PQC

Flex Logix: перша в галузі система на базі Mini-ITX, інтегрована штучним інтелектом

Flex Logix співпрацює з внутрішнім ідентифікатором для захисту платформи eFPGA

Поділитися цим дописом через:

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- Платоблокчейн. Web3 Metaverse Intelligence. Розширені знання. Доступ тут.

- джерело: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :є

- $UP

- 1

- 2021

- 3d

- a

- здатність

- МЕНЮ

- про це

- Досягає

- придбаний

- поглинань

- активний

- пристосовувати

- просунутий

- після

- агресивний

- AI

- ВСІ

- Дозволити

- дозволяє

- та

- Інший

- додаток

- At

- назад

- бар'єр

- заснований

- Основи

- BE

- між

- Великий

- більший

- Блокувати

- блоки

- рада

- запозичений

- Приносить

- приніс

- by

- званий

- CAN

- здатний

- Центр

- виклик

- контроль

- Перевірки

- чіп

- Чіпси

- вибір

- годинник

- закрито

- комплекс

- конфігурація

- Корпоративний

- Коштувати

- витрати

- може

- Пара

- охоплення

- створення

- Поточний

- виготовлений на замовлення

- циклів

- датування

- глибокий

- дизайн

- призначений

- Дизайнери

- розвиненою

- пристрій

- прилади

- Діалог

- диференціювати

- важкий

- цифровий

- нахил

- Двері

- кожен

- редактор

- дозволяє

- досить

- запис

- Навколишнє середовище

- Епоха

- помилка

- оцінка

- все

- приклад

- Екзотичний

- дорогий

- дослідити

- експонування

- сім'я

- ШВИДКО

- швидше

- риси

- Перший

- Гнучкість

- для

- FPGA

- від

- породжує

- дає

- Go

- йде

- обробляти

- Обробка

- апаратні засоби

- Мати

- Високий

- вище

- проведення

- HTTPS

- ID

- зображення

- реалізація

- поліпшення

- in

- У тому числі

- промисловості

- недорогий

- інформація

- замість

- інтегрований

- цікавий

- інтерфейс

- Інтерфейси

- сутнісний

- Вступ

- Інвестори

- IP

- IT

- ЙОГО

- JPG

- тільки один

- Labs

- бібліотека

- легкий

- як

- серія

- низький

- зниження

- Найнижчі

- Macro

- макроси

- made

- Makers

- управління

- Виробники

- відображення

- ринок

- масивний

- зрілий

- макс-ширина

- mind

- режим

- Режими

- гроші

- більше

- найбільш

- Нові

- наступний

- вузли

- of

- пропонує

- Пропозиції

- Пропозиції

- on

- ONE

- відкрити

- Інше

- інші

- пакет

- упаковка

- частина

- партнери

- частини

- сосна

- Платформи

- plato

- Інформація про дані Платона

- PlatoData

- будь ласка

- точок

- пошта

- влада

- представлений

- подарунки

- раніше

- price

- ймовірно

- Проблема

- процес

- обробка

- видатний

- Поклавши

- швидко

- Гонки

- Оперативна пам'ять

- швидко

- Читати

- переконструювати

- зменшити

- чудовий

- видалення

- утримання

- Risk

- дорога

- доріг

- ролі

- масштабованість

- безпечний

- напівпровідник

- комплект

- Зміни

- Сигнал

- Кремній

- Розмір

- сон

- невеликий

- менше

- М'який

- Рішення

- ВИРІШИТИ

- деякі

- стан

- обтічний

- Опори

- Розгортки

- Приймати

- взяття

- Мета

- Технологія

- тест

- Тестування

- Що

- Команда

- їх

- Ці

- times

- до

- Тон

- топ

- традиційний

- tsmc

- при

- користувач

- Інтерфейс користувача

- різний

- через

- візит

- обсяг

- чекати

- способи

- Що

- який

- з

- без

- Work

- б

- зефірнет