Протягом 2010-го десятиліття переваги закону Мура почали розпадатися. Відповідно до закону Мура, щільність транзисторів подвоюється кожні два роки, вартість обчислень зменшуватиметься на відповідні 50%. Зміна в законі Мура пов'язана зі збільшенням складності конструкції еволюцією структури транзисторів від плоских пристроїв до Finfets. Finfets потребують кількох шаблонів для літографії, щоб досягти розмірів пристроїв нижче 20-нм вузлів.

На початку цього десятиліття потреби в обчислювальних ресурсах різко зросли, головним чином через поширення центрів обробки даних і через обсяг даних, які генеруються та обробляються. Насправді впровадження штучного інтелекту (AI) і таких методів, як машинне навчання (ML), тепер використовуються для обробки постійно зростаючого обсягу даних і призвело до значного збільшення обчислювальної потужності серверів.

Сервери додали багато ядер ЦП, інтегрували більші графічні процесори, які використовуються виключно для ML, які більше не використовуються для графіки, і мають вбудовані користувацькі прискорювачі ASIC AI або додаткову обробку AI на основі FPGA. Ранні конструкції чіпів штучного інтелекту були реалізовані з використанням більших монолітних SoC, деякі з них досягали обмеження розміру, встановленого візильною сіткою, близько 700 мм.2.

На даний момент правильним рішенням є поділ на меншу SoC плюс різні обчислювальні мікросхеми та чіплети вводу-виводу. Кілька виробників чіпів, як-от Intel, AMD або Xilinx, вибрали цю опцію для продуктів, які запускаються у виробництво. У чудовому документі The Linley Group «Швидке впровадження чіплетів: чому великі мікросхеми стають маленькими» було показано, що цей варіант веде до кращих витрат порівняно з монолітними SoC через вплив більших розмірів на продуктивність.

Основний вплив цієї тенденції на постачальників IP здебільшого стосується функцій з’єднання, які використовуються для зв’язку SoC і чіплетів. На даний момент (3 квартал 2021 р.) використовується кілька протоколів, і галузь намагається створити формалізовані стандарти для багатьох із них.

Поточні провідні стандарти D2D включають: i) розширену інтерфейсну шину (AIB, AIB2), спочатку розроблену Intel, а тепер пропонує безкоштовне використання, ii) пам’ять високої пропускної здатності (HBM), де матриці DRAM накладаються одна на одну поверх кремнієвого інтерпозера. і підключені за допомогою TSV, iii) Підгрупа Open Domain-Specific Architecture (ODSA), промислова група, визначила два інші інтерфейси, Bunch of Wires (BoW) і OpenHBI.

Гетерогенний дизайн чіплетів дозволяє нам орієнтуватися на різні додатки або сегменти ринку, змінюючи або додаючи лише відповідні чіплети, залишаючи решту системи незмінною. Нові розробки можна було б швидше вивести на ринок із значно меншими інвестиціями, оскільки модернізація вплине лише на підкладку упаковки, яка використовується для розміщення мікросхем.

Наприклад, обчислювальний чіплет можна переробити з TSMC 5nm на TSMC 3nm, щоб інтегрувати більший кеш L1 або високопродуктивні ядра ЦП, зберігаючи при цьому решту системи без змін. На протилежному кінці спектра лише чіплет, що інтегрує SerDes, може бути перероблений для швидшої швидкості на нових вузлах процесу, що пропонує більшу пропускну здатність вводу-виводу для кращого позиціонування на ринку.

Intel PVC є чудовим прикладом гетерогенної інтеграції (різні функціональні мікросхеми, ЦП, комутатори тощо), яку ми можемо назвати вертикальною інтеграцією, коли той самий виробник мікросхем володіє різними компонентами мікросхем (за винятком пристроїв пам’яті).

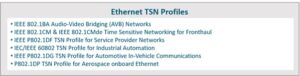

Виробники мікросхем, які розробляють SoC для високотехнологічних додатків, таких як HPC, центри обробки даних, штучний інтелект або мережі, ймовірно, першими приймуть архітектури чіплетів. Спеціальні функції, такі як SRAM для більшого кешу L3 або прискорювачі штучного інтелекту, стандарти Ethernet, PCIe або CXL повинні бути першим кандидатом на інтерфейс для чіплетів.

Коли ці перші користувачі продемонструють дієвість гетерогенних чіплетів, що використовують різні бізнес-моделі, і, очевидно, можливість виробництва для тестування та упаковки, буде створена екосистема, яка є критично важливою для підтримки цієї нової технології. На даний момент ми можемо очікувати ширшого впровадження на ринку не лише для високопродуктивних програм.

Ми можемо уявити, що різнорідні продукти можуть піти далі, якщо виробник мікросхем випустить на ринок систему, яка складається з різних чіплетів, націлених на обчислення та функціональність вводу-виводу. Цей підхід робить конвергенцію на протоколі D2D обов’язковою, оскільки постачальник IP, що пропонує чіплети з власним протоколом D2D, не є привабливим для галузі.

Аналогією з цим є створення SoC у 2000-х роках, коли напівпровідникові компанії переходили до інтеграції різних проектів IP, що надходять з різних джерел. Постачальники IP 2000-х неминуче стануть постачальниками чіплетів 2020-х. Для певних функцій, таких як розширені SerDes або складні протоколи, такі як PCIe, Ethernet або CXL, постачальники IP мають найкращі ноу-хау для реалізації цього на кремнії.

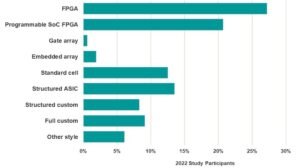

Для комплексного дизайну IP, навіть якщо перевірка моделювання була запущена перед відправкою клієнтам, постачальники повинні перевірити IP на кремнії, щоб гарантувати ефективність. Для цифрового IP цю функцію можна реалізувати в FPGA, оскільки це швидше та набагато дешевше, ніж виготовлення тестової мікросхеми. Для мікс-сигналу IP, як-от PHY на основі SerDes, постачальники вибирають опцію Test Chip (TC), що дозволяє кремнію характеризувати IP у кремнії перед відправкою клієнту.

Незважаючи на те, що чіплет — це не просто TC, тому що перед використанням у польових умовах він буде ретельно перевірений і кваліфікований, обсяг додаткової роботи, яку має виконати постачальник для розробки серійного чіплета, набагато менший. Іншими словами, постачальник IP має найкраще положення для того, щоб швидко випустити чіплет, створений на основі його власної IP, і запропонувати найкращий TTM і мінімізувати ризик.

Бізнес-модель гетерогенної інтеграції надає перевагу різним чіплетам, створеним відповідним постачальником IP (наприклад, ARM для чіплетів ЦП на основі ARM, Si-Five для чіплетів на основі Risc-V і Alphawave для високошвидкісних чіплетів SerDes), оскільки вони є власниками Design IP.

Ніщо з цього не заважає виробникам чіпів розробляти власні чіплети та проектувати IP-адреси вихідних комплексів, щоб захистити свої унікальні архітектури або впроваджувати власноруч створені міжсистемні з’єднання. Подібно до SoC Design IP у 2000-х роках, рішення про купівлю або виготовлення чіплетів буде зважено між захистом основних компетенцій та пошуком недиференційованих функцій.

Ми бачили, що історичне та сучасне зростання бізнесу Design IP з 2000-х років підтримувалося постійним впровадженням зовнішніх джерел. Обидві моделі будуть співіснувати (чіплет, розроблений власними силами або постачальником IP), але історія показала, що рішення про купівлю врешті-решт приймає рішення.

Зараз у галузі існує консенсус щодо того, що маніакальна зосередженість на досягненні закону Мура більше не діє для вузлів передових технологій, наприклад. 7 нм і нижче. Інтеграція чіпів все ще відбувається, додаючи більше транзисторів на квадратний міліметр у кожному новому технологічному вузлі. Однак вартість транзистора також зростає з кожним новим вузлом.

Технологія чіплетів є ключовою ініціативою для посилення інтеграції для основної системи на процесорі з використанням старих вузлів для інших функцій. Ця гібридна стратегія знижує як вартість, так і ризик проектування, пов’язаний з інтеграцією інших проектних IP безпосередньо в основний SoC.

IPnest вважає, що ця тенденція матиме два головних наслідки для ІР-бізнесу інтерфейсів: одним буде значне зростання доходів від D2D IP найближчим часом (2021-2025), а іншим – створення гетерогенного ринку чіплетів для розширення висококласного кремнію. Ринок ІВ.

Очікується, що цей ринок складатиметься з функцій складних протоколів, таких як PCIe, CXL або Ethernet. Постачальники IP-провайдерів, які надають інтерфейс IP, інтегрований у системи вводу-виводу SoC (USB, HDMI, DP, MIPI тощо), можуть замість цього вирішити поставити чіплети вводу-виводу.

Іншими категоріями IP, на які вплине ця революція, будуть постачальники IP компіляторів пам’яті SRAM для кешу L3. За своєю природою розмір кешу залежить від процесора. Тим не менш, розробка мікросхеми кеш-пам’яті L3 може бути способом для постачальника IP збільшити доходи від Design IP, пропонуючи новий тип продукту.

Крім того, можна позитивно вплинути на категорію NVM IP, оскільки NVM IP більше не інтегровано в SoC, розроблені на розширених вузлах процесу. Це був би спосіб для постачальників NVM IP створити новий бізнес, пропонуючи чіплети.

Ми вважаємо, що мікросхеми FPGA та прискорювачів штучного інтелекту стануть новим джерелом доходу для виробників чіпів ASSP, але ми не вважаємо, що їх можна строго класифікувати як постачальників IP.

Якщо постачальники Interface IP будуть головними учасниками цієї кремнієвої революції, кремнієві ливарні заводи, що працюють із найсучаснішими вузлами, такими як TSMC і Samsung, також відіграватимуть ключову роль. Ми не думаємо, що ливарні заводи розроблятимуть чіплети, але вони можуть прийняти рішення підтримувати постачальників IP і підштовхнути їх до розробки чіплетів для використання з SoC у 3 нм, як це роблять сьогодні, коли підтримують постачальників просунутих IP для продажу своїх висококласних SerDes. як жорсткий IP в 7 нм і 5 нм.

Нещодавній перехід Intel на 3rd Очікується, що сторонні ливарні заводи також використовуватимуть сторонні IP-адреси, а також прийняття гетерогенних чіплетів напівпровідниками. У цьому випадку, безсумнівно, такі Hyperscalars, як Microsoft, Amazon і Google, також приймуть архітектури чіплетів... якщо вони не випередять Intel у прийнятті чіплетів.

By Ерік Естев (к.т.н.) Аналітик, Власник IPnest

Поділитися цим дописом через: Джерело: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- прискорювач

- прискорювачі

- Прийняття

- Просунута технологія

- AI

- Дозволити

- Amazon

- AMD

- аналітик

- застосування

- архітектура

- ARM

- штучний інтелект

- Штучний інтелект (AI)

- Основниеопераціі

- КРАЩЕ

- будувати

- Створюємо

- гроно

- bus

- бізнес

- бізнес-модель

- купити

- call

- потужність

- зміна

- чіп

- Чіпси

- майбутній

- Компанії

- обчислення

- обчислення

- Консенсус

- витрати

- Клієнти

- дані

- надання

- дизайн

- розвивати

- прилади

- цифровий

- Рано

- ранні усиновлювачі

- екосистема

- і т.д.

- еволюція

- Перший

- Сфокусувати

- FPGA

- Безкоштовна

- функція

- Графічні процесори

- Group

- Зростання

- Зростання

- Високий

- історія

- будинок

- HTTPS

- гібрид

- Impact

- Augmenter

- промисловість

- Ініціатива

- інтеграція

- Intel

- Інтелект

- інвестиції

- IP

- IT

- зберігання

- ключ

- запуск

- закон

- провідний

- вивчення

- Led

- Важіль

- LINK

- навчання за допомогою машини

- основний

- виробник

- Робить

- виробництво

- ринок

- Microsoft

- ML

- модель

- мережа

- новий продукт

- вузли

- пропонувати

- пропонує

- відкрити

- варіант

- Інше

- власник

- упаковка

- Папір

- продуктивність

- Product

- Production

- Продукти

- захист

- захист

- ставки

- переконструювати

- REST

- Risk

- прогін

- Samsung

- напівпровідник

- Доставка

- моделювання

- Розмір

- стандартів

- Стратегія

- підтримка

- перемикач

- система

- Мета

- методи

- Технологія

- тест

- топ

- us

- USB

- постачальники

- перевірка

- біла книга

- слова

- Work

- років

- вихід