Раніше я писав у блозі про Функціональна перевірка IC та ASIC, тому сьогодні настав час завершити це станом функціональної перевірки FPGA. Wilson Research Group збирає звіт про FPGA кожні два роки, починаючи з 2018 року, тож це вже третій раз, коли вони зосереджуються на цьому сегменті дизайну. Ринок FPGA становить 5.8 мільярда доларів США чималий і, за прогнозами, до 8.1 року зросте до 2025 мільярда доларів США. FPGA почали створюватися в 1984 році з обмеженою пропускною здатністю воріт, а зараз вони включають мільйони воріт, процесорів і стандартизованих протоколів даних.

Невеликі додатки отримують переваги від NRE пристроїв FPGA, і інженери можуть швидко створювати прототипи своїх конструкцій шляхом швидкої перевірки та перевірки. FPGA тепер включають такі процесори, як: Xilinx Zynq UltraSCALE, Intel Stratix, Мікрочіп SmartFusion. Серед 980 учасників дослідження функціональної перевірки найпопулярнішими є стилі дизайну FPGA та програмованого SoC FPGA.

Оскільки розмір FPGA останнім часом зріс, шанс випуску без помилок знизився лише до 17%, що навіть гірше, ніж 30% проектів IC та ASIC для правильного першого кремнію. Очевидно, що нам потрібна краща функціональна перевірка складних систем FPGA.

Типи помилок, виявлених у виробництві, поділяються на кілька категорій:

- 53% – Логічні або функціональні

- 31% – Прошивка

- 29% – Тактування

- 28% – час, надто повільний шлях

- 21% – час, занадто швидкий шлях

- 18% – інтерфейс зі змішаним сигналом

- 9% – функція безпеки

- 8% – функція безпеки

Збільшуючись до найбільшої категорії збоїв, логічних чи функціональних, можна виділити п’ять основних причин.

Проекти FGPA здебільшого не завершувалися вчасно, знову ж таки через більший розмір систем, складність логіки та навіть використовуваних методів перевірки.

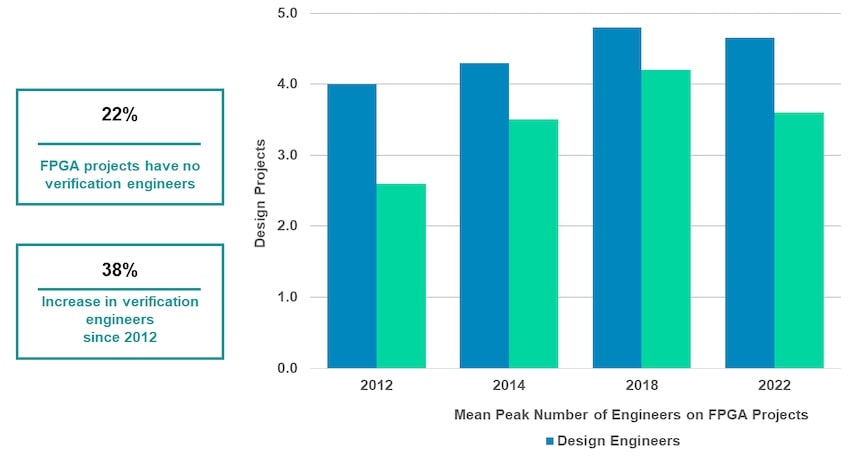

Інженери в команді FPGA можуть мати різні титули, як-от інженер-конструктор або інженер з верифікації, однак у 22% проектів інженерів з верифікації не було, тобто інженери-конструктори виконували подвійні обов’язки та перевіряли власну інтелектуальну власність. За останні 10 років кількість інженерів з верифікації проекту FPGA зросла на 38%, тож це прогрес у напрямку виробництва без помилок.

Інженери з верифікації проектів FPGA витрачали більшу частину свого часу на завдання налагодження – 47%:

- 47% – Налагодження

- 19% – Створення тесту та виконання симуляції

- 17% – розробка Testbench

- 11% – Планування тестування

- 6% – інше

Кількість вбудованих процесорів постійно зростала з часом, тому 65% проектів FPGA зараз мають одне або більше процесорних ядер, що збільшує кількість перевірки між апаратним забезпеченням, програмним інтерфейсом; і управління мережами на чіпі.

Завжди популярний процесор RISC-V вбудовано в 22% FPGA, а прискорювачі ШІ використовуються в 23% проектів. Існує 3-4 середня кількість тактових доменів, що використовуються на ПЛІС, і вони вимагають симуляції синхронізації на рівні воріт для перевірки, а також використання інструментів статичного перетину домену тактового сигналу (CDC) для перевірки.

Функції безпеки додано до 49% проектів FPGA для зберігання конфіденційних даних, а також 42% проектів FPGA дотримуються важливих стандартів або вказівок щодо безпеки. На SemiWiki ми часто вели блоги ISO 26262 та ДО-254 стандарти. Розробка функціональної безпеки (FuSa) займає від 25% до 50% загального часу проекту.

Трьома найкращими мовами перевірки є VHDL, SystemVerilog і Verilog; але також зверніть увагу на нещодавні стрибки в мовах Python і C/C++.

Найпопулярнішими методологіями FPGA та базовими бібліотеками тестового стенду є Accellera UVM, OSVVM та UVVM. На основі Python cocotb було навіть додано як нову категорію на 2022 рік.

Мови тверджень лідирують із SystemVerilog Assertions (SVA) з 45%, за нею йде Accellera Open Verification Library (OVL) з 13% і PSL з 11%. Конструкції FPGA можуть поєднувати VHDL для дизайну RTL разом із SVA для тверджень.

Формальна перевірка властивостей зростає серед проектів FPGA, особливо тому, що постачальники EDA представили більше автоматичних формальних програм.

Підходи верифікації на основі моделювання протягом останніх 10 років демонструють постійне впровадження, перераховані в порядку відповідності: покриття коду, функціональне покриття, твердження, обмежене випадкове.

Підсумки

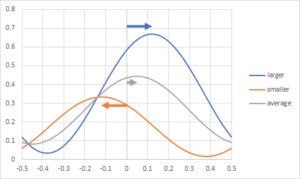

Низький показник відсутності помилок у проектах FPGA у 17 році, які були запущені у виробництво, був для мене найбільш несподіваним показником у 2022%, оскільки спроби відкликати або перепрограмувати пристрій у польових умовах є дорогим і трудомістким для виправлення. Більш надійний підхід функціональної перевірки повинен призвести до зменшення кількості помилок у виробництві, і поділ учасників дослідження на дві групи справді показує переваги.

Прочитайте повністю 18 сторінок білого паперу тут.

Блоги, пов'язані

Поділитися цим дописом через:

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- Платоблокчейн. Web3 Metaverse Intelligence. Розширені знання. Доступ тут.

- джерело: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- МЕНЮ

- прискорювачі

- доданий

- дотримуватися

- Прийняття

- AI

- серед

- кількість

- та

- застосування

- підхід

- підходи

- додатка

- Основниеопераціі

- автоматичний

- середній

- буття

- користь

- Краще

- між

- Мільярд

- Помилка

- помилки

- потужність

- категорії

- Категорія

- Викликати

- викликаний

- Причини

- CDC

- шанс

- контроль

- очевидно

- годинник

- код

- об'єднувати

- повний

- комплекс

- складність

- охоплення

- створення

- критичний

- дані

- дизайн

- конструкцій

- пристрій

- прилади

- DID

- чіткий

- домен

- домени

- впав

- зусилля

- зусилля

- вбудований

- інженер

- Інженери

- особливо

- Навіть

- Кожен

- дорогий

- Провал

- Падати

- риси

- поле

- Перший

- увагу

- потім

- формальний

- знайдений

- FPGA

- від

- функціональний

- Гейтс

- Group

- Групи

- Рости

- Зростання

- вирощений

- керівні вказівки

- апаратні засоби

- тримати

- HTML

- HTTPS

- in

- включати

- Augmenter

- збільшений

- зростаючий

- Intel

- Інтерфейси

- введені

- IP

- IT

- скачки

- мови

- більше

- найбільших

- вести

- Led

- libraries

- бібліотека

- обмеженою

- Перераховані

- низький

- made

- управління

- ринок

- макс-ширина

- сенс

- методології

- методика

- мільйони

- більше

- найбільш

- Найбільш популярний

- Необхідність

- мереж

- Нові

- номер

- ONE

- відкрити

- порядок

- загальний

- власний

- Папір

- Учасники

- Минуле

- шлях

- plato

- Інформація про дані Платона

- PlatoData

- плюс

- популярний

- пошта

- процесор

- процесори

- Production

- прогрес

- проект

- проектів

- власність

- протоколи

- прототип

- Python

- швидко

- випадковий

- останній

- нещодавно

- звільнити

- актуальність

- звітом

- вимагати

- дослідження

- дослідницької групи

- міцний

- корінь

- круглий

- біг

- Безпека

- безпеку

- сегмент

- чутливий

- кілька

- Повинен

- Показувати

- Шоу

- Сіменс

- Кремній

- з

- значний

- Розмір

- So

- Софтвер

- швидкість

- відпрацьований

- стандартів

- почалася

- стан

- стійкий

- Вивчення

- дивно

- Systems

- Приймати

- завдання

- команда

- методи

- тест

- Команда

- Держава

- їх

- третій

- три

- час

- синхронізація

- назви

- до

- сьогодні

- занадто

- інструменти

- топ

- до

- Типи

- використання

- постачальники

- перевірка

- перевірено

- перевірка

- через

- обсяг

- який

- білий

- біла книга

- Уїлсон

- років

- зефірнет