Naukowcy z Uniwersytetu w Lund opublikowali artykuł techniczny zatytułowany „Ferroelektryczne memrystory połączeń tunelowych dla akceleratorów obliczeniowych w pamięci”.

Abstrakcyjny:

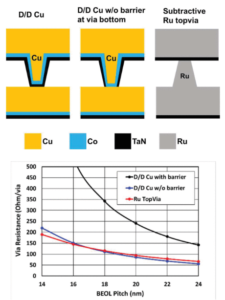

„Obliczenia neuromorficzne cieszą się dużym zainteresowaniem, ponieważ postęp w zastosowaniach sztucznej inteligencji (AI) ujawnił ograniczenia wynikające z dużego dostępu do pamięci w architekturze obliczeniowej von Neumanna. Równoległe przetwarzanie w pamięci zapewniane przez przetwarzanie neuromorficzne może znacząco poprawić opóźnienia i zużycie energii. Kluczem do analogowego neuromorficznego sprzętu komputerowego są memrystory, zapewniające nieulotne poziomy przewodności wielostanowej, dużą prędkość przełączania i efektywność energetyczną. Głównymi kandydatami do tego celu są memrystory ferroelektrycznych złącz tunelowych (FTJ), ale wpływ szczególnych właściwości na ich działanie po integracji z dużymi układami poprzecznymi, będącym głównym elementem obliczeniowym zarówno do wnioskowania, jak i uczenia w głębokich sieciach neuronowych, wymaga dokładnego zbadania. W tej pracy W/Hf x Zr1−x O2/TiN FTJ z 60 programowalnymi stanami przewodnictwa, zakresem dynamiki (DR) do 10, gęstością prądu >3 A m-2 at V czytać = 0.3 V i wysoce nieliniowe napięcie prądowo-napięciowe (I–V) charakterystykę (>1100) wykazano eksperymentalnie. Za pomocą makromodelu obwodu ocenia się wydajność prawdziwego układu poprzecznego na poziomie systemu i osiąga się 92% dokładność klasyfikacji zbioru danych Zmodyfikowanego Narodowego Instytutu Nauki i Technologii (MNIST). Wreszcie niska przewodność w połączeniu z wysoce nieliniową I–V Charakterystyka umożliwia realizację dużych, wolnych od selektorów tablic poprzecznych dla neuromorficznych akceleratorów sprzętowych.”

Znajdź papier techniczny tutaj. Opublikowano w grudniu 2023 r.

Athle, R. i Borg, M. (2023), Ferroelektryczne memrystory połączeń tunelowych dla akceleratorów obliczeniowych w pamięci. Adw. Intel. System. 2300554. https://doi.org/10.1002/aisy.202300554

Powiązane artykuły

Zwiększanie efektywności energetycznej AI dzięki przetwarzaniu w pamięci

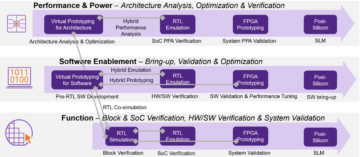

Jak przetwarzać obciążenia w skali zetta i nie przekraczać ustalonego budżetu mocy.

Modelowanie obliczeń w pamięci z wydajnością biologiczną

Generatywna sztuczna inteligencja zmusza producentów chipów do bardziej inteligentnego wykorzystywania zasobów obliczeniowych.

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiengineering.com/ferroelectric-tunnel-junctions-in-crossbar-array-analog-in-memory-compute-accelerators/

- :ma

- :Jest

- $W GÓRĘ

- 10

- 1100

- 2023

- 60

- a

- akceleratory

- dostęp

- precyzja

- osiągnięty

- AI

- i

- aplikacje

- architektura

- SĄ

- Szyk

- sztuczny

- sztuczna inteligencja

- Sztuczna inteligencja (AI)

- AS

- At

- obie

- budżet

- ale

- by

- kandydatów

- Charakterystyka

- klasyfikacja

- Zamknij

- połączenie

- obliczać

- computing

- konsumpcja

- rdzeń

- Aktualny

- grudzień

- głęboko

- głębokie sieci neuronowe

- wykazać

- gęstość

- cyfrowy

- dr

- z powodu

- dynamiczny

- efektywność

- element

- umożliwiać

- energia

- efektywności energetycznej

- oceniane

- narażony

- W końcu

- ustalony

- W razie zamówieenia projektu

- Siły

- wspaniały

- sprzęt komputerowy

- Have

- ciężki

- tutaj

- Wysoki

- wysoko

- HTTPS

- identyfikator

- Rezultat

- podnieść

- in

- Instytut

- integracja

- Inteligencja

- odsetki

- najnowszych

- śledztwo

- Klawisz

- duży

- Utajenie

- skoki

- poziom

- poziomy

- Ograniczenia

- niski

- Pamięć

- zmodyfikowano

- jeszcze

- naród

- sieci

- Nerwowy

- sieci neuronowe

- Nowości

- przedmiot

- of

- on

- koncepcja

- Papier

- Parallel

- szczególny

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- plato

- Analiza danych Platona

- PlatoDane

- potencjał

- power

- premia

- wygląda tak

- programowalny

- pod warunkiem,

- że

- opublikowany

- cel

- R

- zasięg

- realizacja

- Wymaga

- Badacze

- Zasoby

- nauka

- Nauka i technika

- widziany

- znacznie

- prędkość

- Zjednoczone

- pobyt

- system

- Techniczny

- Technologia

- Połączenia

- ich

- to

- pod tytulem

- do

- Trening

- prawdziwy

- tunel

- uniwersytet

- na

- posługiwać się

- za pomocą

- z

- była

- w

- w ciągu

- Praca

- zefirnet