Banias Labs er et halvlederselskap som utvikler infrastrukturløsninger for neste generasjons kommunikasjon. Målmarkedet er markedet for høyytelses datainfrastruktur inkludert hyperskala datasenter, nettverk, AI, optisk modul og Ethernet-svitsj SoCs for nye høyytelses databehandlingsdesign. Disse SoC-ene krever høyhastighets Ethernet-design og løsninger med lav latens for å gi økt systemytelse og akselerere time-to-market. Selskapet har utviklet en optisk DSP SoC på 5nm prosessteknologi for å møte kravene i dette markedet.

![]()

En optisk DSP SoC er en spesialisert type system-on-chip (SoC) designet for bruk i høyhastighets optiske kommunikasjonssystemer. I tillegg til DSP inkluderer den optiske DSP SoC vanligvis høyhastighets grensesnitt IP-blokker, slik som Ethernet PHY IP, PCIe IP og DDR minnekontrollere. Disse typene SoCer muliggjør høyhastighets dataoverføringer med lave ventetider for sanntidssignalbehandling. De er også designet for å minimere strømforbruket, noe som gjør dem ideelle for applikasjoner som krever effektiv drift med reduserte termiske problemer. Med fordelene følger også utfordringer. De spesialiserte kravene til optiske kommunikasjonssystemer gjør det mer utfordrende å designe en optisk DSP SoC enn å designe en vanlig SoC.

Implementeringsutfordringer

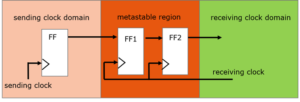

Utfordringene dreier seg om kompleksiteten i designet, de stramme kraft- og ytelseskravene, og behovet for å møte ulike industristandarder. Integreringen av flere IP-blokker inkludert DSP-prosessoren, Ethernet PHY IP og andre tilpassede blokker krever nøye design og validering. Ytterligere høyhastighetsgrensesnitt som PCIe og DDR øker kompleksiteten til designet. Høyhastighetsgrensesnittene og flere IP-blokker i systemet kan skape signalforvrengning, krysstale og elektromagnetisk interferens, noe som kan påvirke systemets ytelse og pålitelighet. Signal- og strømintegritetsanalyse og -optimalisering må utføres tidlig i designsyklusen for å sikre at systemet kan oppfylle kravene til ytelse og pålitelighet. Til slutt kan det være utfordrende å oppfylle krav til tid til marked. Markedet for høyytelses datainfrastruktur er i rask utvikling, og SoC-utviklingsteam må levere designene sine raskt for å ligge i forkant av konkurrentene.

Komme til First Pass Silicon Success

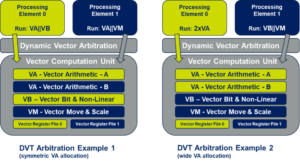

Å overvinne de ovennevnte utfordringene krever en helhetlig tilnærming. En av de kritiske komponentene i løsninger med høy ytelse og lav latens er Ethernet PHY IP. Ethernet PHY IP er ansvarlig for det fysiske laggrensesnittet mellom SoC og Ethernet-nettverket. IP-en må støtte høyhastighets Ethernet-grensesnitt, inkludert 10G, 25G, 40G, 50G, 100G, 200G, 400G og 800G, og gi lav ventetid og lavt strømforbruk. I tillegg må IP-en støtte ulike standarder, inkludert IEEE 802.3 og Ethernet Alliance. En annen viktig komponent er EDA-designpakken. EDA-designpakken må gi en omfattende løsning for utforming og verifisering av SoC, inkludert strømoptimalisering, ytelsesanalyse, områdeoptimalisering og avkastningsanalyse. I den grad inkluderer EDA-designsuiten avanserte funksjoner, som kunstig intelligens (AI) og maskinlæring (ML), jo bedre for økt produktivitet og redusert time-to-market.

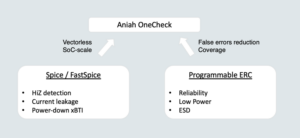

Synopsys akselererer First Pass Silicon Success

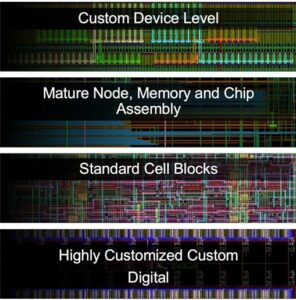

Synopsys tilbyr løsninger som adresserer de unike utfordringene med å utvikle SoC-er for høyytelses datainfrastrukturmarkedet. Selskapet tilbyr en omfattende IP-løsning som inkluderer en mulighetsstudie for ruting, retningslinjer for emballasjesubstrat, modeller for signal- og strømintegritet og grundig krysstaleanalyse. Dette er avgjørende for å møte utfordringene med signal- og strømintegritet når man utvikler en optisk DSP SoC. Synopsys' 112G Ethernet PHY IP tilbyr lav latenstid, fleksible rekkeviddelengder og modenhet på 5nm prosessteknologi, noe som gjør den til en ideell løsning for hyperskalering av datasenter, nettverk, AI, optisk modul og Ethernet-svitsj SoCs. I tillegg tilbyr Synopsys en EDA Design Suite som gir resultater av høy kvalitet med optimalisert kraft, ytelse, areal og utbytte. Synopsys' AI-drevne EDA Design Suite gir løsninger for å øke systemytelsen og akselerere time-to-market, noe som gjør den til en viktig komponent i en vellykket løsning for markedet for høyytelses datainfrastruktur.

Oppsummering

Synopsys tilbyr løsninger med høy ytelse og lav latens som akselererer utviklingen av avanserte Ethernet-svitsj- og nettverks-SoCs. For å lære mer om Synopsys' omfattende IP-løsninger, deres omfattende EDA Design Suite og deres AI-Enhanced EDA Suite, besøk de følgende sidene.

Synopsys sine omfattende IP-løsninger

Synopsys' omfattende EDA Suite

Synopsys' AI-drevne EDA Design Suite

Les også:

Multi-Die Systems: Den største forstyrrelsen i databehandling på mange år

Ta risikoen ved å utvikle din egen RISC-V-prosessor med rask, arkitekturdrevet PPA-optimalisering

Mater den voksende sulten etter båndbredde med høyhastighets Ethernet

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- Platoblokkkjede. Web3 Metaverse Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- kilde: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- : har

- :er

- a

- Om oss

- ovenfor

- akselerere

- akselererer

- tillegg

- Ytterligere

- I tillegg

- adresse

- avansert

- fordeler

- fremover

- AI

- Allianse

- også

- an

- analyse

- og

- En annen

- søknader

- tilnærming

- ER

- AREA

- rundt

- kunstig

- kunstig intelligens

- Kunstig intelligens (AI)

- AS

- At

- Båndbredde

- BE

- Bedre

- mellom

- Biggest

- Blocks

- øke

- CAN

- forsiktig

- sentrum

- utfordringer

- utfordrende

- Kom

- Kommunikasjon

- kommunikasjon

- Selskapet

- konkurranse

- kompleksitet

- komponent

- komponenter

- omfattende

- databehandling

- forbruk

- skape

- kritisk

- skikk

- syklus

- dato

- Datasenter

- leverer

- leverer

- utforming

- designet

- utforme

- design

- utviklet

- utvikle

- Utvikling

- utvikler

- Avbrudd

- Tidlig

- effektiv

- Emery

- muliggjøre

- forbedret

- sikre

- avgjørende

- utvikling

- møtt

- FAST

- Egenskaper

- Endelig

- Først

- fleksibel

- etter

- Til

- fra

- videre

- Økende

- retningslinjer

- høy ytelse

- høykvalitets

- HTML

- HTTPS

- sult

- ideell

- IEEE

- bilde

- Påvirkning

- avgjørende

- viktig

- in

- inkluderer

- Inkludert

- økt

- industri

- industristandarder

- Infrastruktur

- integrering

- integritet

- Intelligens

- Interface

- grensesnitt

- IP

- saker

- IT

- DET ER

- Labs

- Ventetid

- lag

- LÆRE

- læring

- Lav

- maskin

- maskinlæring

- gjøre

- Making

- marked

- modenhet

- max bredde

- Møt

- møte

- Minne

- nevnt

- ML

- modeller

- moduler

- mer

- flere

- Trenger

- nettverk

- nettverk

- neste generasjon

- of

- Tilbud

- on

- ONE

- drift

- optimalisering

- optimalisert

- Annen

- egen

- emballasje

- passere

- ytelse

- fysisk

- plato

- Platon Data Intelligence

- PlatonData

- Post

- makt

- prosess

- prosessering

- prosessor

- produktivitet

- gi

- gir

- raskt

- raskt

- å nå

- Lese

- sanntids

- Redusert

- regelmessig

- pålitelighet

- krever

- Krav

- Krever

- ansvarlig

- Resultater

- Risiko

- halvledere

- Signal

- Silicon

- løsning

- Solutions

- spesialisert

- standarder

- opphold

- Studer

- suksess

- vellykket

- slik

- suite

- støtte

- Bytte om

- system

- Systemer

- Target

- lag

- Teknologi

- enn

- Det

- De

- deres

- Dem

- termisk

- Disse

- de

- denne

- til

- også

- overføringer

- typer

- typisk

- unik

- bruke

- validering

- ulike

- verifisere

- av

- Besøk

- hvilken

- med

- Utbytte

- Din

- zephyrnet