IEDM 2023에서 Naoto Horiguchi는 CFET 및 중간 라인 통합에 대해 발표했습니다. 나는 이 작업에 대해 Naoto와 이야기를 나눌 기회가 있었고 이 글은 IEDM에서의 발표와 후속 토론을 바탕으로 작성되었습니다. 저는 항상 Naoto와 대화하는 것을 좋아합니다. 그는 논리 기술 개발의 리더 중 한 명이며, 기술을 이해하기 쉬운 방식으로 설명하고 반응이 빠르고 작업하기 쉽습니다.

CFET가 필요한 이유

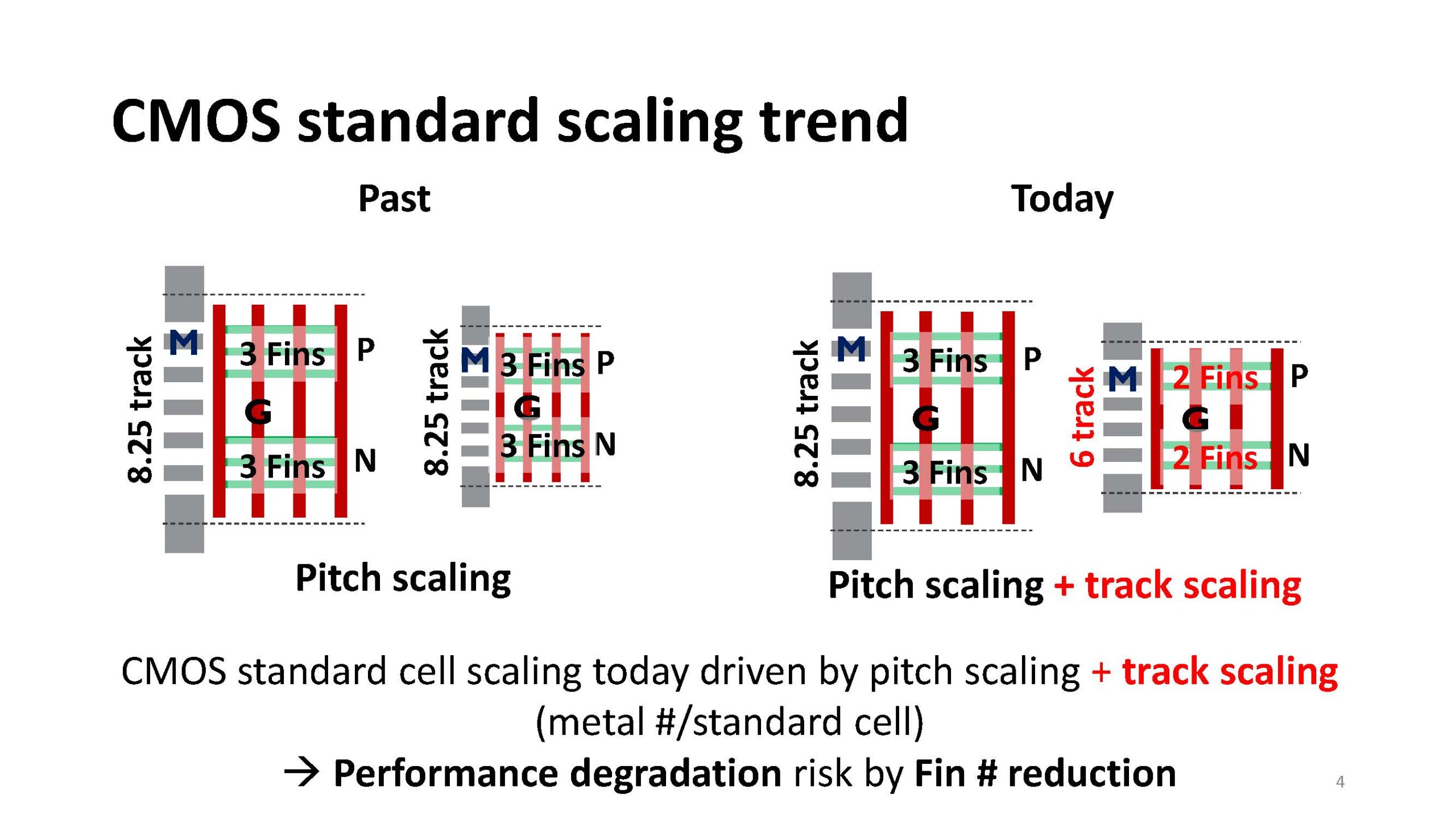

CMOS 스케일링이 순수한 피치 기반 스케일링에서 피치 + 트랙 기반 스케일링으로 전환됨에 따라 핀 제거가 필요해졌습니다(그림 1 참조). 핀 수를 줄일 때마다 성능이 저하됩니다.

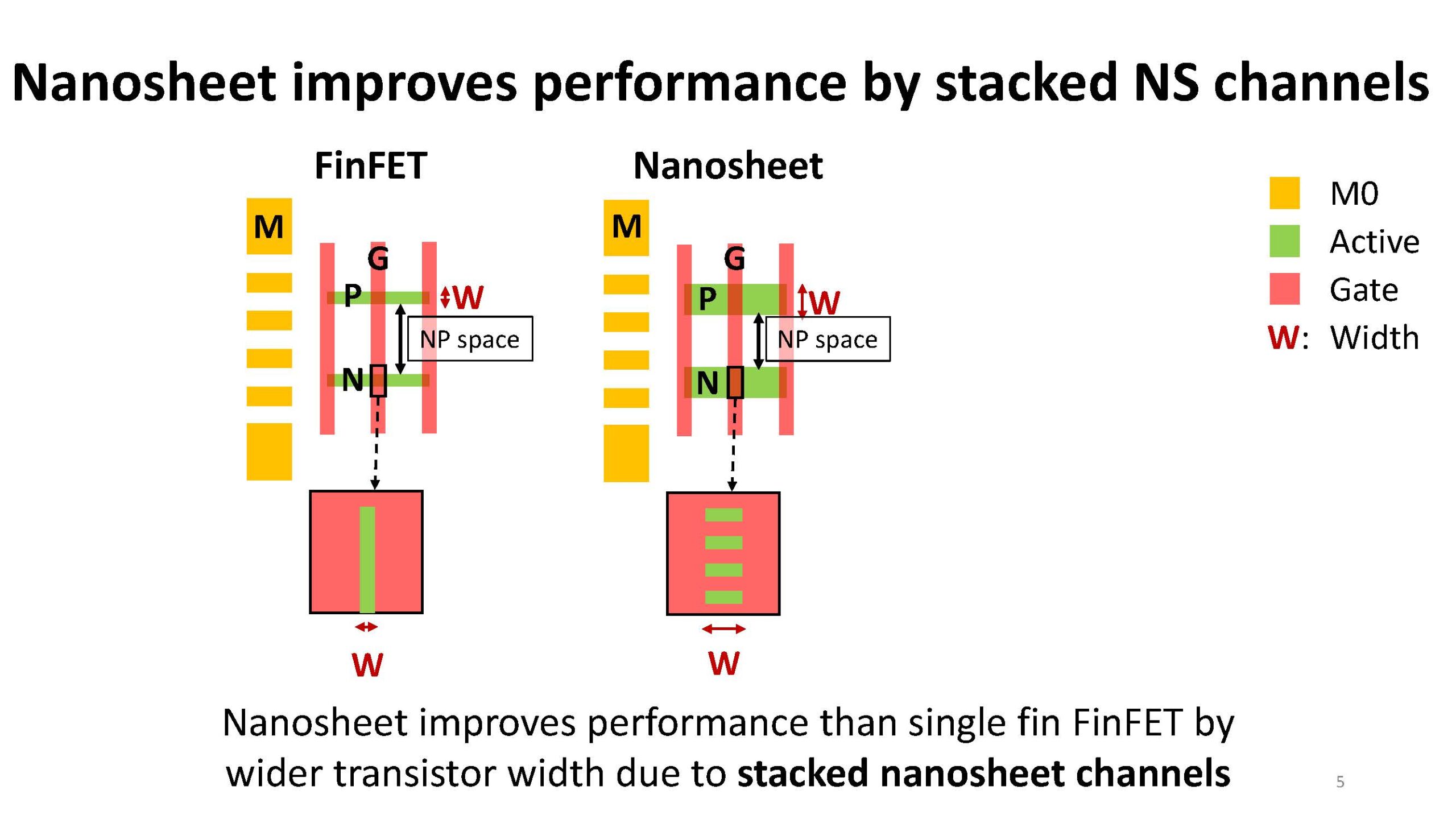

FinFET에서 Stacked H로 이동HNS(Orizontal NanoSheets) 성능은 더 넓은 나노시트 스택과 여러 나노시트를 수직으로 쌓아서 향상/복구될 수 있습니다(그림 2 참조).

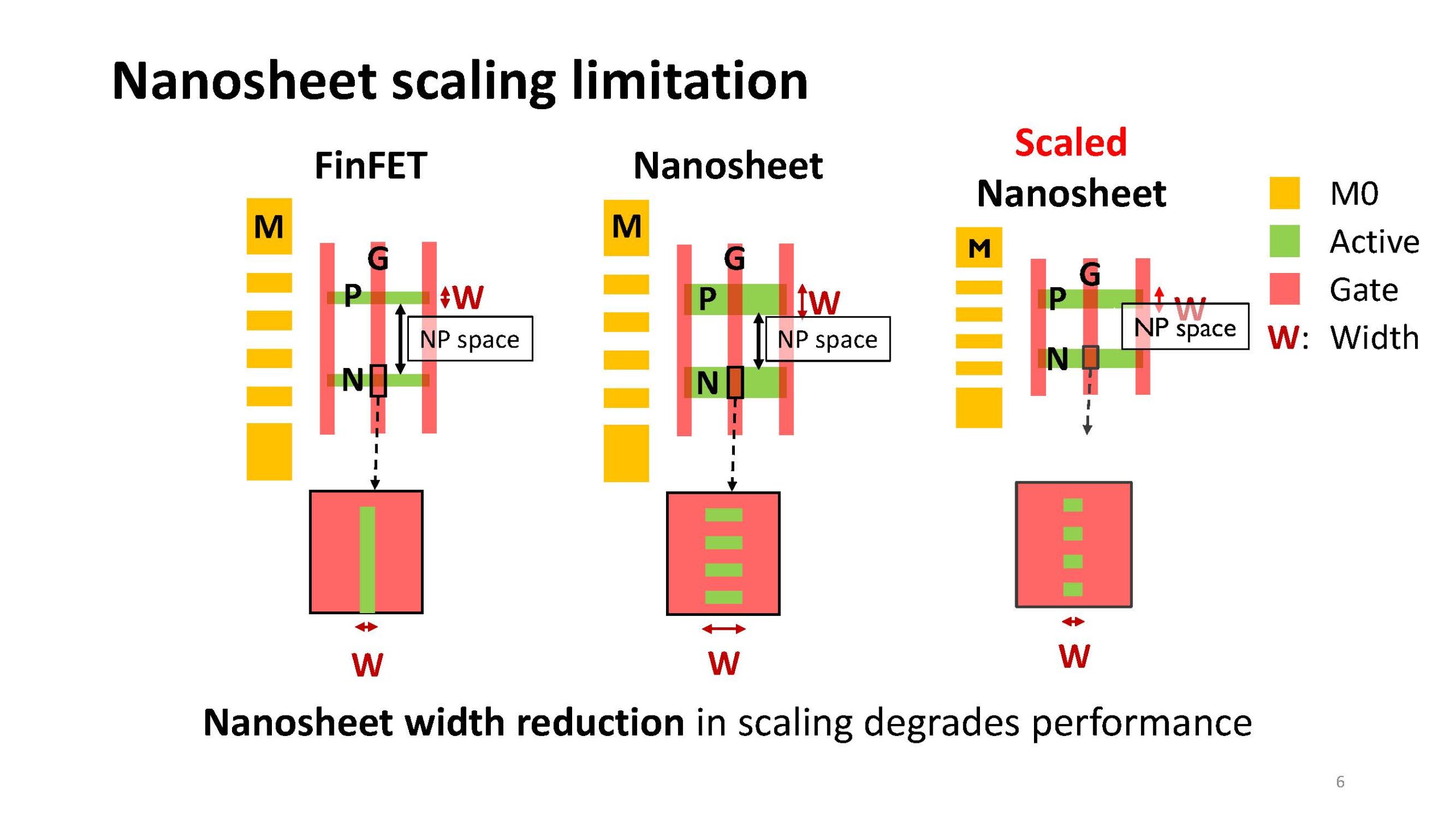

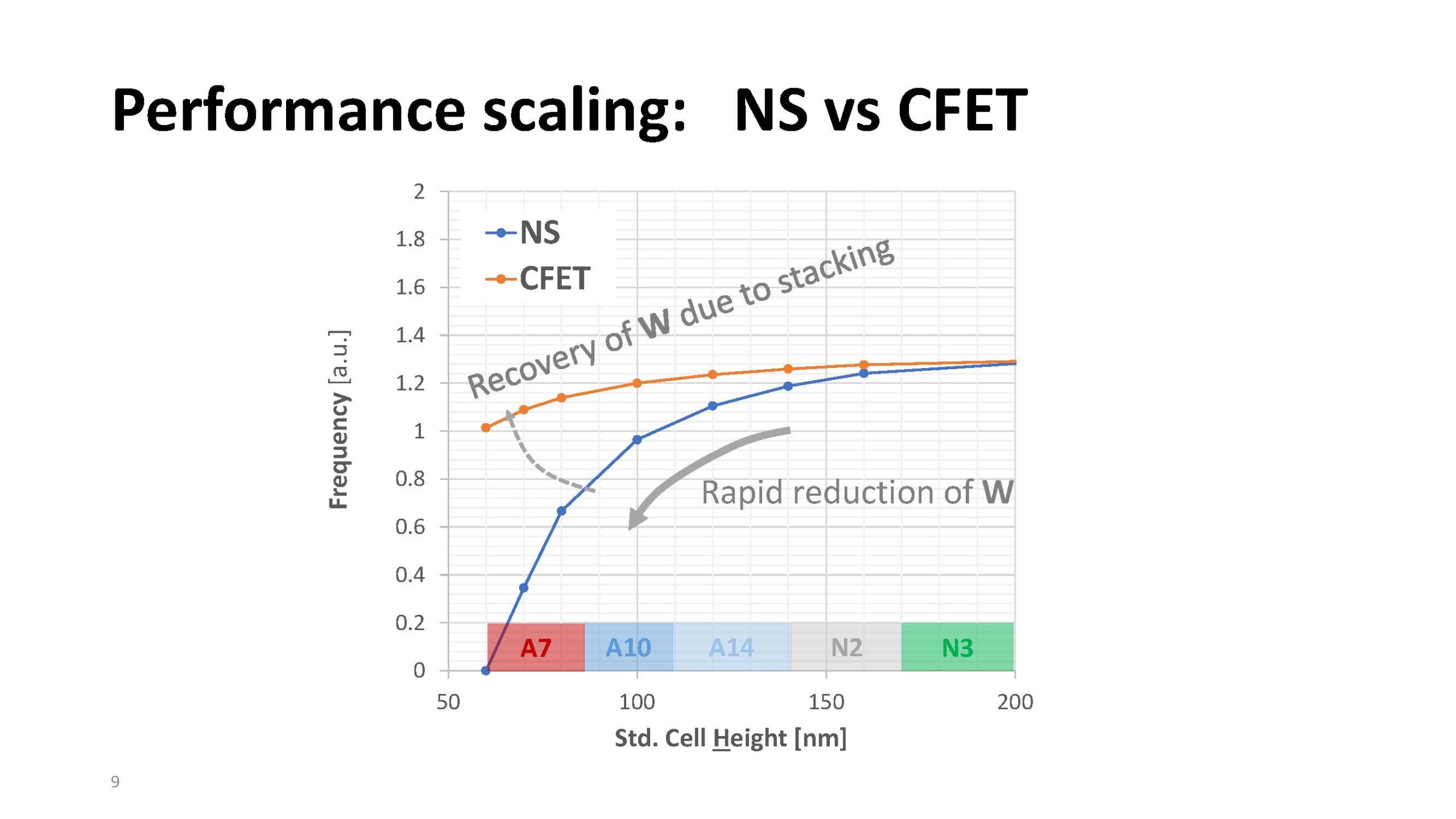

그러나 FinFET의 나노시트 스케일링에서 보았듯이 결국 성능 저하로 이어집니다(그림 3 참조).

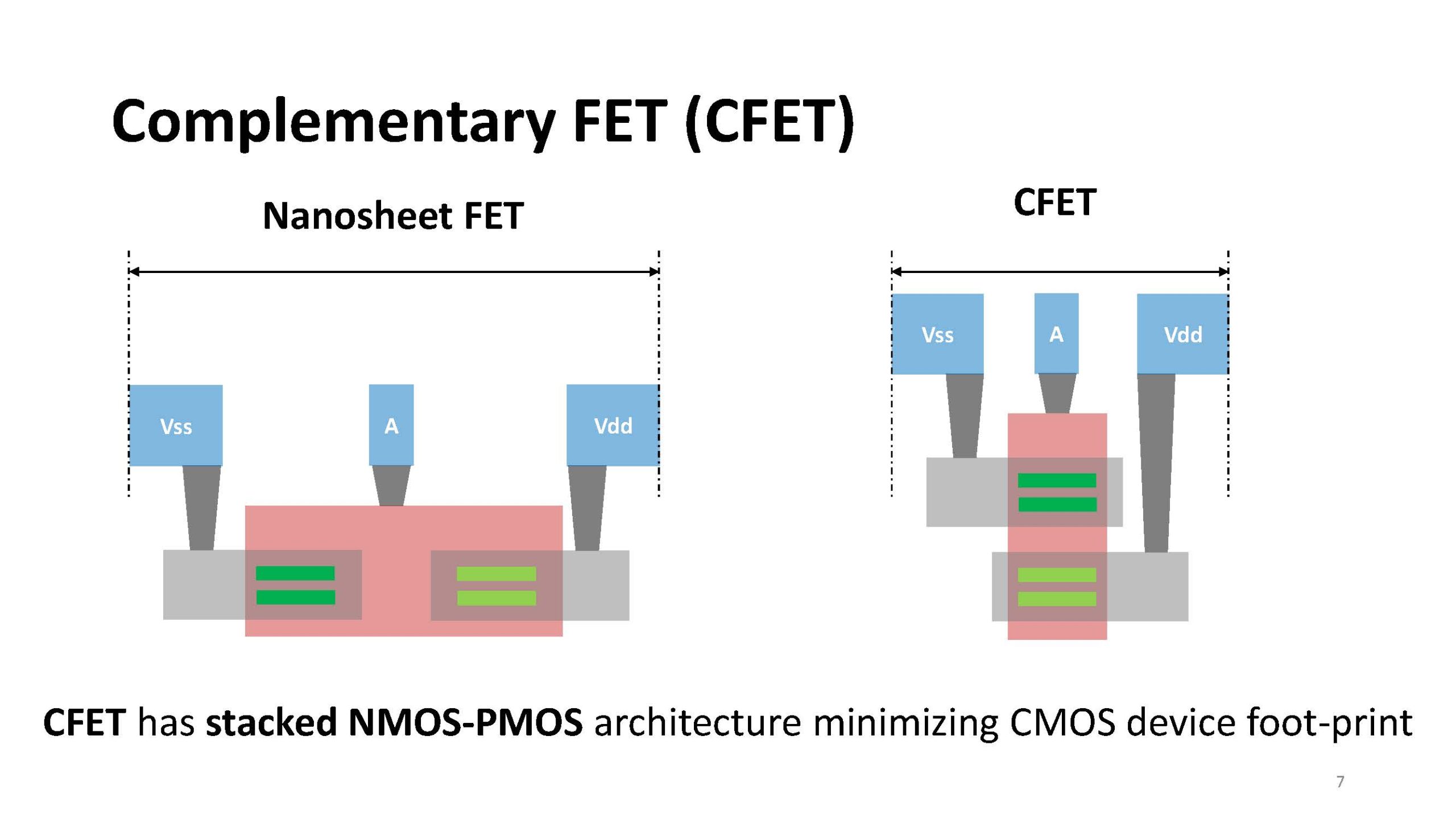

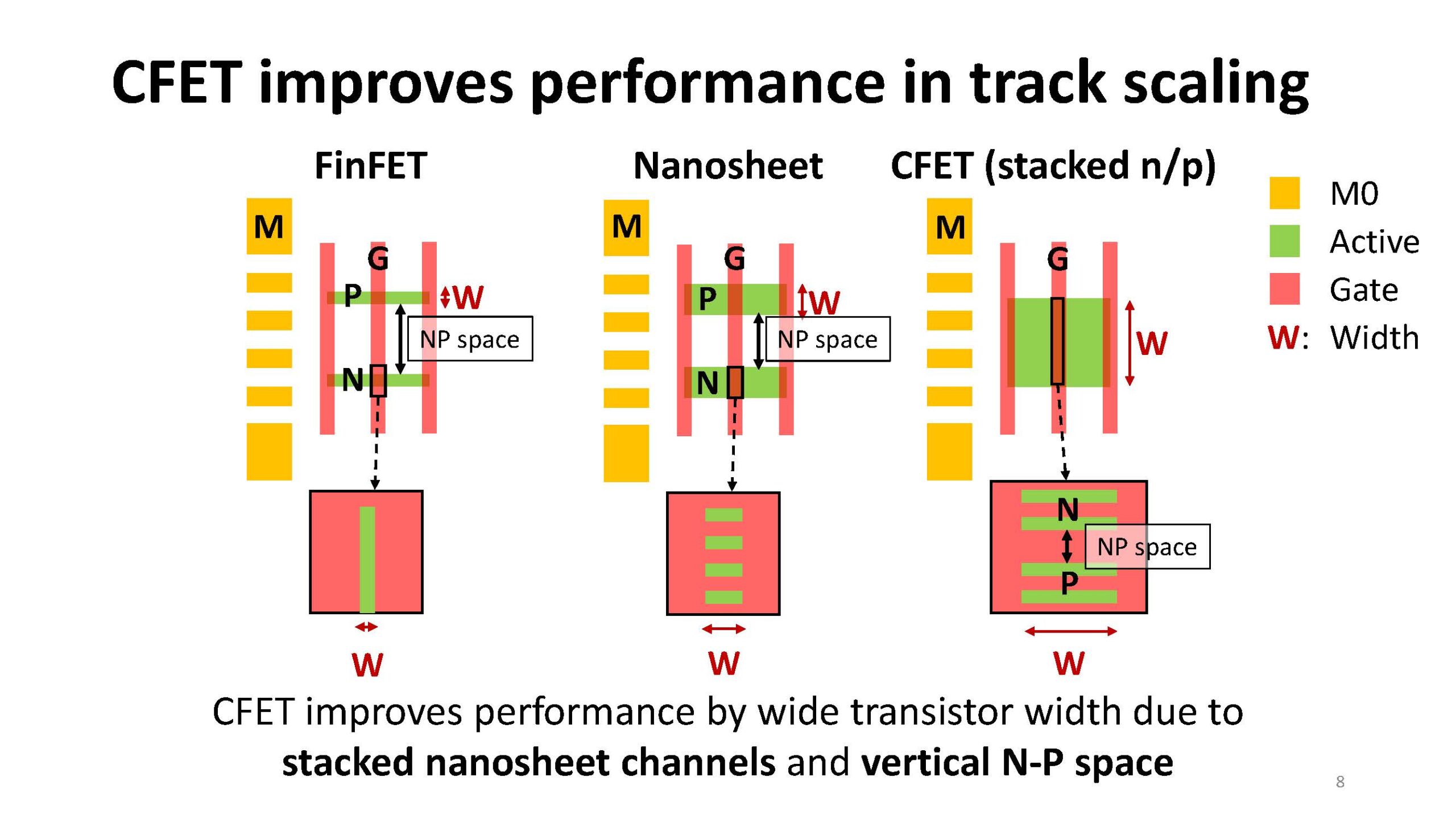

CFET(상보형 FET)는 nFET와 pFET를 적층합니다(그림 4 참조).

CFET는 nFET와 pFET가 적층되고 장치 사이의 np 간격이 수평이 아닌 수직이 되므로 스케일링 제약 조건을 다시 한 번 재설정하여 더 넓은 시트를 가능하게 합니다(그림 5 참조).

그림 6은 HNS 및 CFET 성능과 CFET의 장점을 강조하는 셀 높이의 비교를 보여줍니다.

모놀리식 대 순차 CFET

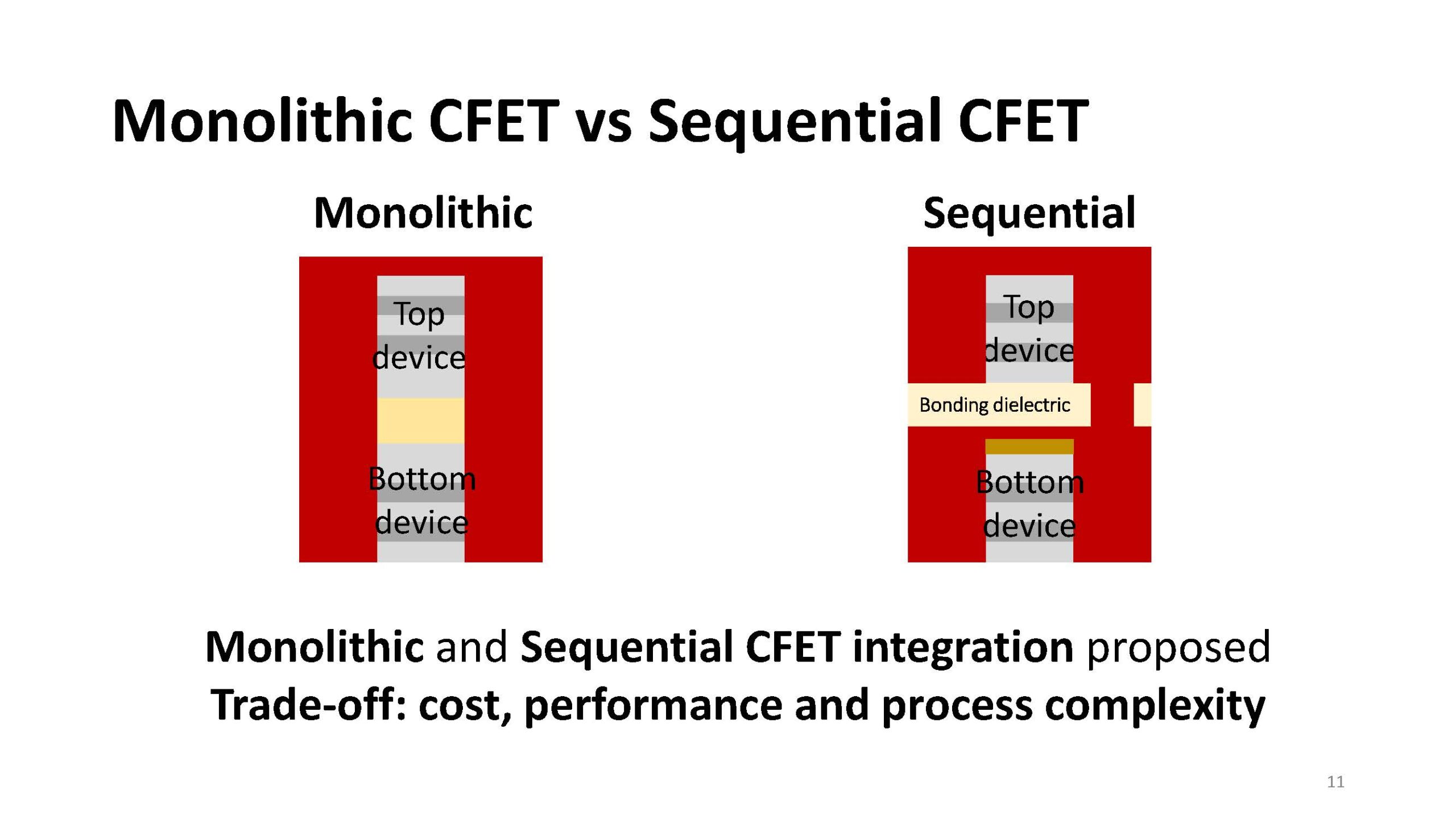

CFET 제조에는 근본적으로 다른 두 가지 접근 방식이 있습니다. 모놀리식 흐름에서 CFET는 연속 공정 흐름으로 웨이퍼에 제조됩니다. 순차적인 흐름에서는 하단 장치가 하나의 웨이퍼에 제조되고, 두 번째 웨이퍼가 첫 번째 웨이퍼에 접합되고, 상단 장치가 두 번째 웨이퍼에 제조됩니다.

순차 흐름에서는 두 장치 사이에 결합 유전체가 존재합니다(그림 7 참조).

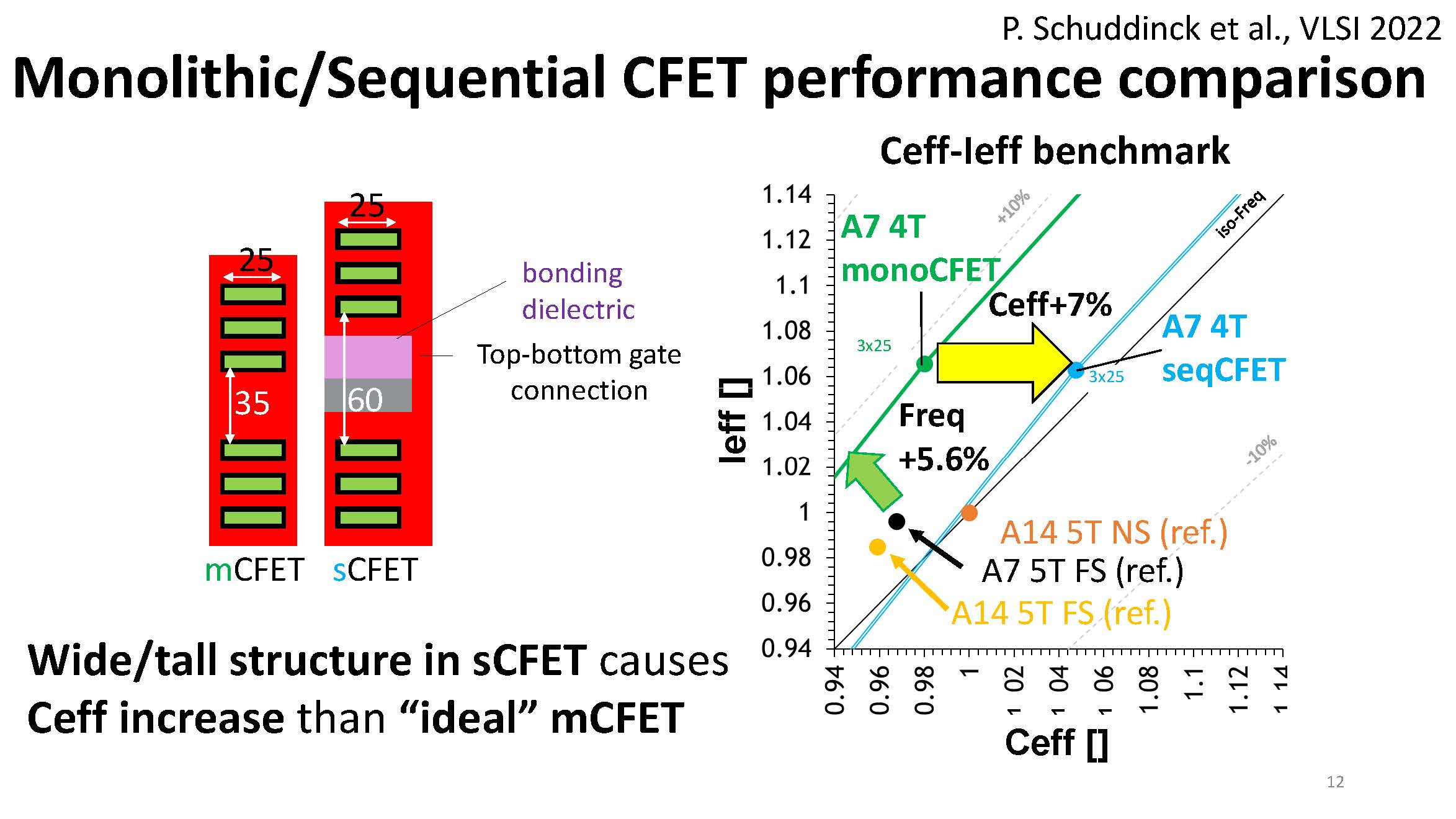

본딩 유전체로 인해 구조가 더 크고 커패시턴스 저하 성능이 더 높습니다(그림 8 참조).

순차 CFET는 모놀리식 CFET보다 제조 비용이 더 많이 들고, 그와 성능 저하 사이에서 업계는 모놀리식 CFET에 초점을 맞추고 있는 것으로 보입니다.

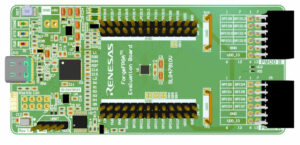

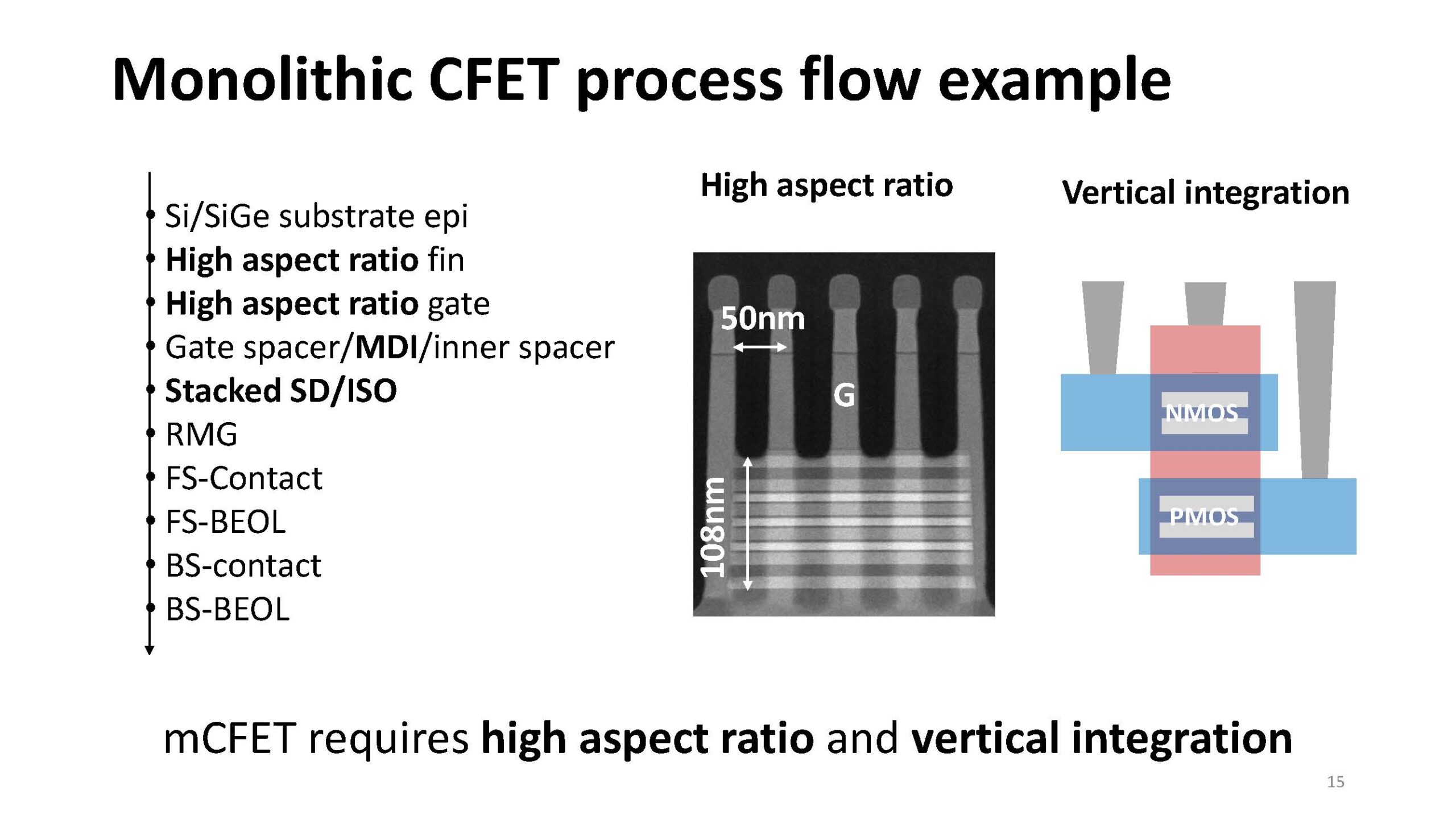

모놀리식 CFET 처리

모놀리식 CFET 프로세스는 그림 9에 나와 있습니다.

굵게 표시된 단계는 특히 어렵습니다.

- 수평형 나노시트 스택(핀)은 이미 종횡비가 높으므로 CFET를 만들기 위해 nFET와 pFET 스택을 서로 위에 쌓아 높이를 두 배 이상 높이는 비교적 두꺼운 층을 만듭니다.

- 게이트 형성은 이전 지점에서 설명한 것처럼 종횡비가 높습니다.

- 에피택셜 소스/드레인은 서로 수직으로 격리되어야 합니다.

- 명시적으로 호출되지는 않지만 하단 장치 소스/드레인을 제작한 다음 상단 장치 상단 소스/드레인을 제작합니다. 상단 장치의 열 처리 및 후속 단계는 하단 장치의 품질이 저하되지 않을 만큼 충분히 낮은 온도에서 수행되어야 합니다.

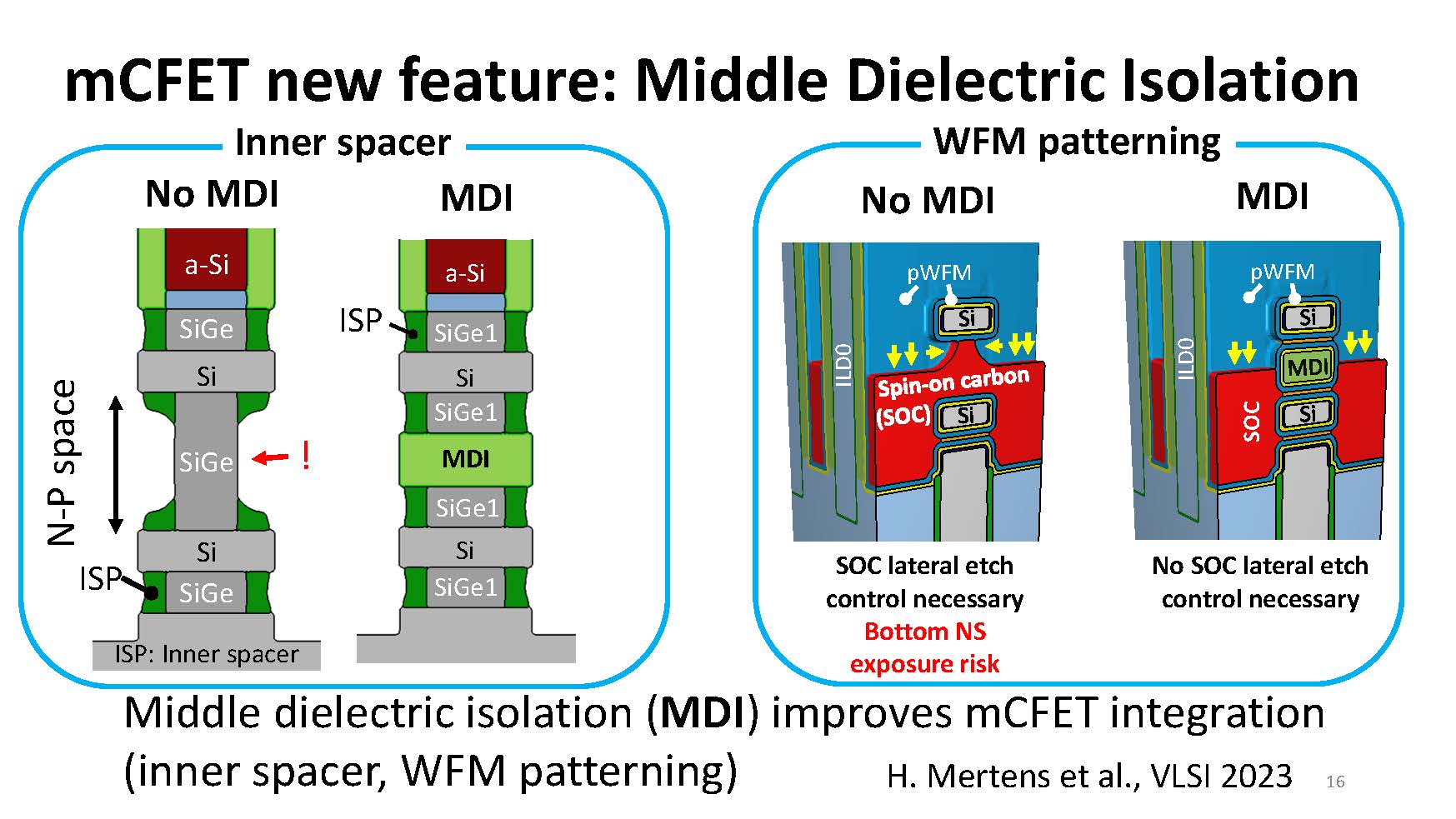

이 프레젠테이션에서 특히 흥미로운 부분 중 하나는 MDI(Middle Dielectric Isolation) 부분이었습니다. 이전에는 이 문제를 본 적이 없었습니다. MDI는 내부 스페이서 및 WFM(Work Function Material) 패터닝을 입증합니다.

그림 10은 내부 스페이서 형성(왼쪽) 및 WFM 패터닝(오른쪽)에 대한 MDI 효과를 보여줍니다.

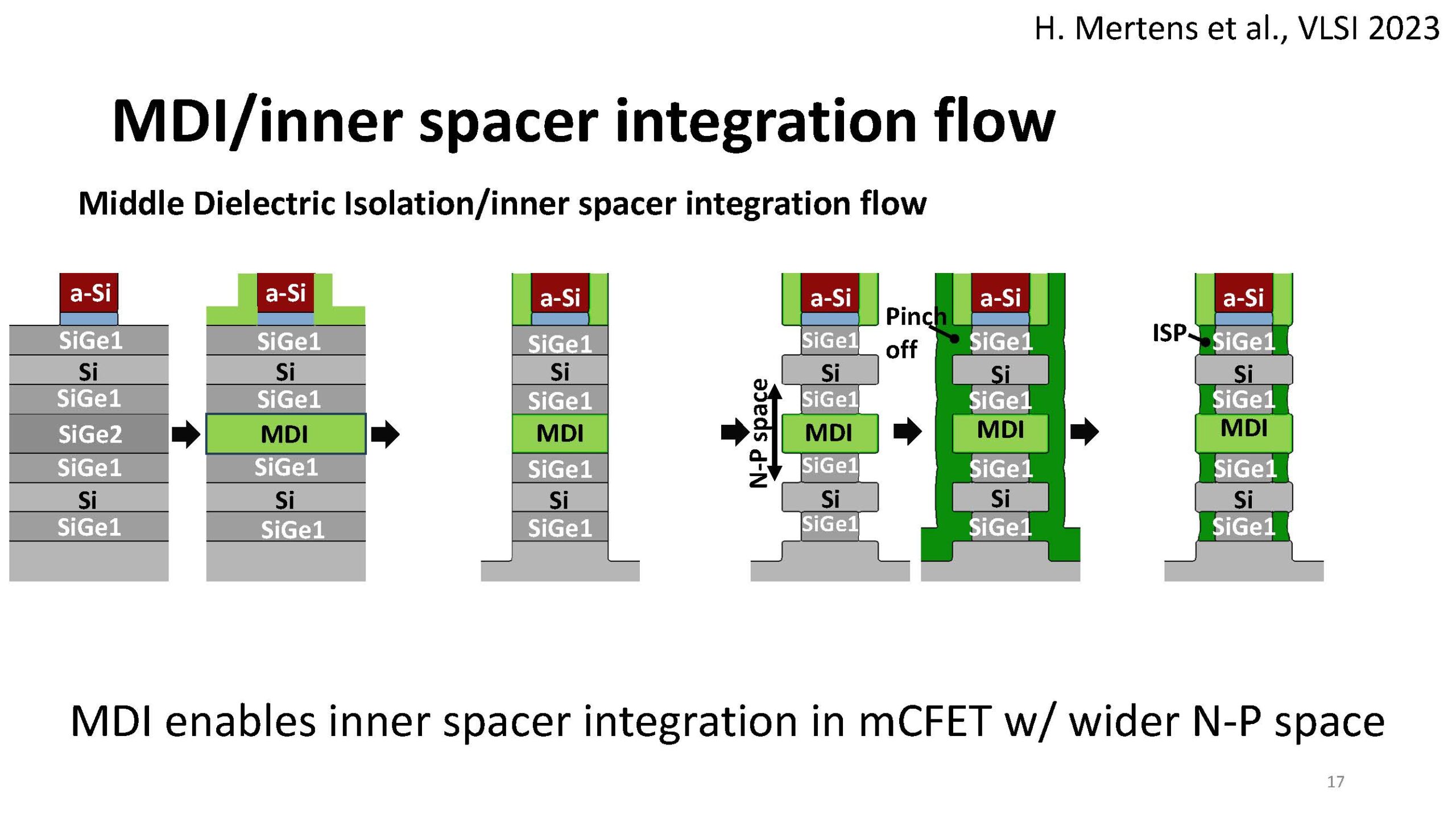

그림 11은 MDI 통합 흐름을 보여줍니다.

MDI를 통합함으로써 내부 스페이서 형성에 영향을 주지 않고 nFET와 pFET 사이의 수직 간격을 늘릴 수 있습니다.

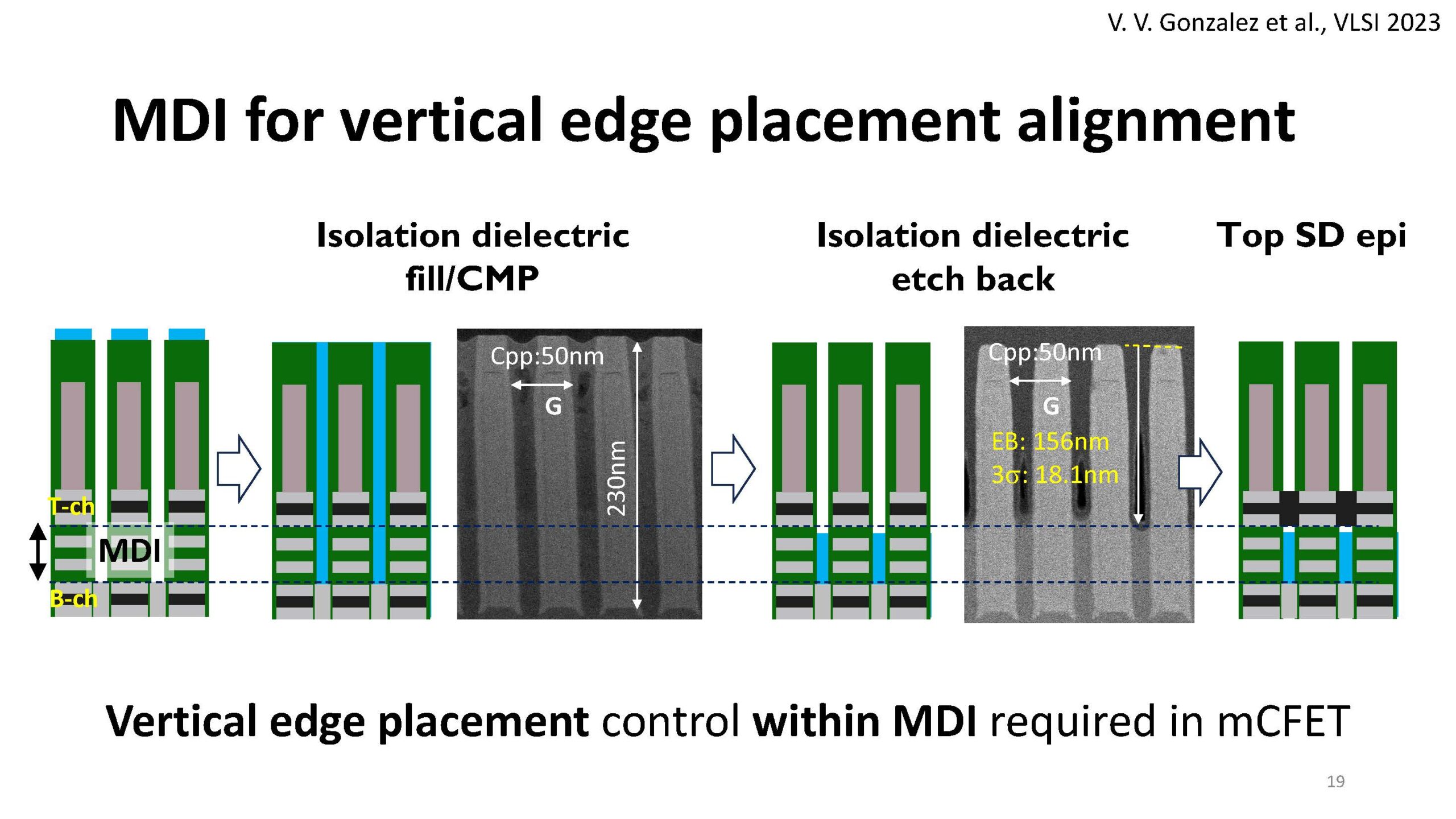

앞서 언급한 것처럼 하단 장치 소스/드레인이 제작된 다음 상단 장치 소스/드레인이 제작됩니다. 하단 소스/드레인을 형성한 후, 절연 유전체를 증착하고 에칭하여 소스/드레인 에피택셜 형성을 위한 상단 장치를 노출시킵니다. 절연 에칭백은 MDI 높이로 제어되어야 합니다(그림 12 참조).

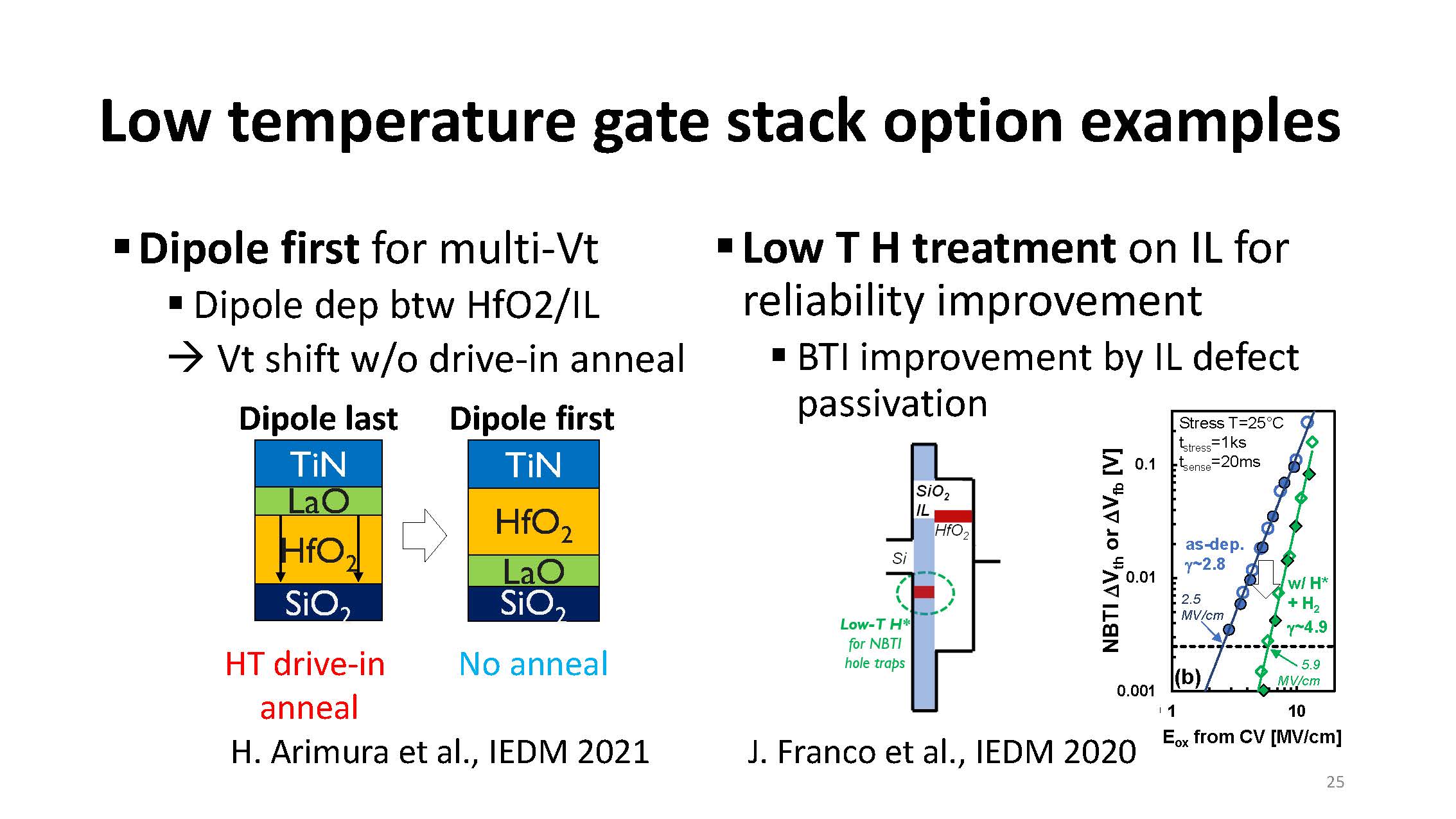

장치 성능의 열적 저하를 최소화하려면 쌍극자 우선 처리를 사용하고 어닐링 및 저온 층간 형성 공정이 필요하지 않은 새로운 WFM 옵션이 필요합니다(그림 13 참조).

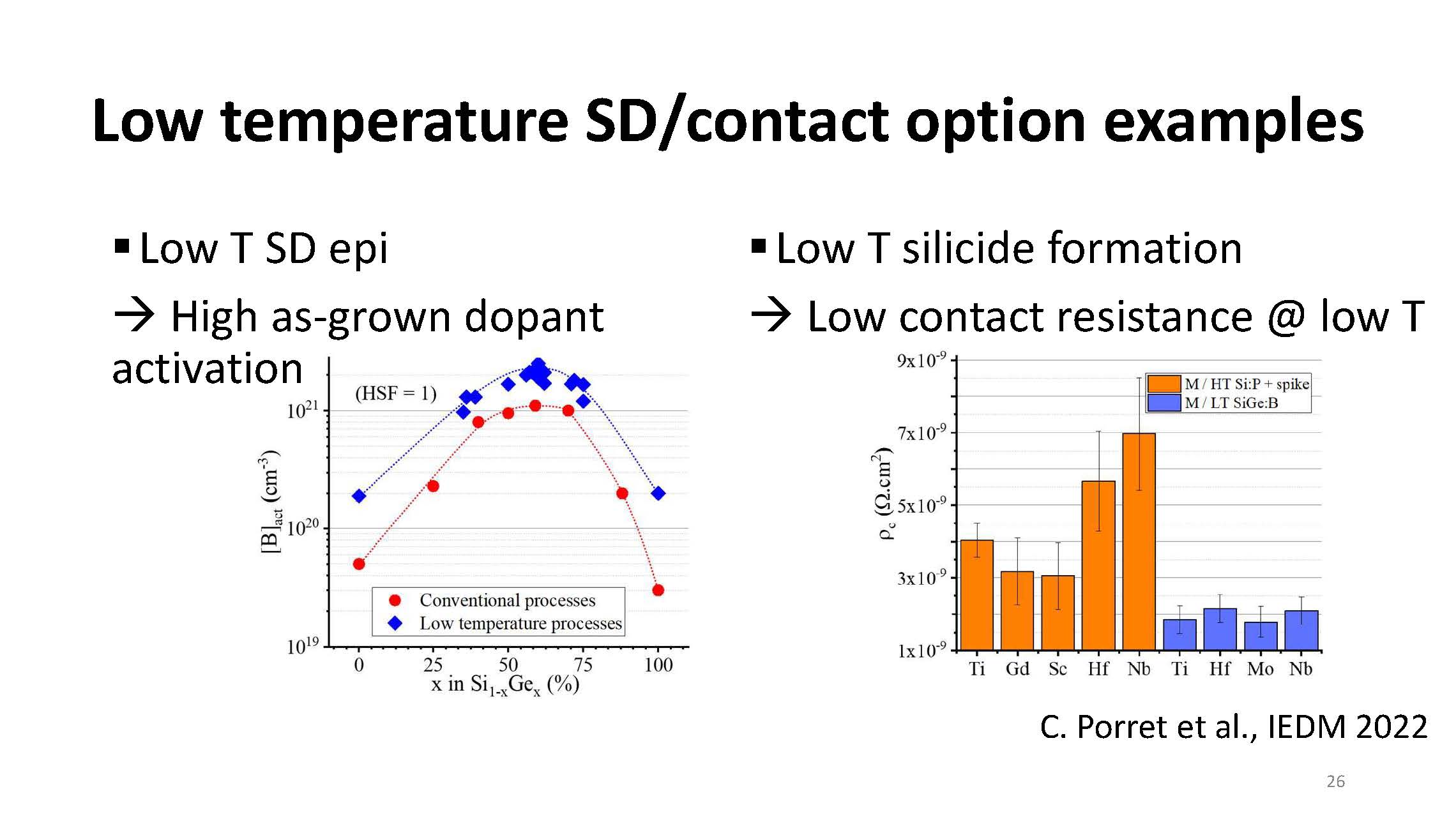

접점 형성을 위한 저온 소스/드레인 성장과 저온 실리사이드도 필요합니다(그림 14 참조).

저온 규화물은 하단 장치에 대한 후면 직접 접촉에 특히 중요합니다. CFET 인터커넥트는 하단 및 상단 장치에 대한 접촉이 필요하며 후면 전력 공급의 출현으로 상단 장치는 전면 상호 연결 스택에서 접촉되고 하단 장치는 후면에서 접촉됩니다. 몰리브덴(Mo)과 니오븀(Nb)은 pFET에 유망하고 스칸듐(Sc)은 nFET에 유망하지만 Sc는 ALD로 증착하기 어렵습니다.

라인 상호 연결의 뒷면과 중간

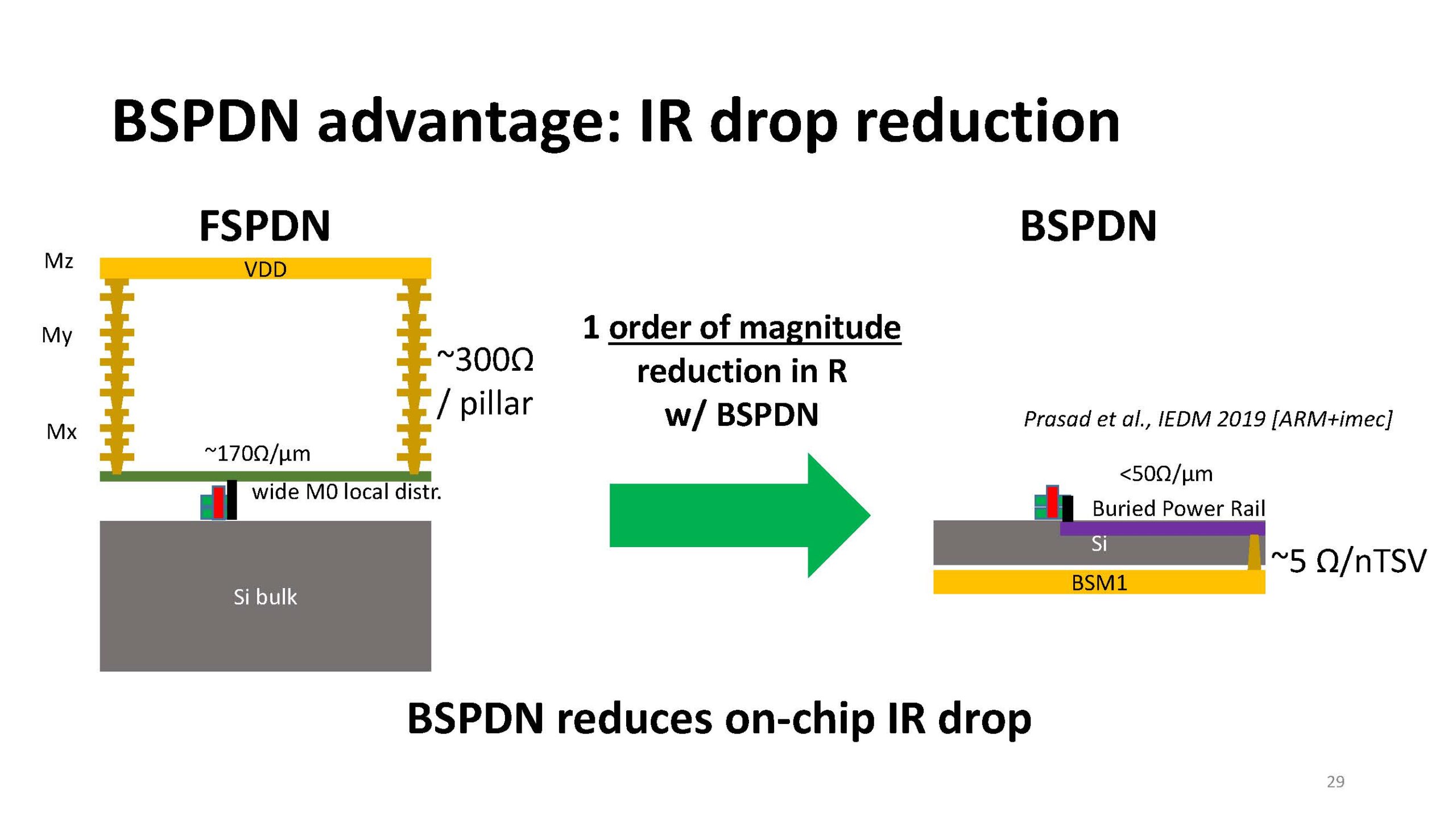

제가 이전에 쓴 것처럼 여기에서 지금 확인해 보세요. BSPDN(Back Side Power Delivery Network)은 올해 Intel, Samsung 및 TSMC가 2026년에 도입할 예정입니다. 상호 연결을 전면 신호 연결과 후면 전원 연결로 분할하면 IR 강하(전력 손실)가 몇 배나 줄어듭니다. 그림 참조 15.

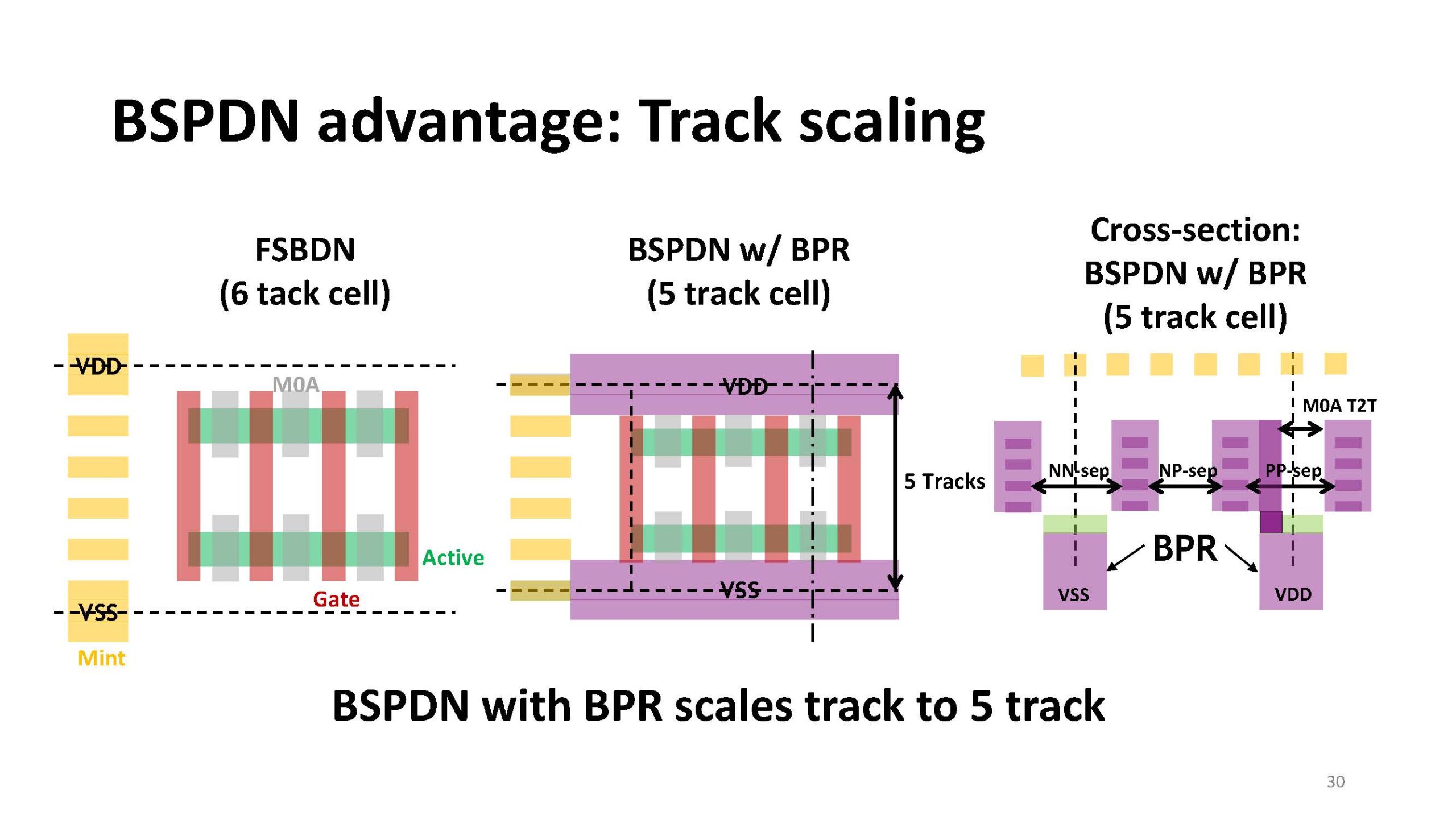

BSPDN은 또한 6트랙에서 5트랙 셀로의 축소를 지원하는 트랙 스케일링을 개선합니다(그림 16 참조).

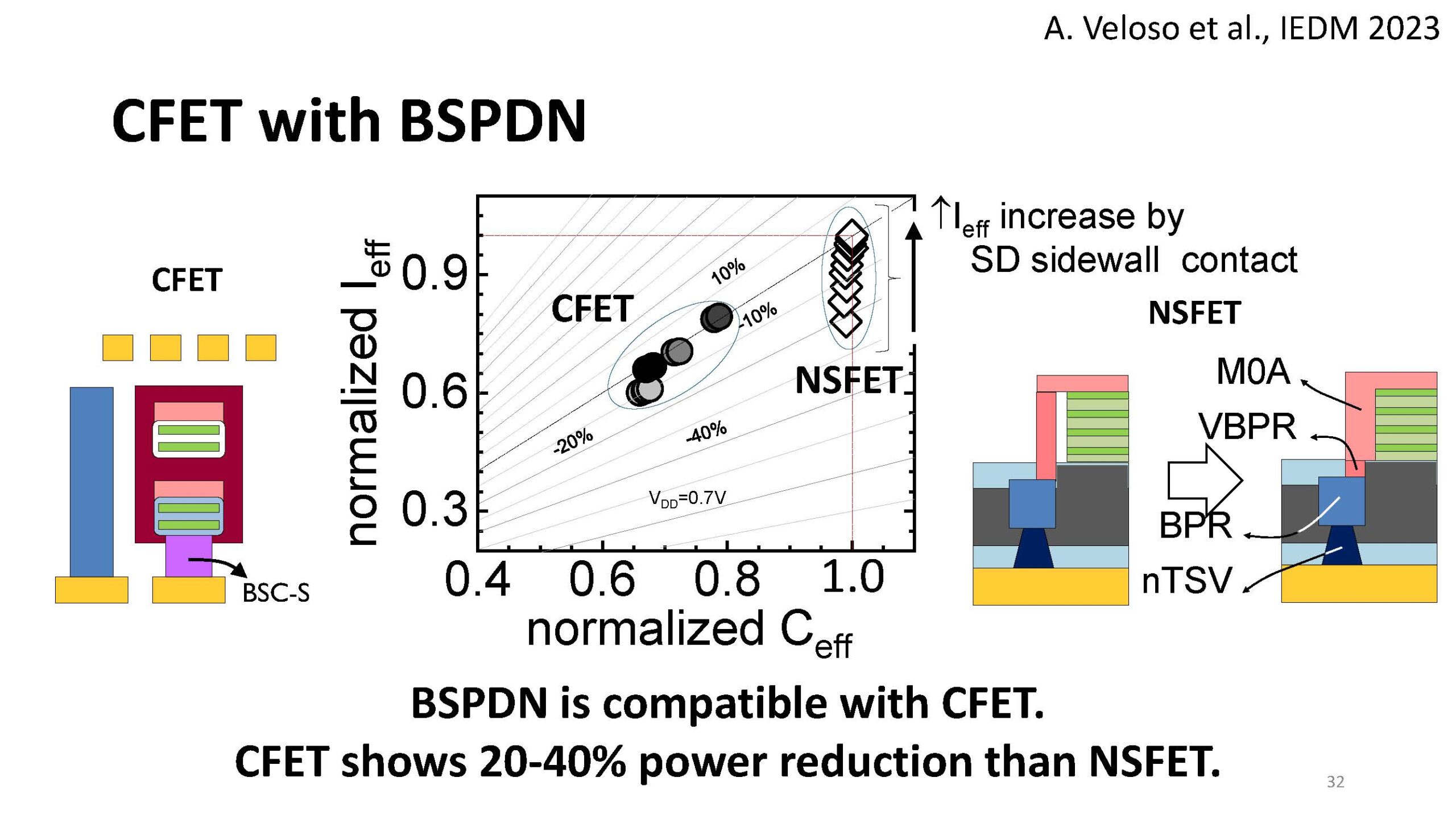

BSPDN과 CFET의 통합은 HNS(Horizontal Stacked NanoSheet)에 비해 전력을 20~40% 절감할 수 있습니다(그림 17 참조).

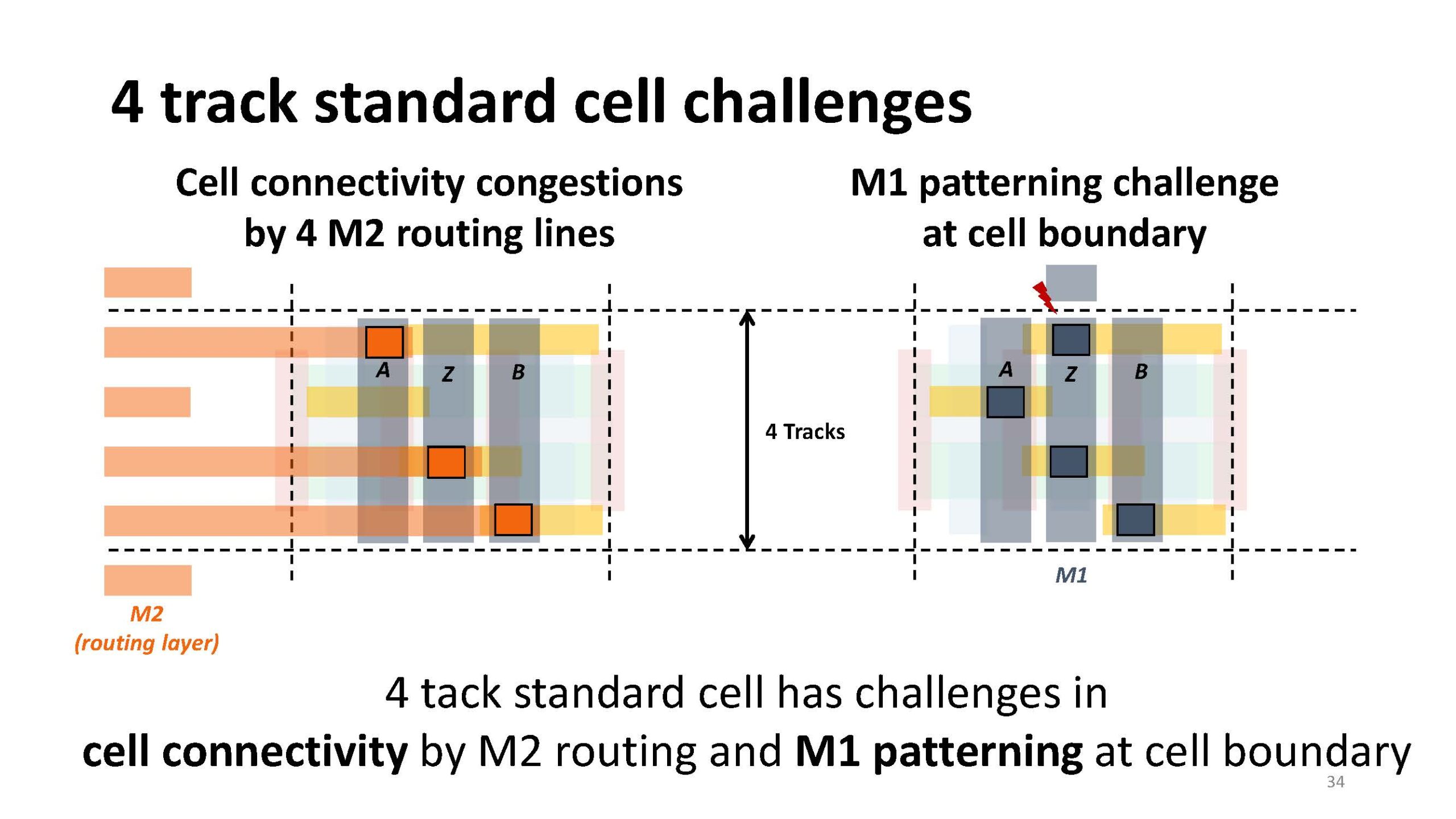

5트랙 셀을 넘어 4트랙 셀 상호 연결 문제를 극복해야 합니다(그림 18 참조).

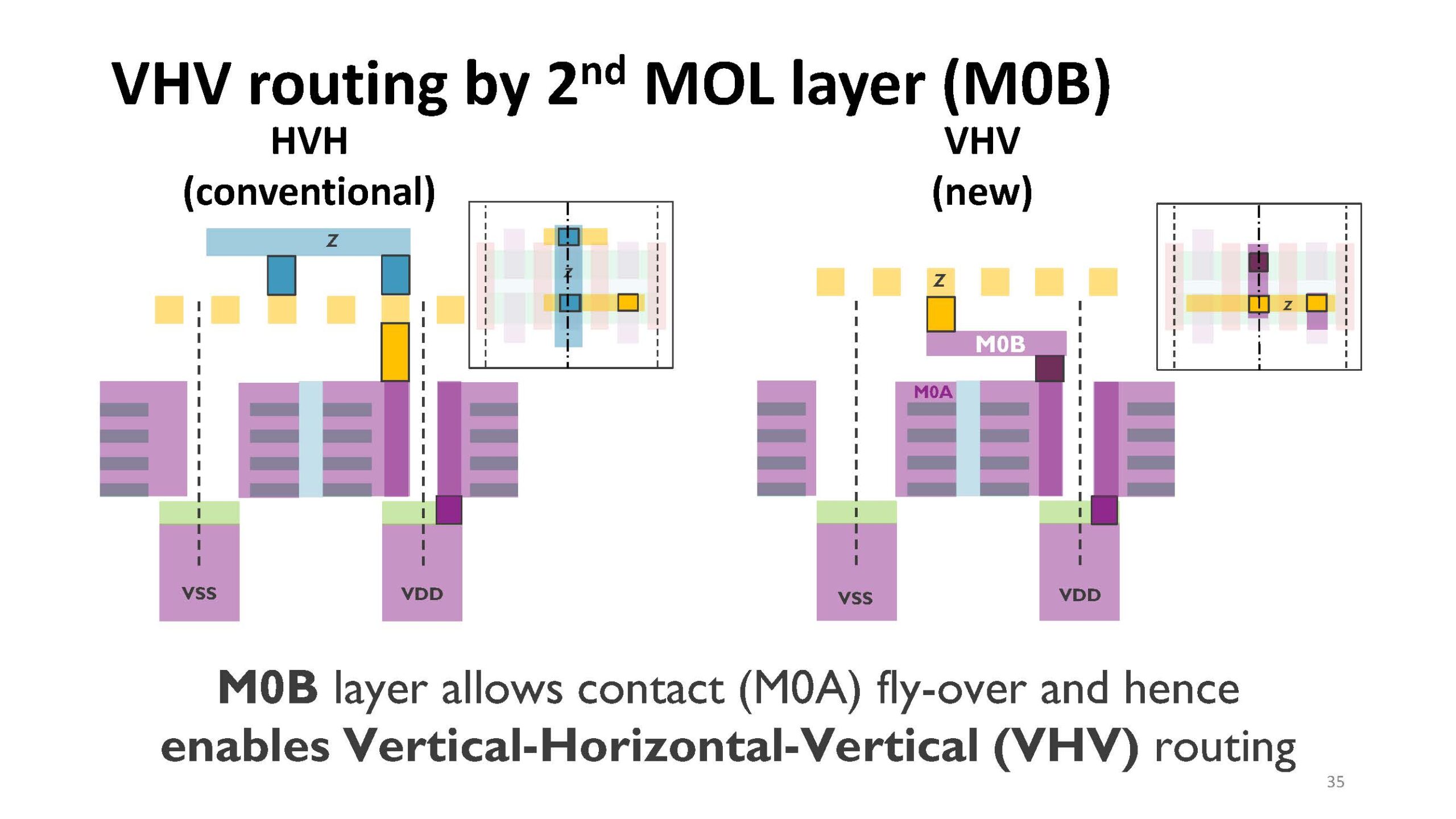

추가 MOL(Middle of Line) 레이어가 있는 수직-수평-수직 레이아웃은 4트랙 셀을 활성화할 수 있습니다(그림 19 참조).

나는 이전에 이 분야에서 Imec의 작업에 대해 글을 쓴 적이 있습니다. 여기에서 지금 확인해 보세요. 그래서 나는 그 정보를 반복하지 않을 것입니다.

나는 Naoto에게 4트랙 셀을 넘어 3트랙 셀로 이동하려면 무엇이 필요한지 물었습니다. 그는 Imec이 현재 최적화 작업을 진행하고 있으며 추가 MOL 레이어가 필요할 수 있으며 옆에 위에서 아래로 연결해야 할 수도 있다고 대답했습니다. 표준 셀 레이아웃에 영향을 미치는 장치.

나는 또한 Naoto에게 언제 CFET가 구현되는 것을 볼 수 있을지 물었고 그는 A10 로직 세대나 A7 세대가 가능할 것이라고 말했습니다.

저자는 Intel, Samsung 및 TSMC가 모두 올해 IEDM에서 CFET에 대한 작업을 발표했으며 Intel과 TSMC 모두 FinFET가 HNS와 CFET로 바뀌는 것을 보여주는 기술 옵션 맵을 가지고 있다고 언급했습니다.

결론

Imec은 HNS 이후 차세대 옵션으로 CFET 개발에 있어 계속해서 뛰어난 진전을 보이고 있습니다. 이 작업에서는 장치 통합 옵션과 BSPDN 및 MOL 옵션이 모두 설명되었습니다.

또한 읽기 :

IEDM 2023 – 300mm 웨이퍼 Fab 탄소 배출 모델링

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/semiconductor-services/340811-iedm-2023-imec-cfet/

- :있다

- :이다

- :아니

- $UP

- 06

- 07

- 08

- 09

- 1

- 10

- 11

- 12

- 13

- 14

- 15%

- 16

- 17

- 19

- 2023

- 2026

- 25

- 26

- 29

- 30

- 32

- 35%

- 7

- 8

- 9

- a

- 소개

- 또한

- 추가

- 이점

- 출현

- 후

- 다시

- All

- 이미

- 또한

- 이기는하지만

- 항상

- an

- 및

- 등장하다

- 구혼

- 있군요

- 지역

- AS

- 양상

- At

- 뒤로

- 기반으로

- BE

- 때문에

- 가

- 된다

- 된

- 전에

- 사이에

- 그 너머

- 일시: XNUMX년 XNUMX월 XNUMX일 화요일 XNUMX:XNUMXpm - XNUMX:XNUMXpm 장소: 여의도 페어몬트 앰배서더 서울 호텔 XNUMXF 아잘레아스 룸 [약도] 행사 문의: info.korea@rescale.com

- 두

- 바닥

- by

- 전화

- 라는

- CAN

- 탄소

- 세포

- 셀

- 과제

- 도전

- 기회

- 비교

- 보완적인

- 연결

- 연결

- 제약

- CONTACT

- 콘택트 렌즈

- 계속

- 끊임없는

- 통제

- 배달

- 예금

- 기탁 된

- 기술 된

- 개발

- 장치

- 디바이스

- 다른

- 곧장

- 토론

- do

- 한

- 급회전

- 드롭

- 마다

- 쉽게

- Edge

- 효과

- 가능

- 수

- 즐겨

- 충분히

- 있을뿐만 아니라

- 우수한

- 기대하는

- 비싼

- 설명

- 명시 적으로

- FET

- 그림

- 지느러미

- 최후의

- FINE

- 먼저,

- 흐름

- 집중

- 따라

- 럭셔리

- 형성

- 에

- 앞

- 기능

- 근본적으로

- 문

- 세대

- 기부

- Go

- 성장

- 했다

- 하드

- 있다

- he

- 신장

- 높은

- 더 높은

- 강조

- 그의

- 수평

- HTTPS

- 화웨이

- i

- 설명하다

- 영향

- 영향을주는

- 구현

- 중대한

- 개선하는

- 향상

- in

- 증가

- 산업

- 정보

- 안의

- 를 받아야 하는 미국 여행자

- 통합

- 완성

- 인텔

- 흥미있는

- 으로

- 소개

- 외딴

- 격리

- 발행물

- IT

- JPG

- 층

- 레이어

- 레이아웃

- 지도자

- 오퍼

- 왼쪽 (left)

- 라인

- 논리

- 오프

- 낮은

- 확인

- 지도

- 항해사

- 자료

- 최대 폭

- XNUMX월..

- 말하는

- 중간

- 수도

- 최소화

- 모델링

- 몰

- 단단히 짜여 하나로 되어 있는

- 배우기

- 움직이는

- 여러

- 절대로 필요한 것

- 필요한

- 필요

- 필요

- 네트워크

- 신제품

- 다음 것

- 아니

- 주의

- 지금

- 번호

- of

- on

- 일단

- ONE

- 최적화

- 선택권

- 옵션

- or

- 주문

- 기타

- 우리의

- 아웃

- 극복하다

- 페이지

- 부품

- 특별히

- 성능

- 피치

- 게재

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- ...을 더한

- 포인트 적립

- 혹시

- 게시하다

- 힘

- 제시

- 프레젠테이션

- 제시

- 선물

- 너무 이른

- 이전에

- 찬성

- 방법

- 프로세스

- 처리

- 진행

- 장래가 촉망되는

- 증명하다

- 제공

- 출판

- 전혀

- 비율

- 읽기

- 감소

- 감소

- 감소

- 축소

- 상대적으로

- 반복

- 필요

- 필요

- 반응

- 연락해주세요

- 라우팅

- 말했다

- 삼성

- SC

- 스케일링

- 둘째

- 참조

- 본

- 표시

- 보여주는

- 측면

- 신호

- So

- 말하다

- 스택

- 쌓인

- 스태킹

- 스택

- 표준

- 단계

- 구조

- 후속의

- 지원

- 받아

- 말하는

- Technology

- 기술 개발

- 보다

- 그

- XNUMXD덴탈의

- 그때

- 열의

- 이

- 올해

- 생각

- 시간

- 에

- 상단

- 선로

- 전환 된

- 티엠씨

- 두

- 업데이트

- 대

- 수직선

- 수직으로

- 를 통해

- vs

- 였다

- 방법..

- we

- 잘

- West

- 뭐

- 언제

- 넓은

- 의지

- 과

- 없이

- 작업

- 일하는

- 겠지

- 쓰다

- 쓴

- year

- 당신

- 제퍼 넷