最近の RISC-V サミットの最後のセッションは、チップレットに関するパネルディスカッションでした。 RISC-V エコシステムのチップレット。 RISC-V International の CEO である Calista Redmond が司会を務めました。パネリストは次のとおりです。

- Arteris 社 COO、Laurent Moll 氏

- Aniket Saha 氏、Tenstorrent 製品管理担当副社長

- Dale Greenley 氏、Ventana Microsystems エンジニアリング担当副社長

- ロブ・エイトケン氏、シノプシスの著名アーキテクト

これは私にとって少し奇妙なトピックの組み合わせです。もちろん、RISC-V プロセッサをチップレット上に搭載することもできますが、課題は他のプロセッサと実際には変わりません。しかし、RISC-V は注目されており、チップレットも注目されており、Ventana のような企業はそれらを組み合わせています。

文脈を理解するために、企業についての背景を少し説明しましょう。

- ご存知かと思いますが、Arteris はネットワーク オン チップ (NoC) を製造しています。同社は、チップレット ベンダー (および IP ベンダー) の中では中立的な企業です。

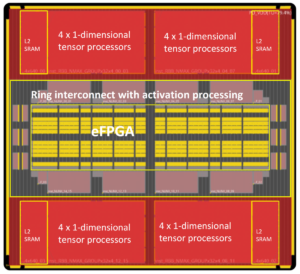

- Tenstorrent は、非常に高性能なマルチコア RISC-V チップのポートフォリオを設計しています

- Ventana は RISC-V IP を備えていますが、それをチップレットとしても提供します

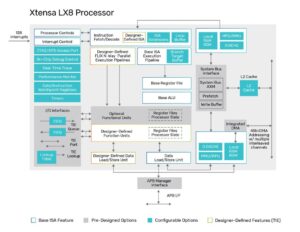

- Synopsys は明らかに EDA 企業ですが、サミットの早い段階で RISC-V コアを発表しました

]

実際の議論

カリスタからの最初の質問は、チップレットの価値は何かというソフトボールでした。

デール氏は、チップレット向けのRISC-Vについて具体的なことは何もないが、大きなモノリシックなものやチップレットをいつ作るかは市場が決めると述べた。それは顧客が何をしてくれるかによって決まります。 「当社は IP とチップレットの両方を提供しており、両方を提供する余地があります。」

Aniket 氏は、「チップレットの開発は安くはありませんが、チップレットと RISC-V の実行は柔軟性があり、迅速に製品を思いつくことができます。」と述べました。

ローランは製作費を求めた。 100 億個の部品を構築している人は多くないため、NRE を管理しておくことが非常に重要です。そのため、より多くのベンダーが関与し、サプライチェーンが複雑になります。 SoC は複雑ですが、チップレットはさらに複雑です。

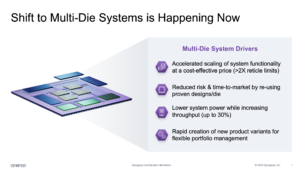

ロブ氏は、RF とアナログ用のチップレットの追加、オプションのアクセラレータの搭載などの異質性を指摘しました。これにより、新たな市場が開拓される可能性があります。

カリスタは続けて、自動車業界における私たちの立ち位置について尋ねました。

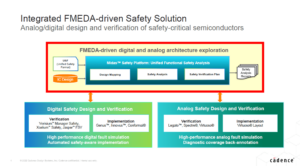

アニケット氏は、自動車業界は非常に保守的だが、現在はローエンド車からハイエンド車まで拡張できるプラットフォームに積極的であると指摘した。チップレットに関しては、機能安全性を実際に考慮した人は誰もいませんでした。

ロブは航空宇宙(自動車産業ではありません)に行き、通常、数十年前に定義された固定の物理体積がどのように存在するのかについて話し合いました。物を入れるのは難しいです。

ローラン: 自動車会社は究極のカタログ購入者であり、チップレットにより AI、レーダー、インフォテインメントなどの最高のものを活用できるようになります。

ソフトウェアを実行するにはどうすればよいですか?

ロブ: システムを小さくすれば大丈夫です。しかし、自動車カタログの購入はさらに困難になります。

アニケット: 「追加しても使用しません」という発言に関連しました。車載ソフトウェア スタックは 5 年以内に RISC-V をサポートする予定です。これは早いです。 Armがそこに到達するまでに15年かかりました。

Q: 接続には何が必要ですか?

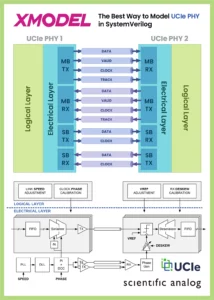

ローラン: 特に人々がチップレットを求めて買い物をしている状況では、非常に複雑です。異なるベンダーの PHY は相互運用可能である場合があります。誰もが UCIe に熱心です。人々はチップレットをより適切に適合させる標準を求めています。

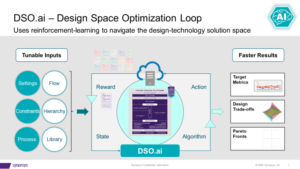

Aniket は、チップレットの標準設計フローが存在しないと不満を述べました。基準が大きく欠如している。

ロブは、標準的なフローを考え出すことはできるが、さまざまなチップレットを使用するため、さまざまな設計フローは必要ないと考えています。

Q: 3 ~ 5 年後にはどうなると思いますか?

ロブ:私たちはこれからもさまざまな取り組みを続けていきます

「カタログ ショッピングは自動車 OEM によって異なる場合があります。それには多大な業界の努力が必要になるだろう。異種のものはさらに時間がかかります。

アニケット氏は、チップレットはまずデータセンターに導入され、次に自動車に導入されるだろうと述べた。ただし、最初の波は単一ベンダーになります。

まとめ

これは参加者の皆さんの意見と私の意見を組み合わせたものです。

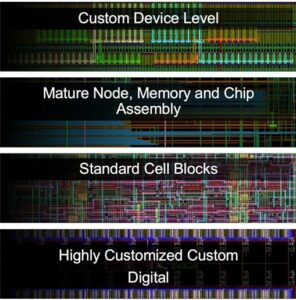

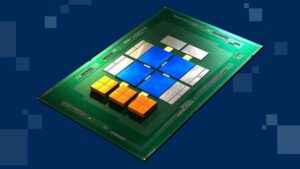

当分の間、チップレットベースの RISC-V 設計は 1 つの企業の取り組みになると思います (おそらく、高帯域幅メモリ (HBM) を除く)。異なる企業の複数のチップレットやインターポーザーを使用して設計を構築するのは複雑すぎます。 、およびそれらすべてを接続するネットワーク (通常は RDL として知られます)。

近い将来、設計は真の 2.5D (ダイが互いに積み重ねられ、スルーシリコン ビアまたは TSV と通信する) ではなく 3D になるでしょう。

自動車には独自の一連の課題があり、特に振動の多い環境でもチップレットベースの設計の信頼性を確保できます。これには広範なテストが必要になります。もう 1 つの問題は、マルチダイ環境における機能安全の確保です。

UCIe は有望であり、ある程度 PCIe に基づいています。 PCIe 企業はプラグフェストを通じて信頼性を確保しました。同様のメカニズムを通じて、チップレットでの UCIe の相互運用性を経済的に確保する方法がわかりません。

最後に、既製のチップレットを購入して妥当なコストでシステムに組み立てることができるという究極の状態に到達するには、技術的な課題に加えて、商業的な課題もあります。最大の課題は、誰がチップレットの在庫を支払い、保有するのかということだ。すべてのチップレットをオンデマンドで製造する必要がある場合、サイクルタイムが速いという利点の多くが失われます。

しかし、RISC-V チップレットは、単一の企業によって製造された 2.5D インターポーザー上のマルチダイ設計の形で確実に急速に登場しています。

また読む:

NoC により、アーキテクトはシステムイン RISC-V 設計に柔軟性を得ることができます

RISC-V コアと NoC をペアリングすると、SoC プロトコルが連携します

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :持っている

- :は

- :not

- :どこ

- $UP

- 100M

- 15年

- 視聴者の38%が

- 167

- 200

- 300

- 3d

- a

- できる

- 私たちについて

- 加速器

- 実際の

- 加えます

- 追加

- 添加

- 利点

- 航空宇宙

- 積極的な

- 前

- AI

- すべて

- 沿って

- また

- 間で

- an

- および

- 発表の

- 別の

- どれか

- 建築家

- です

- ARM

- 周りに

- AS

- 頼む

- 質問

- At

- 自動車

- 背景

- ベース

- BE

- さ

- BEST

- より良いです

- ビッグ

- 最大の

- ビット

- 両言語で

- ビルド

- 建物

- 内蔵

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 呼ばれます

- 缶

- 自動車

- カタログ

- 最高経営責任者(CEO)

- 確かに

- チェーン

- 挑戦する

- 課題

- 安い

- カラー

- 組み合わせ

- 結合

- 来ます

- 到来

- コマーシャル

- 伝える

- 企業

- 会社

- 複雑な

- 複雑な

- お問合せ

- 接続性

- 保守的な

- 見なさ

- コンテキスト

- コントロール

- coo

- 費用

- コスト

- 顧客

- サイクル

- データセンター

- 数十年

- 定義済みの

- 提供します

- によっては

- 依存

- 設計

- 設計

- デザイン

- 死

- 異なります

- 議論する

- 議論

- 優れました

- do

- すること

- ドント

- 各

- 前

- 努力

- end

- エンジニアリング

- 確保

- 確実

- 確保する

- 環境

- 特に

- 誰も

- 除く

- 広範囲

- スピーディー

- 終わり

- 名

- フィット

- 固定の

- 柔軟性

- フレキシブル

- フロー

- 流れ

- 予見

- フォーム

- から

- 機能的な

- さらに

- 未来

- 取得する

- 与える

- ハード

- もっと強く

- 持ってる

- 持って

- ハイ

- ハイパフォーマンス

- HOT

- 認定条件

- HTTPS

- i

- if

- 重要

- in

- 産業を変えます

- 世界全体

- 相互運用性(インターオペラビリティ)

- 相互運用可能な

- に

- インベントリー

- 関係する

- IP

- 問題

- IT

- ITS

- JPG

- キーン

- キープ

- 知っている

- 既知の

- 欠如

- 姓

- う

- ような

- より長いです

- 失われた

- たくさん

- ロー

- make

- 作る

- 管理

- 製造された

- 多くの

- 多くの人々

- 市場

- マーケット

- 最大幅

- 五月..

- 多分

- me

- メカニズム

- 一枚岩

- 他には?

- の試合に

- my

- 必要

- ネットワーク

- 普通

- 新作

- いいえ

- 何も

- 今

- of

- on

- オンデマンド

- ONE

- 開きます

- 意見

- or

- その他

- でる

- 自分の

- パネル

- パネルディスカッション

- 参加者

- 特定の

- 部品

- 支払う

- のワークプ

- おそらく

- 物理的な

- プラットフォーム

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポートフォリオ

- ポスト

- :

- 多分

- プロセッサ

- プロダクト

- 製品管理

- 生産

- 製品

- 有望

- プロトコル

- 提供します

- 購入

- 置きます

- 質問

- 非常に

- レーダー

- 読む

- 本当に

- 合理的な

- 最近

- 関連する

- 信頼性

- 信頼性のある

- 必要とする

- ルーム

- ラン

- 安全性

- 前記

- 規模

- セッション

- セッションに

- 買い物客

- ショッピング

- 同様の

- から

- 小さい

- So

- ソフトウェア

- 幾分

- 特定の

- 積み上げ

- スタック

- 標準

- 規格

- ステートメント

- サミット

- 供給

- サプライチェーン

- サポート

- システム

- 取る

- 会話

- 技術的

- テスト

- それ

- それら

- その後

- そこ。

- 彼ら

- 物事

- 考える

- 考え

- この

- 介して

- ネクタイ

- 時間

- 〜へ

- あまりに

- 取った

- top

- トピック

- true

- 究極の

- 下

- アップデイト

- つかいます

- 通常

- 値

- ベンダー

- ベンダー

- 非常に

- 、

- ボリューム

- vp

- 欲しいです

- ました

- ウェーブ

- we

- went

- した

- この試験は

- いつ

- which

- 誰

- 意志

- もっと悪い

- 年

- 貴社

- ゼファーネット