チップレットは設計の一面を簡素化しましたが、別の面ではパンドラの箱を開けました。それぞれのシミュレーションの複雑さ チップレット は低くなりましたが、現在ではチップレット間の相互接続が複雑になっています。人々は、さまざまな相互接続プロトコル、UCIe のバリエーション、UCIe 設定の変更、インターフェイス速度、物理層の数などを実験しています。ここで、AXI などのレガシー標準、PICe6.0 などの新しいプロトコル、キャッシュ コヒーレンシをミックスに追加します。

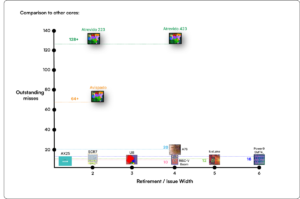

つまり、これにより、まったく新しい一連の実験が作成されます。従来のエミュレーションや RTL モデリングが機能しないものです。まずコンポーネントの選択だけでなく、アーキテクチャのトレードオフに労力を費やす必要があります。これは、トラフィック分析、アプリケーションのパーティショニング、システムのサイジング、およびさまざまな種類の物理層の影響を実行する必要があることを意味します。また、アプリケーションに応じて、ベンチマークは大きく異なります。

UCIe 仕様は新しいため、明確なベンチマークはありません。また、UCIe 仕様では、遅延と電力に関するガイダンスのみが提供されています。どちらも厳しい要件です。これは、電力パフォーマンス領域の調査が避けられないことを意味します。 PCIe 6.0、UCIe、AXI などのプロトコル間変換があるため、モデリングのセットアップは複雑です。

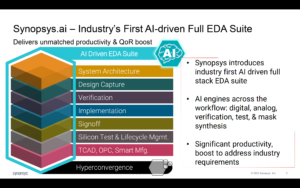

1 つの解決策は、次を使用してシステム モデリングを検討することです。 ビジュアルシム から ミラビリス デザイン。彼らは最近、UCIe システムレベルの IP モデルを発表し、相互接続の多くの使用例をデモンストレーションする予定です。 チップレットサミット。設計者をガイドするために、多くの使用例、予想される電力パフォーマンスの結果、最適化のオプションを記載したガイドを発行しました。サミットでは論文発表とブースの両方を開催します。そこであなたに会えたらいいですね!

また、人々が入手できる論文へのリンクは次のとおりです。 UCIe インターコネクト アーキテクチャに基づく異種コンピューティング システムのパフォーマンス モデリング

要約:

最先端ノードにおける今日の複雑なチップ設計は、通常、複数のダイ (またはチップレット) で構成されています。このアプローチにより、異なるメーカーやプロセスのダイや再利用可能な IP が可能になります。設計者は、このような複雑な状況のさまざまな実装を評価するためのシステム レベルのモデルを必要とします。

システム例は、I/O チップレット、低電力コア チップレット、高性能コア チップレット、オーディオ ビデオ チップレット、およびアナログ チップレットで構成され、Universal Chiplet Interconnect Express (UCIe) 標準を使用して相互接続されています。

私たちのチームは、高度なパッケージと標準パッケージ、さまざまなトラフィック プロファイルとリソース、到達範囲を拡張してタイムアウト時にイベントを評価するリタイマーなど、いくつかのシナリオと構成を検討しました。ミッション アプリケーション向けの UCIe インターコネクトの長所と短所を特定することで、パフォーマンス、電力、機能の要件を満たす各サブシステムの最適な構成を取得することができました。

株式会社ミラビリスデザインについて

Mirabilis Design はシリコンバレーのソフトウェア会社で、製品仕様のリスクを特定して排除し、製品開発に必要な人的リソースと時間的リソースを正確に予測し、多様なエンジニアリング間のコミュニケーションを改善するためのソフトウェアとトレーニング ソリューションを提供しています。

チーム。

VisualSim Architect は、知的財産、システムレベルのモデリング、シミュレーション、環境分析、アプリケーション テンプレートを組み合わせて、モデルの構築、シミュレーション、分析、RTL 検証を大幅に改善します。この環境により、設計者は、相互に依存するさまざまな時間と電力の要件を満たす設計に迅速に収束することができます。これは、設計プロセスの非常に早い段階で、仕様書と並行して (およびその補助として)、製品の実装 (RTL、ソフトウェア コード、回路図など) の前に使用されます。

また読む:

ウェビナー: アーキテクチャ探索中に 95% 以上の精度の電力測定を達成する方法

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :持っている

- :は

- :not

- a

- 正確な

- 正確にデジタル化

- 達成する

- 加えます

- 高度な

- 援助

- ことができます

- 沿って

- また

- an

- 分析

- および

- 別の

- 申し込み

- アプローチ

- 建築

- です

- AREA

- AS

- At

- ベース

- BE

- になる

- ベンチマーク

- ベンチマーク

- の間に

- 両言語で

- ボックス

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- キャッシュ

- 缶

- 取得することができます

- 例

- チップ

- クリア

- コード

- 組み合わせ

- コミュニケーション

- 会社

- 完全に

- 複雑な

- 複雑さ

- コンポーネント

- コンピューティング

- プロフェッショナルな方法で

- 見なさ

- からなる

- 建設

- 収束する

- 変換

- 基本

- コース

- 作成します。

- デモ

- によっては

- 設計

- 設計プロセス

- デザイナー

- デザイン

- 開発する

- 異なります

- 異なる

- 間に

- 各

- 早い

- 努力

- 排除する

- emulation

- 可能

- 環境

- 評価する

- イベント

- 例

- 予想される

- 実験中

- 実験

- 表現します

- 伸ばす

- 名

- から

- フロント

- 機能的な

- 一般に

- 取得する

- でログイン

- ガイダンス

- ガイド

- Hardware

- 持ってる

- 助けました

- こちら

- ハイパフォーマンス

- 希望

- 認定条件

- How To

- HTTPS

- 人間

- i

- 識別する

- 識別

- 影響

- 実装

- 実装

- 改善します

- in

- 含めて

- 知的

- 知的財産

- 相互接続

- インタフェース

- IP

- IT

- JPG

- ただ

- レイテンシ

- 打ち上げ

- 層

- 層

- Legacy

- レベル

- ような

- LINK

- 見て

- たくさん

- ロー

- 下側

- メーカー

- 最大幅

- 意味する

- 手段

- 測定

- 大会

- ミーツ

- ミッション

- ミックス

- モデリング

- モデリング

- の試合に

- 必要

- 新作

- いいえ

- ノード

- 今

- 数

- 入手する

- of

- on

- ONE

- の

- 開いた

- 開かれた

- 最適な

- 最適化

- オプション

- or

- パッケージ

- 紙素材

- 並列シミュレーションの設定

- パフォーマンス

- 物理的な

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポスト

- 電力

- 予測

- プレゼンテーション

- プロセス

- ラボレーション

- プロダクト

- 対応プロファイル

- 財産

- プロトコル

- は、大阪で

- 提供

- 公表

- 急速に

- リーチ

- 読む

- 最近

- の提出が必要です

- 要件

- リソース

- 結果

- 再利用可能な

- リスク

- シナリオ

- 選択

- セッションに

- 設定

- いくつかの

- 著しく

- シリコン

- シリコンバレー

- 簡略化されました

- 状況

- So

- ソフトウェア

- 溶液

- ソリューション

- 仕様

- 速度

- 過ごす

- 標準

- 規格

- 強み

- 厳しい

- 勉強

- そのような

- サミット

- チーム

- テンプレート

- それ

- そこ。

- 彼ら

- この

- 時間

- 〜へ

- 伝統的な

- トラフィック

- トレーニング

- ユニバーサル

- us

- つかいます

- 中古

- 谷

- バリエーション

- Verification

- 非常に

- 、

- 弱点

- WELL

- which

- 意志

- 仕事

- 書かれた

- 貴社

- ゼファーネット