Al recente vertice RISC-V, l'ultima sessione è stata un panel sui chiplet chiamato Chiplet nell'ecosistema RISC-V. È stato moderato da Calista Redmond, CEO di RISC-V International. I relatori erano:

- Laurent Moll, direttore operativo di Arteris

- Aniket Saha, vicepresidente della gestione del prodotto di Tenstorrent

- Dale Greenley, vicepresidente dell'ingegneria di Ventana Microsystems

- Rob Aitken, illustre architetto di Synopsys

Questa è una combinazione di argomenti un po' strana per me. Ovviamente, puoi inserire un processore RISC-V su un chiplet ma le sfide non sono molto diverse da quelle di qualsiasi altro processore. Ma RISC-V è caldo, così come i chiplet, e aziende come Ventana li stanno combinando.

Permettetemi di darvi un po' di informazioni sulle aziende per inserirle nel contesto:

- Come probabilmente saprai, Arteris realizza reti su chip (NoC). È un'azienda neutrale rispetto ai fornitori di chiplet (e fornitori di IP).

- Tenstorrent sta progettando un portafoglio di chip RISC-V multicore ad altissime prestazioni

- Ventana ha l'IP RISC-V ma lo fornisce anche come chiplet

- Synopsys è ovviamente una società EDA, ma ha annunciato i core RISC-V all'inizio del summit

]

La discussione vera e propria

La prima domanda di Calista è stata una palla da softball che chiedeva quale fosse il valore dei chiplet.

Dale ha affermato che non c'è nulla di specifico in RISC-V per i chiplet, ma è il mercato a decidere quando realizzare grandi cose monolitiche o chiplet. Dipende da cosa ti pagherà un cliente per fare. "Forniamo sia IP che chiplet, c'è spazio per entrambi."

Aniket ha affermato che "fare chiplet non è economico, ma fare chiplet e RISC-V è flessibile e puoi realizzare rapidamente nuovi prodotti".

Laurent ha optato per i costi di produzione. NRE è molto importante da tenere sotto controllo poiché non molte persone costruiscono parti da 100 milioni. Quindi ci sono più fornitori coinvolti e una catena di fornitura complicata. Un SoC è complesso ma i chiplet sono peggiori.

Rob ha sottolineato l'eterogeneità come l'aggiunta di chiplet per RF e analogico, la presenza di un acceleratore opzionale e così via. Ciò apre potenzialmente nuovi mercati.

Calista ha continuato chiedendo a che punto siamo nel settore automobilistico.

Aniket ha sottolineato che il settore automobilistico è molto conservatore e ora è aggressivo nei confronti delle piattaforme che possono scalare dalle auto di fascia bassa alle auto di fascia alta. Con i chiplet nessuno ha veramente considerato la sicurezza funzionale.

Rob si è occupato di settore aerospaziale (non proprio automobilistico) e ha discusso di come di solito esista un volume fisico fisso definito decenni fa. È difficile adattare le cose.

Laurent: Le aziende automobilistiche sono gli acquirenti di cataloghi per eccellenza e i chiplet consentono loro di prendere il meglio in termini di intelligenza artificiale, radar, infotainment e così via.

Come si fa a far funzionare il software?

Rob: se rendi il sistema piccolo, va bene. Ma lo shopping nel catalogo automobilistico rende tutto più difficile.

Aniket: Correlata un'affermazione “se lo aggiungi non lo useremo”. Gli stack software automobilistici supporteranno RISC-V tra 5 anni, ovvero in tempi rapidi. Arm ha impiegato 15 anni per arrivarci.

D: Di cosa abbiamo bisogno per la connettività?

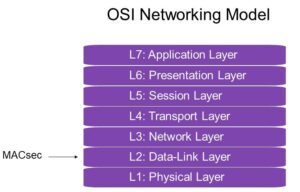

Laurent: È molto complesso soprattutto con la gente che fa la spesa per i chiplet. I PHY di fornitori diversi potrebbero essere interoperabili. Tutti sono entusiasti dell’UCIe. Le persone vogliono standard che rendano i chiplet più adatti.

Aniket si è lamentato del fatto che non esistono flussi di progettazione standard per il chiplet. Una grande mancanza di standard.

Rob pensa che possiamo creare un flusso standard ma con chiplet diversi non vogliamo N flussi di progettazione diversi.

D: Come vedi le cose tra 3-5 anni?

Rob: saremo più avanti insieme a diversi

“L'acquisto del catalogo potrebbe dipendere dagli OEM automobilistici. Ci vorrà un grande sforzo da parte dell’industria. Qualsiasi materiale eterogeneo richiederà più tempo.

Aniket ha affermato che i chiplet saranno prima nei data center e poi nel settore automobilistico. Ma la prima ondata sarà a fornitore unico.

In breve

Questa è una combinazione di cose che hanno detto i partecipanti e delle mie opinioni.

Penso che per il momento, i progetti RISC-V basati su chiplet saranno un impegno di una sola azienda (tranne, forse, per la memoria a larghezza di banda elevata (HBM). È troppo complesso costruire progetti con più chiplet di diverse aziende, interposer e la rete per collegarli tutti, solitamente nota come RDL.

I progetti saranno 2.5D e non 3D (dove i die sono impilati uno sopra l'altro e comunicano con passanti in silicio o TSV) per il prossimo futuro.

Il settore automobilistico deve affrontare una serie di sfide, in particolare garantire che i progetti basati su chiplet siano affidabili in un ambiente con molte vibrazioni. Ciò richiederà test approfonditi. Un altro problema è garantire la sicurezza funzionale in un ambiente multi-die.

UCIe è promettente ed è in qualche modo basato su PCIe. Le aziende PCIe hanno garantito l'affidabilità attraverso i plugfest. Non vedo come si possa garantire economicamente l'interoperabilità UCIe nei chiplet attraverso un meccanismo simile.

Infine, oltre alle sfide tecniche, ci sono sfide commerciali se vogliamo raggiungere il nirvana di poter acquistare chiplet standard e assemblarli in sistemi a un costo ragionevole. La sfida più grande è chi pagherà e manterrà l’inventario dei chiplet. Se tutti i chiplet dovessero essere prodotti su richiesta, molti dei vantaggi di un tempo di ciclo rapido andrebbero persi.

Ma i chiplet RISC-V stanno sicuramente arrivando rapidamente sotto forma di progetti multi-die su interposer 2.5D costruiti da un'unica azienda.

Leggi anche:

I NoC offrono agli architetti flessibilità nella progettazione del sistema RISC-V

L'abbinamento dei core RISC-V con i NoC lega insieme i protocolli SoC

Aggiornamento #60DAC da Arteris

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :ha

- :È

- :non

- :Dove

- $ SU

- 100M

- 15 anni

- 15%

- 167

- 200

- 300

- 3d

- a

- capace

- WRI

- acceleratore

- presenti

- aggiungere

- l'aggiunta di

- aggiunta

- vantaggi

- Aeronautico

- aggressivo

- fa

- AI

- Tutti

- lungo

- anche

- tra

- an

- ed

- ha annunciato

- Un altro

- in qualsiasi

- architetti

- SONO

- ARM

- in giro

- AS

- chiedere

- chiedendo

- At

- settore automobilistico

- sfondo

- basato

- BE

- essendo

- MIGLIORE

- Meglio

- Big

- Maggiore

- Po

- entrambi

- costruire

- Costruzione

- costruito

- ma

- by

- detto

- Materiale

- auto

- catalogo

- ceo

- certamente

- catena

- Challenge

- sfide

- economico

- colore

- combinazione

- combinando

- Venire

- arrivo

- comunicare

- Aziende

- azienda

- complesso

- complicato

- Connettiti

- Connettività

- prudente

- considerato

- contesto

- di controllo

- tubare

- Costo

- Costi

- cliente

- ciclo

- Datacenter

- decenni

- definito

- fornisce un monitoraggio

- Dipendente

- dipende

- Design

- progettazione

- disegni

- *

- diverso

- discusso

- discussione

- Distinto

- do

- fare

- Dont

- ogni

- In precedenza

- sforzo

- fine

- Ingegneria

- garantire

- assicurato

- assicurando

- Ambiente

- particolarmente

- tutti

- Tranne

- estensivo

- FAST

- sottile

- Nome

- in forma

- fisso

- Flessibilità

- flessibile

- flusso

- flussi

- Nel

- prevedibile

- modulo

- da

- funzionale

- ulteriormente

- futuro

- ottenere

- Dare

- Hard

- Più forte

- Avere

- avendo

- Alta

- Alte prestazioni

- tenere

- HOT

- Come

- HTTPS

- i

- if

- importante

- in

- industria

- Internazionale

- Interoperabilità

- interoperabile

- ai miglioramenti

- inventario

- coinvolto

- IP

- problema

- IT

- SUO

- jpg

- Acuto

- mantenere

- Sapere

- conosciuto

- Dipingere

- Cognome

- lasciare

- piace

- più a lungo

- perso

- lotto

- Basso

- make

- FA

- gestione

- manufatto

- molti

- molte persone

- Rappresentanza

- Mercati

- max-width

- Maggio..

- può essere

- me

- meccanismo

- Monolitico

- Scopri di più

- multiplo

- my

- Bisogno

- Rete

- Neutres

- New

- no

- Niente

- adesso

- of

- on

- On-Demand

- ONE

- apre

- Opinioni

- or

- Altro

- su

- proprio

- pannello di eventi

- tavola rotonda

- partecipanti

- particolare

- Ricambi

- Paga le

- Persone

- Forse

- Fisico

- Piattaforme

- Platone

- Platone Data Intelligence

- PlatoneDati

- lavori

- Post

- potenzialmente

- probabilmente

- Processore

- Prodotto

- gestione del prodotto

- Produzione

- Prodotti

- promettente

- protocolli

- fornire

- Acquista

- metti

- domanda

- abbastanza

- radar

- Leggi

- veramente

- ragionevole

- recente

- relazionato

- problemi di

- affidabile

- richiedere

- Prenotazione sale

- Correre

- Sicurezza

- Suddetto

- Scala

- vedere

- Sessione

- set

- Shoppers

- Shopping

- simile

- da

- singolo

- piccole

- So

- Software

- piuttosto

- specifico

- impilato

- Stacks

- Standard

- standard

- dichiarazione

- Vertice

- fornire

- supply chain

- supporto

- sistema

- SISTEMI DI TRATTAMENTO

- Fai

- parlando

- Consulenza

- Testing

- che

- Il

- Li

- poi

- Là.

- di

- cose

- think

- pensa

- questo

- Attraverso

- Cravatte

- tempo

- a

- pure

- ha preso

- top

- Argomenti

- vero

- ultimo

- per

- Aggiornanento

- uso

- generalmente

- APPREZZIAMO

- venditore

- fornitori

- molto

- via

- volume

- vp

- volere

- Prima

- Wave

- we

- è andato

- sono stati

- Che

- quando

- quale

- OMS

- volere

- con

- peggio

- anni

- Tu

- zefiro