Quando pensi a "FPGA", cosa ti viene in mente? Parti massicce e costose in grado di contenere molta logica ma anche di consumare molta energia. Piattaforme riconfigurabili in grado di assorbire RTL per un progetto SoC nei test pre-silicio. Grandi acquisizioni aziendali vistose in cui gli investitori hanno fatto un sacco di soldi. Confezione 3D esotica e interconnessioni avanzate. Ma probabilmente non è economico, pacchetto piccolo, numero di pin basso, parti di alimentazione a basso consumo, giusto? L'eFPGA di Flex Logix torna alle origini per la logica programmabile a basso consumo che può accettare dispositivi a basso costo, volume più elevato e dimensioni limitate.

Due strade programmabili hanno presentato una scelta

A rischio di uscire con me stesso, la mia prima esposizione a quella che allora era chiamata tecnologia FPGA risale a quando Altera ha lanciato la sua famiglia EP1200 basata su EPROM in un pacchetto DIP a 40 pin con il suo clock a 16 MHz, 400 mW di potenza attiva e 15 mW in standby energia. È arrivato con un editor schematico e una libreria di macro di gate. I progettisti disegnavano la loro logica, "bruciavano" la loro parte, la testavano, la gettavano sotto una lampada UV e la cancellavano se non funzionava, e riprovavano.

Poco dopo, in un altro dei nostri laboratori è apparsa una scheda con alcuni dei primi FPGA Xilinx. Questi erano basati su RAM anziché su EPROM: più grandi, più veloci e riprogrammabili senza che la lampada UV attendesse o rimuovesse la parte dalla scheda. Anche la logica all'interno era più complessa, con l'introduzione di moltiplicatori veloci. Queste parti potrebbero non solo spazzare via la logica, ma potrebbero anche essere utilizzate per esplorare la capacità di elaborazione del segnale digitale personalizzata con rapidi cicli di riprogettazione.

Ciò ha dato il via alla corsa agli armamenti al silicio programmabile e si è sviluppata una biforcazione tra il PLD (dispositivo logico programmabile) e l'FPGA. I produttori hanno fatto delle scelte, con Altera e Xilinx che hanno intrapreso la strada maestra della scalabilità FPGA e Actel, Lattice e altri hanno intrapreso la strada inferiore della flessibilità PLD per la "logica collante" per ridurre i costi della distinta base.

eFPGA sposta l'equazione della logica programmabile a bassa potenza

Tutto ciò suona come un mercato maturo, con un'elevata barriera all'ingresso da un lato e un'offerta più mercificata dall'altro. Ma cosa succederebbe se la logica programmabile fosse un blocco IP che potrebbe essere progettato in qualsiasi chip in questa era favolosa, incluso un piccolo FPGA a bassa potenza? Ciò aggirerebbe la barriera (almeno nelle offerte di fascia bassa e media) e la mercificazione.

Flex Logix ha affrontato questa sfida con l'EFLX 1K eFPGA Tile. Ogni riquadro logico ha 560 tabelle di ricerca (LUT) a sei input con RAM, clocking e interconnessione. La disposizione dei riquadri EFLX offre la possibilità di gestire vari ruoli logici e DSP. Ma le sue caratteristiche più importanti potrebbero essere le dimensioni e la gestione dell'alimentazione.

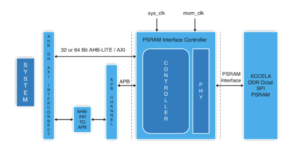

Realizzata in TSMC 40ULP, la piastrella EFLX 1K si adatta a 1.5 mm2 e offre power-gating per le modalità di sospensione profonda con ritenzione dello stato, molto più aggressivo rispetto ai PLD tradizionali. EFLX 1K ha anche funzionalità pronte per la produzione prese in prestito dagli FPGA. Presenta interfacce AXI o JTAG per la configurazione bitstream, circuiti di readback che consentono il controllo soft degli errori e una modalità di test con vettori semplificati che migliorano la copertura e riducono i tempi di test.

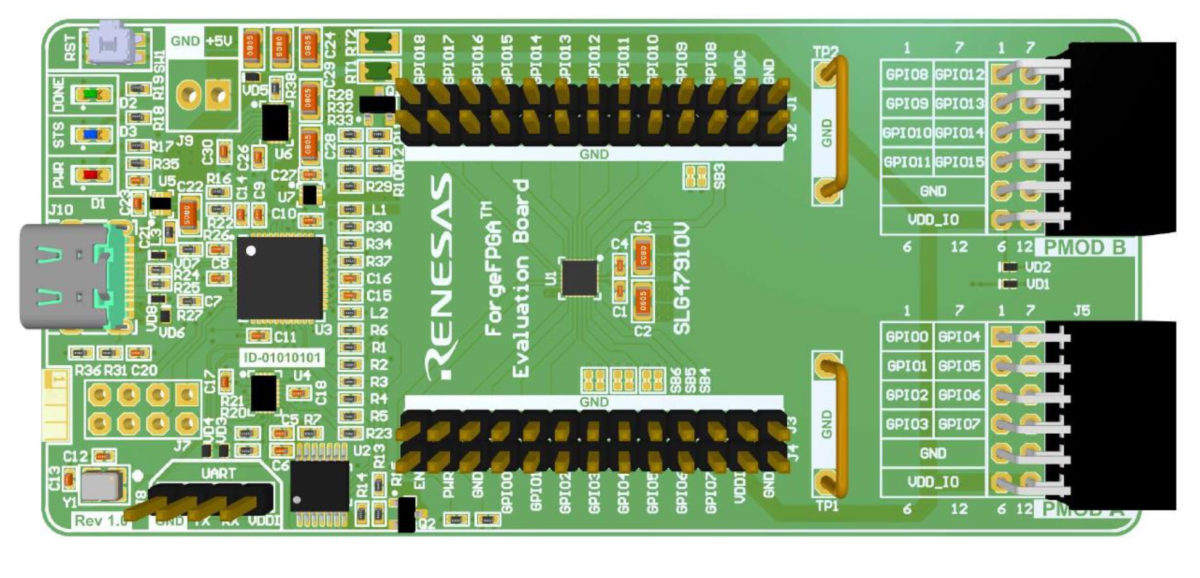

Vedi il chip al centro di questa prossima immagine? Questo è un ForgeFPGA di Renesas in un pacchetto QFN-24, basato su IP EFLX 1K, che Renesas offre a un prezzo inferiore a $ 1 in volume. La sua corrente di destinazione in standby effettua il check-in a meno di 20uA. Dimensioni ridotte, costi inferiori e meno alimentazione aprono porte precedentemente chiuse agli FPGA. Il lignaggio di ForgeFPGA risale a Silego Technology, quindi a Dialog Semiconductor, acquisita da Renesas nel 2021.

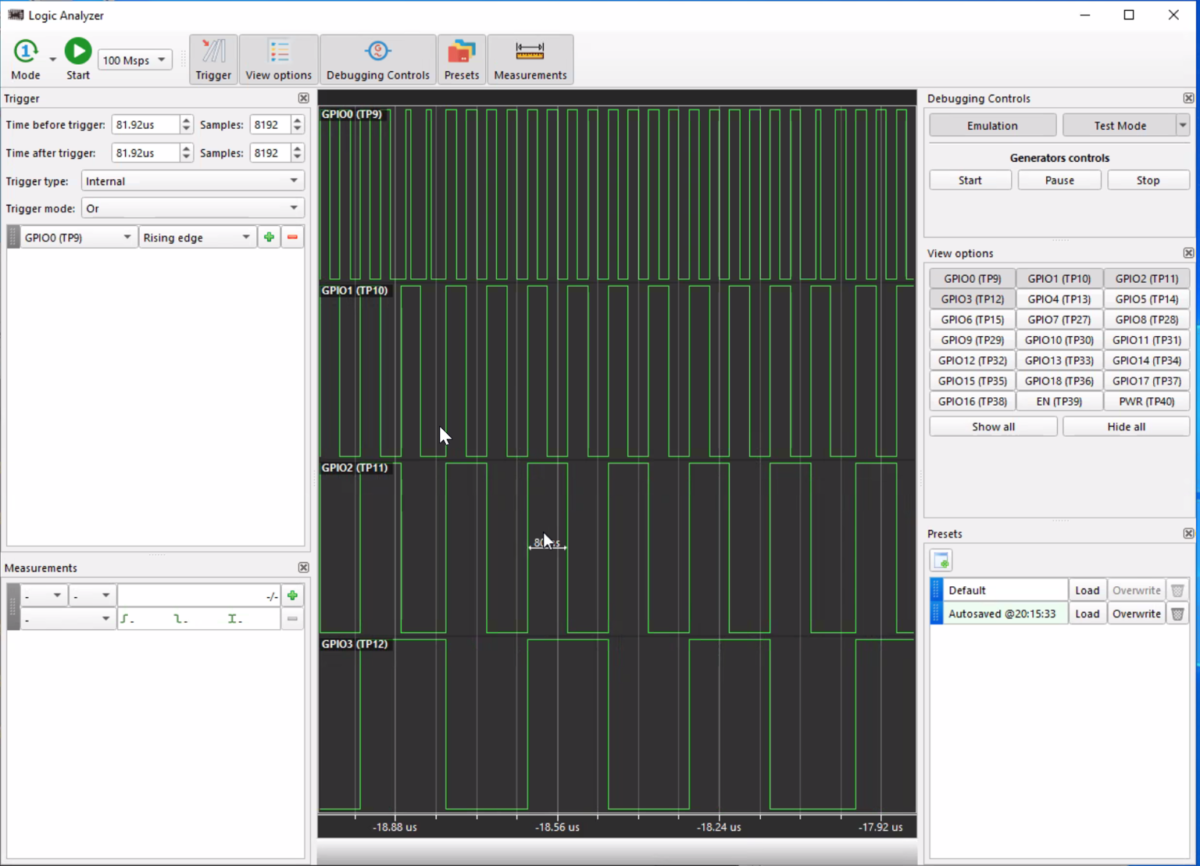

Renesas introduce l'ambiente IDE Go Configure, aggiungendo un'interfaccia utente grafica al compilatore Flex Logix EFLX. Supporta la mappatura dei pin ForgeFPGA, la compilazione di Verilog, la generazione di un flusso di bit e dispone di un analizzatore logico leggero.

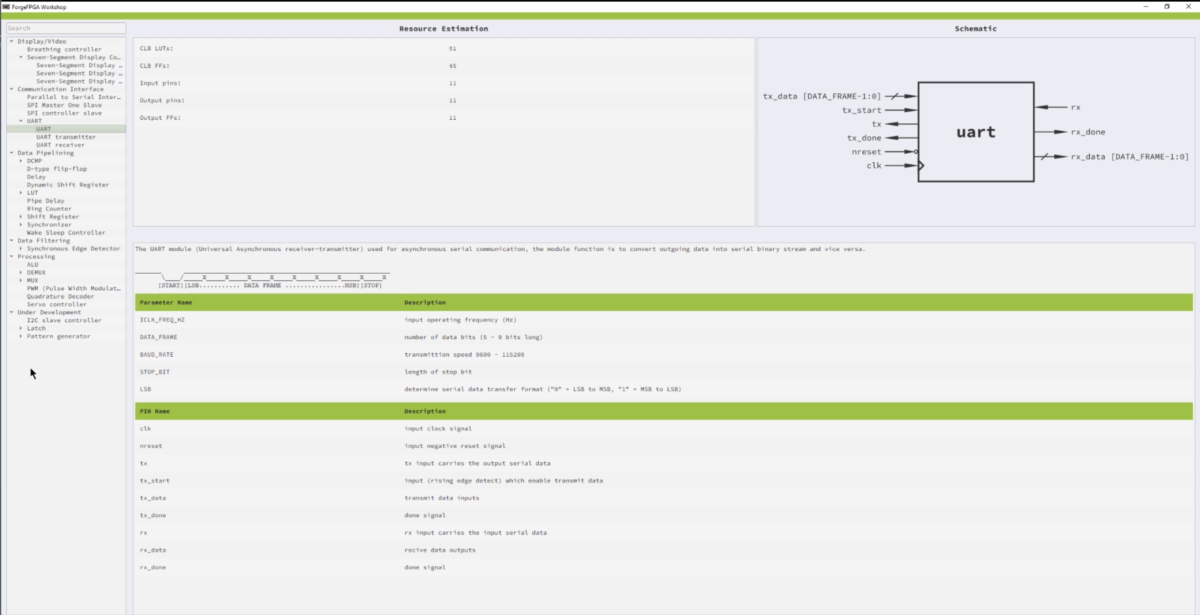

I blocchi applicativi predefiniti per ForgeFPGA ne hanno uno interessante che Geoff Tate di Flex Logix sottolinea: un UART. Creare un UART in logica non è poi così difficile, ma si scopre che ognuno l'ha fatto in modo diverso, ed è solo una logica sufficiente per essere più di un paio di chip discreti. Un ForgeFPGA è un pezzo di logica riconfigurabile che può risolvere questo problema, consentendo a un'implementazione hardware di adattarsi rapidamente a varie configurazioni.

ForgeFPGA è solo un esempio di ciò che si può fare con Flex Logix EFLX 1K eFPGA Tile. Flex Logix è in grado di adattare l'IP per vari nodi di processo e la capacità di tiling mix-and-match offre scalabilità. Raggiunge nuovi minimi per la logica programmabile a bassa potenza e consente ai produttori di chip di differenziare le soluzioni in modi straordinari. Per maggiori informazioni, visitare:

Famiglia Flex Logix EFLX eFPGA

Leggi anche:

eFPGA che gestiscono l'agilità crittografica per SoC con PQC

Flex Logix: il primo sistema basato su Mini-ITX integrato con intelligenza artificiale del settore

Flex Logix collabora con l'ID intrinseco per proteggere la piattaforma eFPGA

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Fonte: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :È

- $ SU

- 1

- 2021

- 3d

- a

- capacità

- WRI

- a proposito

- Realizza

- acquisito

- acquisizioni

- attivo

- adattare

- Avanzate

- Dopo shavasana, sedersi in silenzio; saluti;

- aggressivo

- AI

- Tutti

- Consentire

- consente

- ed

- Un altro

- Applicazioni

- At

- precedente

- barriera

- basato

- Nozioni di base

- BE

- fra

- Big

- maggiore

- Bloccare

- Blocchi

- tavola

- preso in prestito

- Porta

- portato

- by

- detto

- Materiale

- capace

- centro

- Challenge

- verifica

- Controlli

- patata fritta

- Chips

- scelte

- Orologio

- chiuso

- complesso

- Configurazione

- Aziende

- Costo

- Costi

- potuto

- Coppia

- copertura

- Creazione

- Corrente

- costume

- cicli

- Incontri

- deep

- Design

- progettato

- designer e gli illustratori veneziani,

- sviluppato

- dispositivo

- dispositivi

- dialogo

- differenziare

- difficile

- digitale

- Dip

- porte

- ogni

- editore

- consentendo

- abbastanza

- iscrizione

- Ambiente

- epoca

- errore

- valutazione

- tutti

- esempio

- Esotico

- costoso

- esplora

- Esposizione

- famiglia

- FAST

- più veloce

- Caratteristiche

- Nome

- Flessibilità

- Nel

- FPGA

- da

- la generazione di

- dà

- Go

- va

- maniglia

- Manovrabilità

- Hardware

- Avere

- Alta

- superiore

- possesso

- HTTPS

- ID

- Immagine

- implementazione

- miglioramento

- in

- Compreso

- dell'industria

- poco costoso

- info

- invece

- integrato

- interessante

- Interfaccia

- interfacce

- intrinseco

- Introduzione

- Investitori

- IP

- IT

- SUO

- jpg

- solo uno

- Labs

- Biblioteca

- leggero

- piace

- lotto

- Basso

- abbassamento

- Direzione del vento:

- Macro

- macro

- fatto

- Makers

- gestione

- Produttori

- mappatura

- Rappresentanza

- massiccio

- alunni

- max-width

- mente

- Moda

- modalità di

- soldi

- Scopri di più

- maggior parte

- New

- GENERAZIONE

- nodi

- of

- offerta

- offerte

- Offerte

- on

- ONE

- aprire

- Altro

- Altri

- pacchetto

- imballaggio

- parte

- partner

- Ricambi

- pino

- Piattaforme

- Platone

- Platone Data Intelligence

- PlatoneDati

- per favore

- punti

- Post

- energia

- presentata

- presents

- in precedenza

- prezzo

- probabilmente

- Problema

- processi

- lavorazione

- prominente

- Mettendo

- rapidamente

- Gara

- RAM

- veloce

- Leggi

- ridisegnare

- ridurre

- notevole

- rimozione

- ritenzione

- Rischio

- strada

- strade

- ruoli

- Scalabilità

- sicuro

- semiconduttore

- set

- Turni

- Signal

- Silicio

- Taglia

- sonno

- piccole

- inferiore

- Soft

- Soluzioni

- RISOLVERE

- alcuni

- Regione / Stato

- aerodinamico

- supporti

- Sweep

- Fai

- presa

- Target

- Tecnologia

- test

- Testing

- che

- Il

- loro

- Strumenti Bowman per analizzare le seguenti finiture:

- volte

- a

- tonnellate

- top

- tradizionale

- tsmc

- per

- Utente

- Interfaccia utente

- vario

- via

- Visita

- volume

- aspettare

- modi

- Che

- quale

- con

- senza

- Lavora

- sarebbe

- zefiro