Ha megnézzük a félvezetőipar elmúlt 25 év alatti terjeszkedését, úgy tűnik, hogy a tervezési IP alkalmazása minden alkalmazásban a siker egyik fő tényezője, a szilíciumtechnológia x100-as faktorral hihetetlen fejlődése, a 250-as 2018 nm-ről 3 nm-re (ha Nem 2nm) 2023-ban. Előrelátjuk, hogy a chiplet-alapú architektúrára való átállás hamarosan ugyanazt a szerepet fogja betölteni, mint a 2000-es években az SoC chip-alapú architektúra és a tervezési IP tömeges használata.

A kérdés az, hogy hogyan lehet pontosan megjósolni a chiplet elfogadásának időkeretét, és mik lesznek ennek a forradalomnak a kulcsfontosságú tényezői. Meglátjuk, hogy az innovációs elmélet diffúziója hasznos lehet-e az előrejelzés finomhangolásában, és meghatározzuk, hogy milyen típusú alkalmazás lesz a mozgatórugója. A chip-to-chip összekapcsolási protokoll szabványos specifikációi, amelyek lehetővé teszik a gyors iparági átvételt, az olyan alkalmazások, mint az IA vagy az okostelefon-alkalmazás-processzorok gyors meghajtását, a legfontosabbnak tűnnek, de az EDA-eszközök hatékonysága vagy az új technológiák csomagolása, valamint a dedikált fejlesztések kulcsfontosságúak többek között.

Bevezetés: a chiplet technológia megjelenése

A 2010-es évtized során a Moore-törvény előnyei kezdtek szétesni. Moore törvénye szerint a tranzisztorok sűrűsége kétévente megduplázódik, a számítási költség ennek megfelelő 50%-kal csökken. A Moore-törvény változása annak köszönhető, hogy a tranzisztor szerkezete a síkbeli eszközöktől a Finfet-ekig terjed a tervezés bonyolultabbá tételében. A finfeteknek többszörös mintázatra van szükségük a litográfiához, hogy az eszköz méreteit 20 nm alatti csomópontokhoz érjék el.

Ennek az évtizednek a végén a számítástechnikai igények robbanásszerűen megnőttek, elsősorban az adatközpontok elterjedése, valamint az előállított és feldolgozott adatmennyiség miatt. Valójában a mesterséges intelligencia (AI) és az olyan technikák, mint a gépi tanulás (ML) átvételét ma már egyre több adat feldolgozására használják, és a szerverek jelentősen megnövelték számítási kapacitásukat. A szerverek sokkal több CPU magot adtak hozzá, nagyobb GPU-kat integráltak, amelyeket kizárólag ML-hez használnak, már nem használnak grafikához, és beágyazott egyedi ASIC AI-gyorsítókat vagy kiegészítő, FPGA-alapú AI-feldolgozást. A korai mesterséges intelligencia chip-terveket nagyobb monolit SoC-k segítségével valósították meg, némelyikük elérte az irányzék által szabott mérethatárt, körülbelül 700 mm-t.2.

Ezen a ponton a kisebb SoC-re, valamint különféle számítási és IO chipletekre való szétbontás tűnik a megfelelő megoldásnak. Számos chipgyártó, mint például az Intel, az AMD vagy a Xilinx, ezt a lehetőséget választotta a gyártásba kerülő termékekhez. A The Linley Group kiváló fehér könyve, „A chipletek gyors átvétele: miért válnak kicsivé a nagy zsetonok”, kimutatta, hogy ez a lehetőség jobb költségeket eredményez a monolitikus SoC-okhoz képest, mivel a nagyobb hozamot befolyásolja. Ezek a chipgyártók homogén chipletet terveztek, de az olyan összekapcsolási szabványok megjelenése és elfogadása, mint az Universal Chiplet Interconnect Express (UCIe) IP, megkönnyíti a heterogén chiplet alkalmazását.

Az újabb, gyorsabb protokollszabványok fejlődése felgyorsul, ahogy az iparág folyamatosan nagyobb teljesítményt kér. Sajnos a különféle szabványokat nem egyetlen szervezet szinkronizálja. Az új PCIe szabványok egy évvel (vagy többel) korábban vagy később érkezhetnek, mint az új Ethernet protokoll szabvány. A heterogén integráció alkalmazása lehetővé teszi a szilícium-szolgáltatók számára, hogy csak az adott chiplet kialakításának megváltoztatásával alkalmazkodjanak a gyorsan változó piachoz. Tekintettel arra, hogy a fejlett SoC tervezési gyártás hatalmas beruházási ráfordítást igényel az 5 nm-es, 4 nm-es vagy 3 nm-es folyamatcsomópontok esetében, a chiplet architektúrák óriási hatással vannak a jövőbeli innovációkra a félvezető térben.

A heterogén chipletkialakítás lehetővé teszi, hogy különböző alkalmazásokat vagy piaci szegmenseket célozhassunk meg úgy, hogy csak a megfelelő chipleteket módosítjuk vagy hozzáadjuk, miközben a rendszer többi részét változatlanul hagyjuk. Az új fejlesztések gyorsabban, lényegesen kisebb befektetéssel kerülhetnek piacra, mivel az átalakítás csak a chipletek elhelyezésére használt csomagolóanyagot érinti. Például a számítási chiplet áttervezhető TSMC 5 nm-ről TSMC 3 nm-re, hogy integrálja a nagyobb L1 gyorsítótárat vagy nagyobb teljesítményű CPU-t vagy CPU magok számát, miközben a rendszer többi része változatlan marad. A chipletet integráló SerDes-ek újratervezhetők a gyorsabb sebesség érdekében az új folyamatcsomópontokon, amelyek nagyobb IO sávszélességet kínálnak a jobb piaci pozíció érdekében.

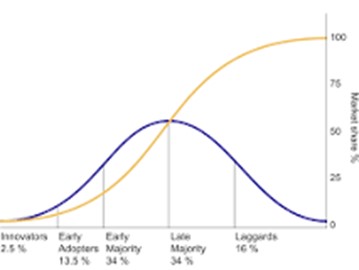

Heterogén chiplet használata jobb Time-to-Market (TTM) lehetőséget biztosít a rendszer frissítése során, és a rendszer egy részét változtatás nélkül újrahasználja, ha chipletben tervezték. Ez egy mód a költségek minimalizálására is, ha néhány funkcionális chipletet kevésbé fejlett csomópontokon tartanak, olcsóbbak, mint a legfejlettebbek. A fő kérdés azonban az, hogy előre jelezzük, mikor fog a chiplet technológia jelentős szegmenst létrehozni a félvezetőpiacon? Áttekintjük az IP átvételi előzményeket, mivel a chiplet és az IP hasonló, mindkettőnek meg kell törnie az NIH-szindrómát, hogy sikeres legyen. Kivonjuk a chiplet átvételének fő okait, és előrejelzést készítünk az innovációs elmélet és a meghatározott kategória (Innovátorok, Korai alkalmazók stb., lásd lenti ábra) felhasználásával.

Áttekintjük az ARM CPU IP átvételét 1991 és 2018 között, valamint az IP átvételi előzményeket 1995 és 2027 között, és ellenőrizzük, hogy ez az elfogadási arány hogyan illeszkedik az innovációs elmélethez.

Elmagyarázzuk, hogy miért fog fellendülni a chiplet bevezetése, áttekintve a technológiával és marketinggel kapcsolatos okokat:

- Az IP-alapú SoC-től a chiplet alapú rendszerig

- Együttműködés a chiplet interconnect preferált protokoll szabványnak köszönhetően

- Elmagyarázza, hogy a csúcskategóriás interfész IP miért kulcsfontosságú a Chiplet bevezetésében

- Megoldandó tervezéssel kapcsolatos kihívások.

- Végül, de nem utolsósorban az öntöde által végzett beruházás

Végül az innovációs elméletre alapozva egy kísérleti chiplet-elfogadási előrejelzést készíthetünk. Csak hogy megemlítsük, az iparág éppen a „korai alkalmazók” fázisába lépett, és számos IP- és chiplet-szállító szolgálja ki a HPC-t és az AI-t.

Ha letölti a fehér papír, élvezni fogja az összes szöveget és számos képet, amelyek közül néhány kizárólag ehhez a munkához készült.

By Eric Esteve (PhD.) elemző, tulajdonos IPnest

Az Alphawave támogatta ennek a fehér könyvnek a létrehozását, de a vélemények és elemzések a szerző sajátjai. A cikk itt található:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Is Read:

Interfész IP 2022-ben: 22%-os éves növekedés továbbra is adatközpontú

Oszd meg ezt a bejegyzést ezen keresztül:

- SEO által támogatott tartalom és PR terjesztés. Erősödjön még ma.

- PlatoData.Network Vertical Generative Ai. Erősítse meg magát. Hozzáférés itt.

- PlatoAiStream. Web3 Intelligence. Felerősített tudás. Hozzáférés itt.

- PlatoESG. Carbon, CleanTech, Energia, Környezet, Nap, Hulladékgazdálkodás. Hozzáférés itt.

- PlatoHealth. Biotechnológiai és klinikai vizsgálatok intelligencia. Hozzáférés itt.

- Forrás: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :van

- :is

- :nem

- $ UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- Rólunk

- gyorsítók

- Elérése

- alkalmazkodni

- hozzáadott

- hozzáadásával

- alkalmazók

- Örökbefogadás

- fejlett

- AI

- AI adatok

- Minden termék

- lehetővé téve

- lehetővé teszi, hogy

- Is

- AMD

- között

- összeg

- elemzés

- elemző

- és a

- külön

- Megjelenik

- Alkalmazás

- alkalmazások

- építészet

- VANNAK

- ARM

- cikkben

- mesterséges

- mesterséges intelligencia

- Mesterséges intelligencia (AI)

- AS

- ASIC

- kér

- At

- szerző

- Sávszélesség

- alapján

- BE

- válik

- kezdődött

- hogy

- lent

- Előnyök

- Jobb

- Nagy

- Javítottak

- mindkét

- szünet

- épít

- de

- by

- cache

- TUD

- Kapacitás

- tőke

- Kategória

- okai

- biztosan

- kihívások

- változik

- változó

- olcsóbb

- ellenőrizze

- csip

- játékpénz

- hogyan

- képest

- kiegészítő

- bonyolultság

- Kiszámít

- számítástechnika

- figyelembe véve

- Megfelelő

- Költség

- kiadások

- tudott

- CPU

- teremt

- készítette

- teremtés

- szokás

- dátum

- évtized

- elszánt

- meghatározott

- sűrűség

- Design

- tervezett

- tervek

- Határozzuk meg

- Fejlesztés

- fejlesztések

- Eszközök

- különböző

- Diffusion

- méretek

- megduplázódott

- letöltés

- hajtás

- gépkocsivezető

- vezetés

- két

- alatt

- Korábban

- Korai

- korai alkalmazók

- lazítás

- ökoszisztéma

- hatékonyság

- beágyazott

- megjelenése

- engedélyező

- lehetővé téve

- végén

- élvez

- stb.

- egyre növekvő

- Minden

- evolúció

- példa

- kiváló

- kizárólagosan

- terjeszkedés

- Magyarázza

- expressz

- kivonat

- tény

- tényező

- tényezők

- Esik

- GYORS

- gyorsabb

- Ábra

- A

- Előrejelzés

- előre lát

- talált

- FPGA

- ból ből

- funkcionális

- jövő

- Nyereség

- generált

- szerzés

- megy

- GPU

- grafika

- Csoport

- Növekedés

- Legyen

- hasznos

- itt

- High-End

- <p></p>

- történelem

- Ház

- Hogyan

- How To

- hpc

- HTTPS

- ia

- if

- Hatás

- végre

- kiszabott

- in

- <p></p>

- növekvő

- hihetetlen

- ipar

- Innováció

- innovátorok

- integrálni

- integrált

- integrálása

- integráció

- Intel

- Intelligencia

- Felület

- bele

- beruházás

- IP

- IT

- jpg

- éppen

- tartás

- Kulcs

- nagyobb

- keresztnév

- a későbbiekben

- indított

- Törvény

- vezetékek

- tanulás

- legkevésbé

- Led

- kevesebb

- mint

- LIMIT

- hosszabb

- néz

- alacsonyabb

- gép

- gépi tanulás

- készült

- Fő

- fontos

- Makers

- sok

- piacára

- Marketing

- tömeges

- említ

- minimalizálása

- ML

- Monolitikus

- több

- a legtöbb

- többnyire

- mozog

- áthelyezve

- többszörös

- Szükség

- igények

- Új

- Új technológiák

- újabb

- NIH

- nem

- csomópontok

- Most

- szám

- számos

- of

- ajánlat

- felajánlás

- on

- ONE

- csak

- Vélemények

- opció

- or

- szervezet

- Egyéb

- tulajdonos

- csomag

- csomagolás

- Papír

- rész

- teljesítmény

- előadó

- fázis

- phd

- PHP

- szedés

- képek

- Plató

- Platón adatintelligencia

- PlatoData

- játszani

- játszott

- plusz

- pont

- helymeghatározás

- állás

- Bekapcsolom

- pontosan

- előre

- előrejelzés

- előnyben részesített

- folyamat

- feldolgozott

- feldolgozás

- Processzor

- Termelés

- Termékek

- protokoll

- szolgáltatók

- kérdés

- gyorsabb

- gyorsan

- gyors

- Arány

- Az árak

- elérése

- Olvass

- miatt

- újratervezés

- újratervezett

- összefüggő

- emlékeztető

- megköveteli,

- REST

- Kritika

- felülvizsgálata

- Forradalom

- jobb

- Szerep

- azonos

- lát

- látás

- Úgy tűnik,

- részes

- szegmensek

- válasszuk

- félvezető

- szerverek

- szolgáló

- számos

- mutatott

- jelentős

- jelentősen

- Szilícium

- hasonló

- egyetlen

- Méret

- kisebb

- okostelefon

- megoldások

- SOLVE

- néhány

- Nemsokára

- Hely

- specifikációk

- sebesség

- Szponzorált

- standard

- szabványok

- meghatározott

- bot

- Még mindig

- struktúra

- siker

- sikeres

- rendszer

- Systems

- cél

- technikák

- Technologies

- Technológia

- szöveg

- mint

- köszönöm

- hogy

- A

- azok

- Őket

- elmélet

- Ezek

- ezt

- azok

- Keresztül

- időkeret

- nak nek

- szerszámok

- felső

- borzasztó

- tsmc

- kettő

- típus

- sajnálatos módon

- Egyetemes

- frissítése

- us

- használ

- használt

- segítségével

- különféle

- gyártók

- keresztül

- volt

- Út..

- we

- voltak

- Mit

- amikor

- míg

- fehér

- fehér papír

- miért

- lesz

- val vel

- Munka

- lenne

- év

- év

- Hozam

- te

- zephyrnet