IEDM 2023 -tapahtumassa Naoto Horiguchi esitteli CFET:istä ja Middle of Line -integraatiosta. Minulla oli tilaisuus puhua Naoton kanssa tästä työstä ja tämä kirjoitus perustuu hänen esitykseensä IEDM:ssä ja jatkokeskusteluomme. Nautin aina puhumisesta Naoton kanssa, hän on yksi logiikkateknologian kehittämisen johtajista, selittää tekniikan helposti ymmärrettävällä tavalla ja on herkkä ja helppo työskennellä.

Miksi tarvitsemme CFETiä

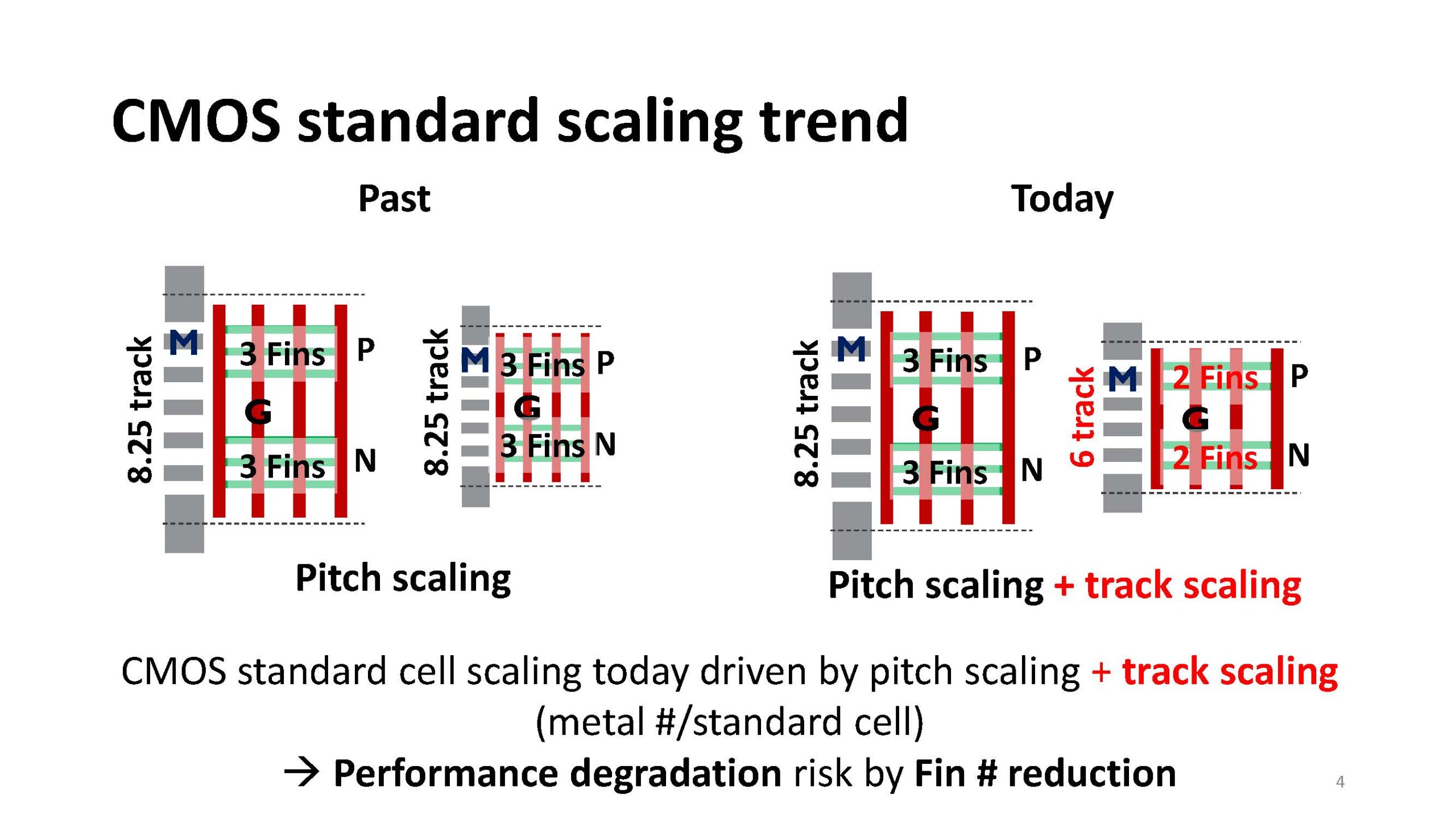

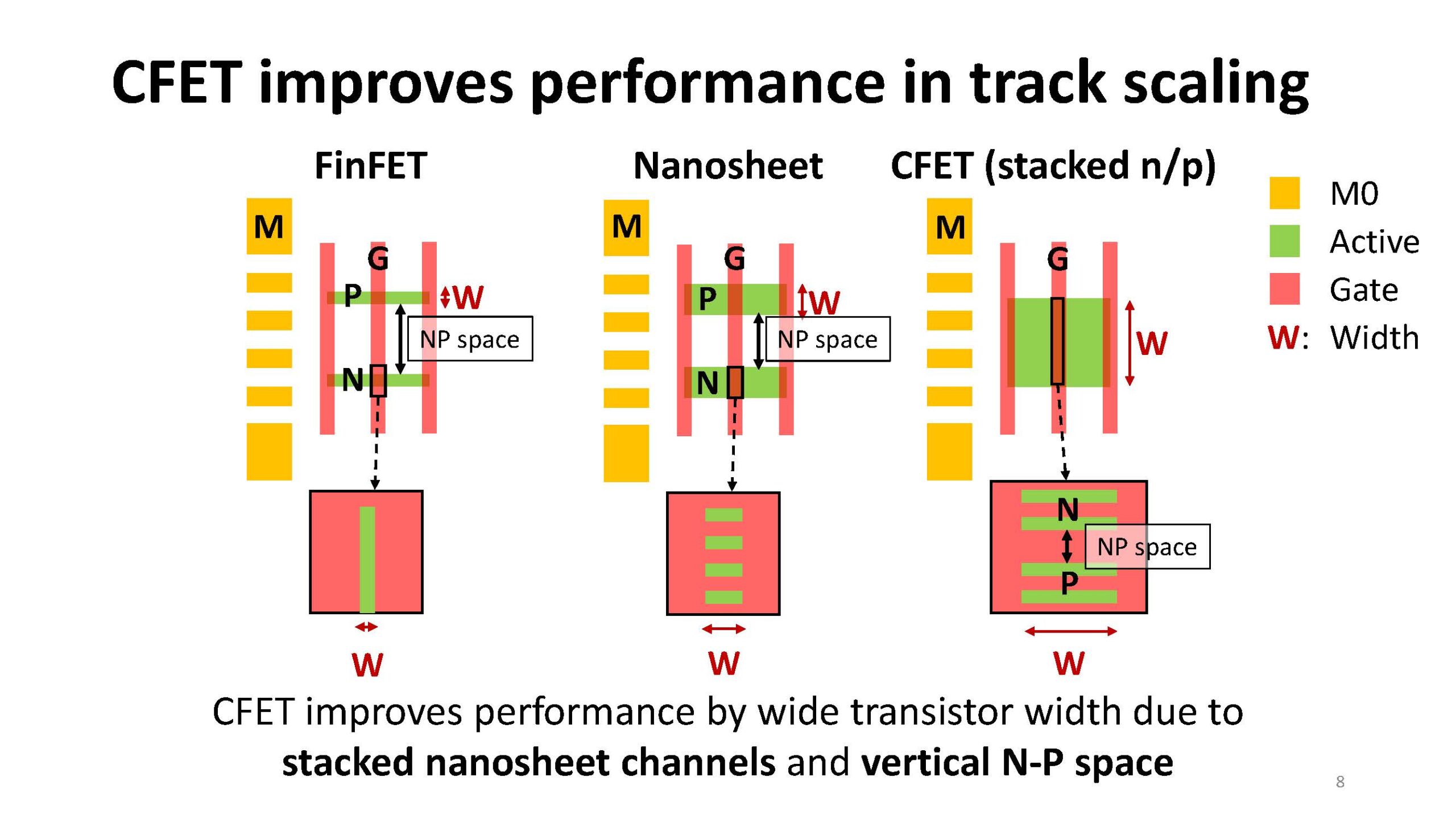

Koska CMOS-skaalaus on siirtynyt puhtaasti sävelkorkeuspohjaisesta skaalauksesta sävelkorkeuteen ja raitapohjaiseen skaalaukseen, eväpopulaatio on tullut tarpeelliseksi, katso kuva 1. Aina kun vähennät evien määrää, suorituskyky heikkenee.

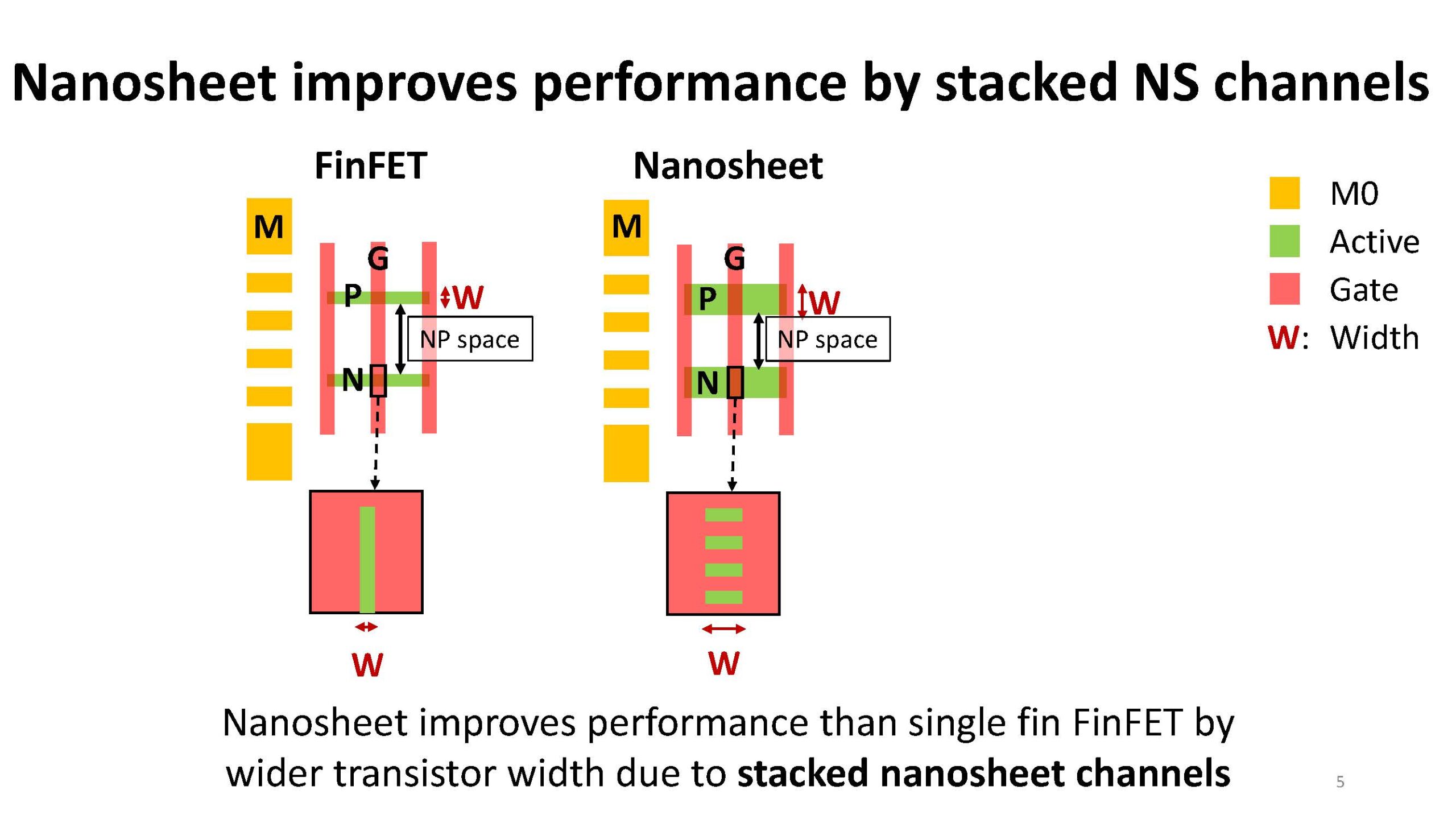

Siirtymällä FinFEtsistä pinottuihin HHorizontal NanoSheets (HNS) -suorituskykyä voidaan parantaa/palauttaa leveämmillä nanoarkkipinoilla ja pinoamalla useita nanoarkkeja pystysuoraan, katso kuva 2.

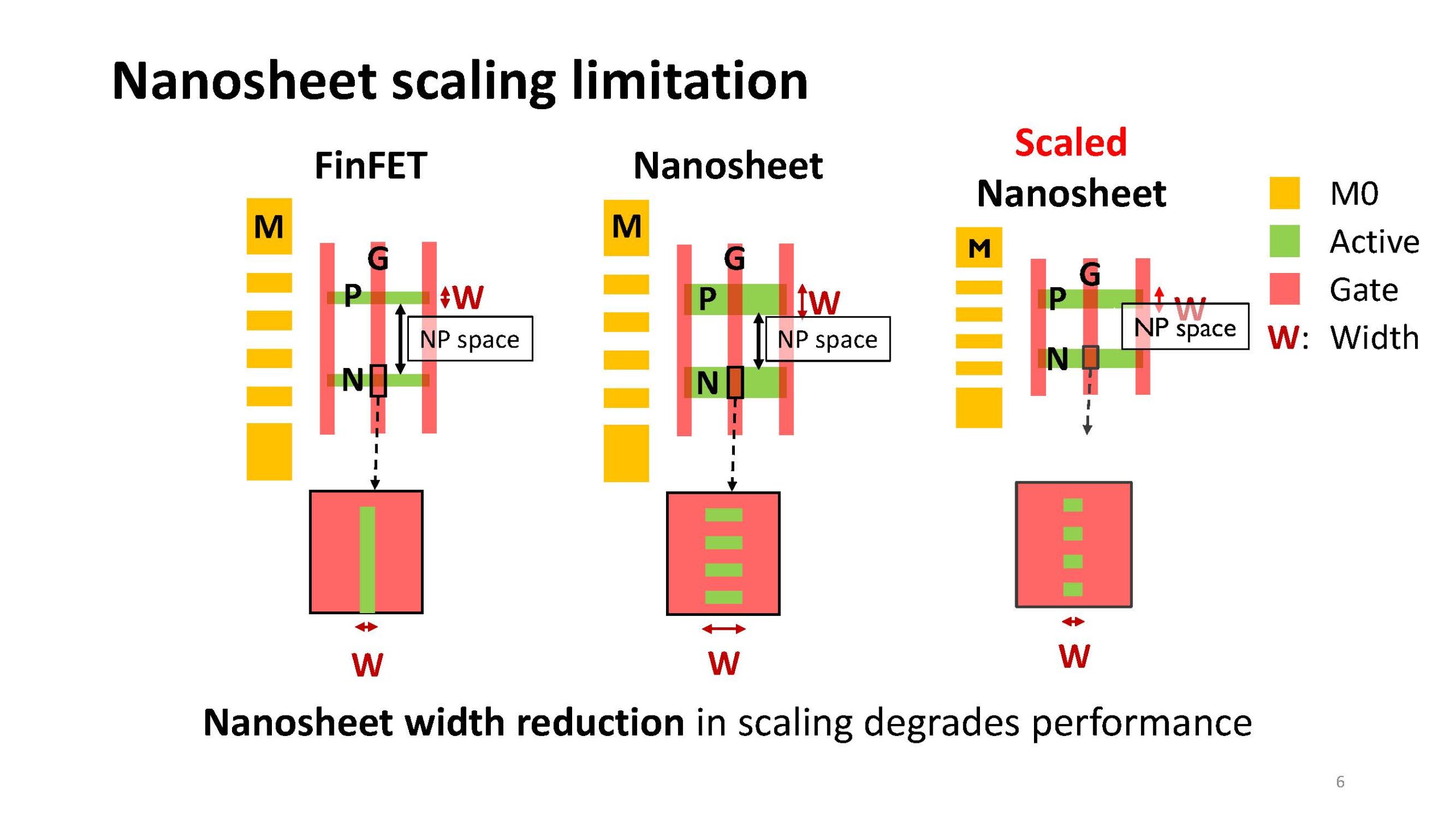

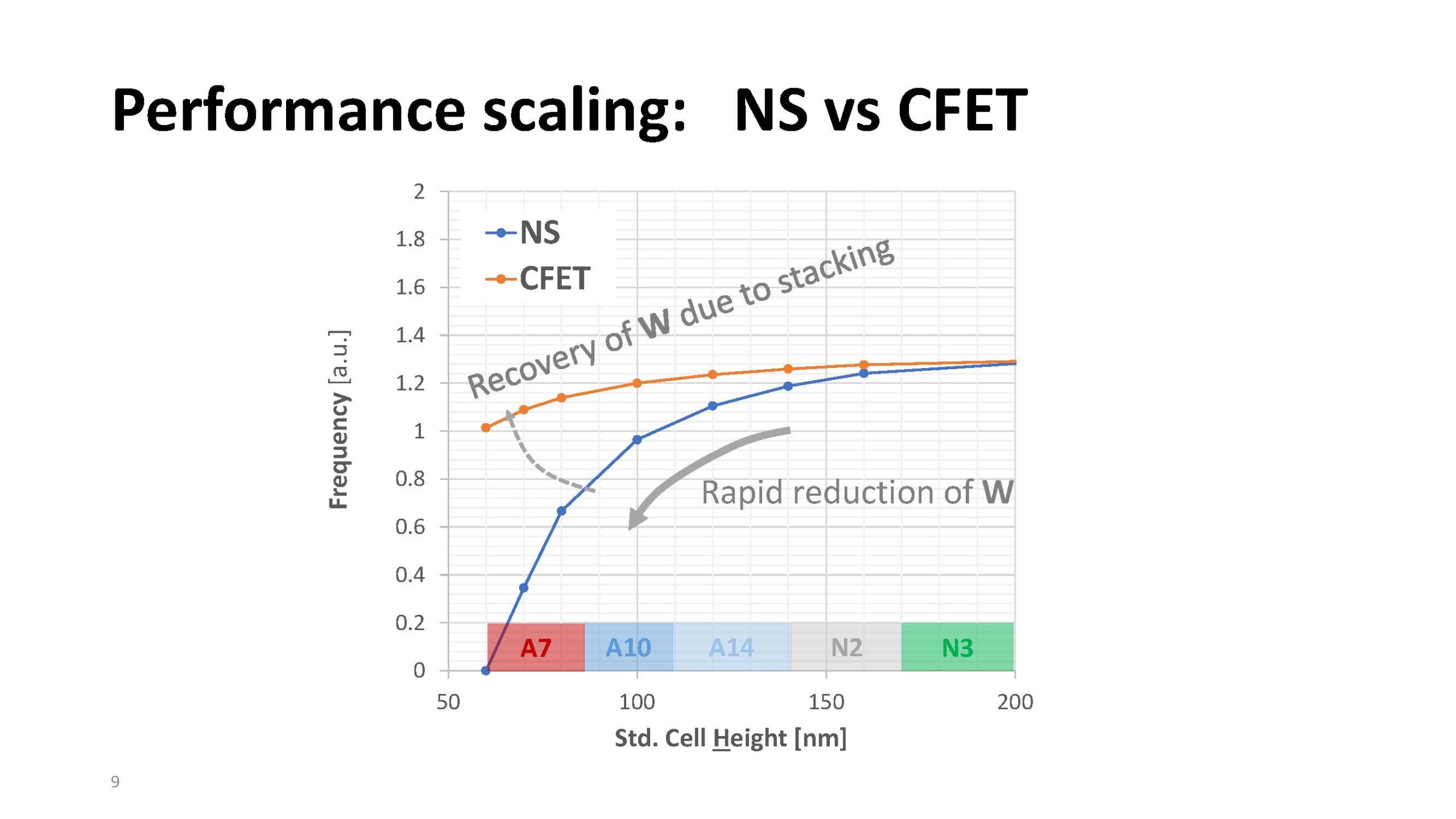

Mutta kuten olemme nähneet FinFETin nanoarkkien skaalaus johtaa lopulta suorituskyvyn heikkenemiseen, katso kuva 3.

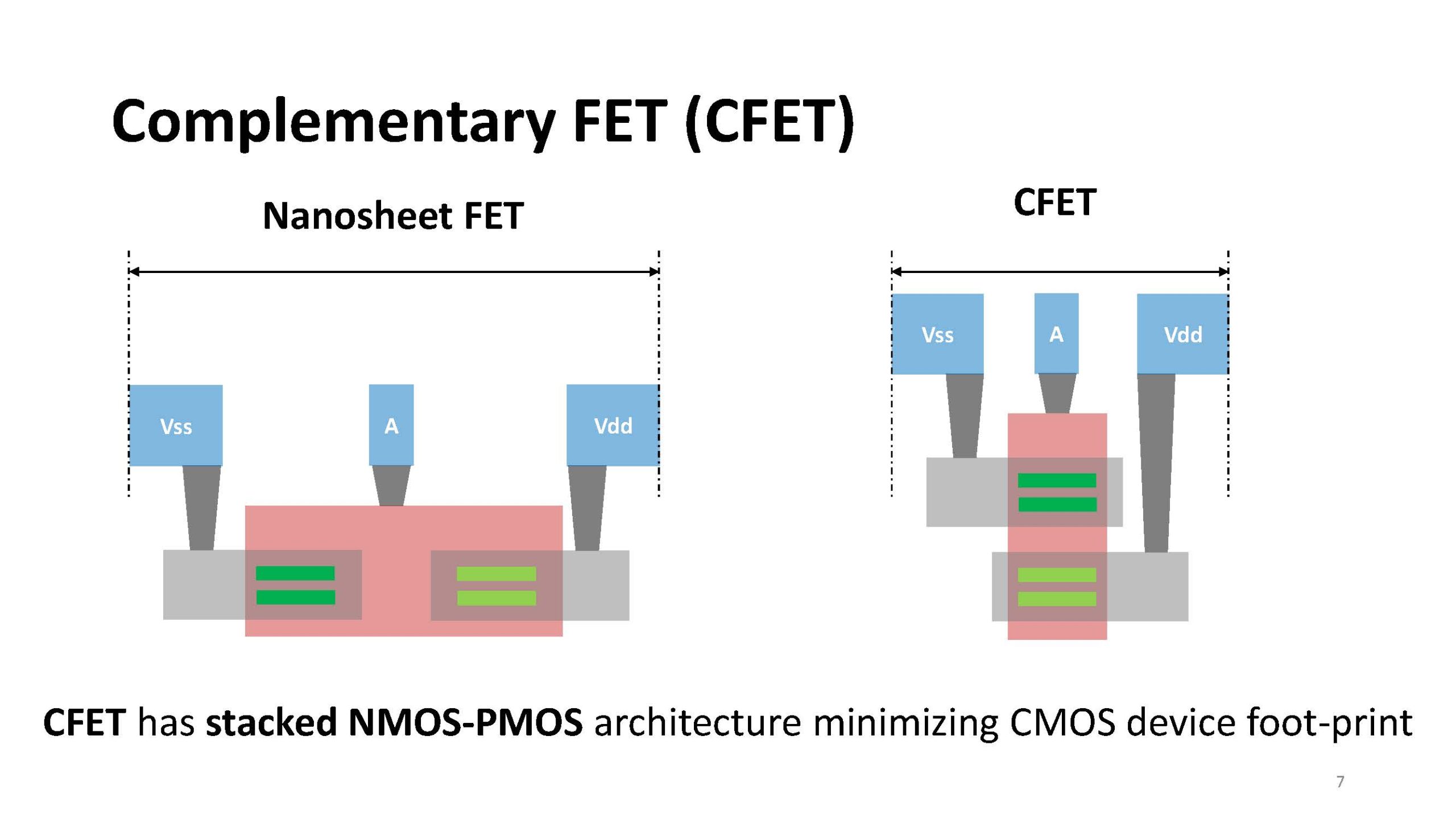

CFET:t (Complementary FET) pinoavat nFET:n ja pFETin, katso kuva 4.

CFETit nollaavat jälleen skaalausrajoitukset, koska nFET ja pFET pinotaan ja laitteiden välinen np-etäisyys muuttuu pystysuoraksi vaakasuuntaisen sijaan, mikä mahdollistaa leveämmät arkit, katso kuva 5.

Kuva 6 esittää HNS- ja CFET-suorituskyvyn vertailun solun korkeuteen, mikä korostaa CFET:n etua.

Monoliittinen vs. peräkkäinen CFET

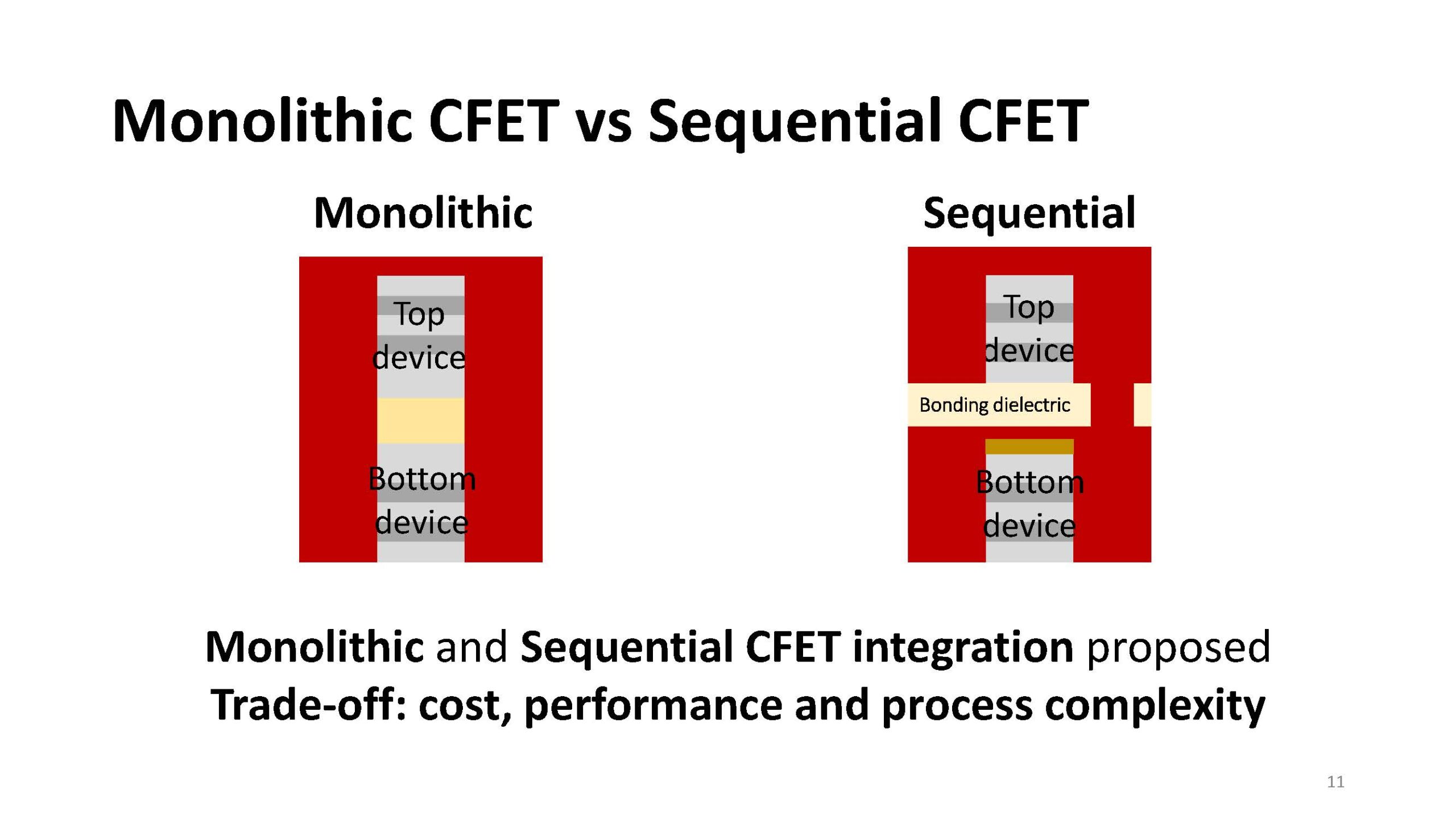

CFET-valmistukseen on olemassa kaksi pohjimmiltaan erilaista lähestymistapaa. Monoliittinen virtaus CFETit valmistetaan kiekolle jatkuvassa prosessivirtauksessa. Peräkkäisessä virtauksessa pohjalaite valmistetaan yhdelle kiekolle, sitten toinen kiekko liitetään ensimmäiseen kiekkoon ja ylälaite valmistetaan toiseen kiekkoon.

Jaksottaisessa virtauksessa kahden laitteen välillä on sidosdielektri, katso kuva 7.

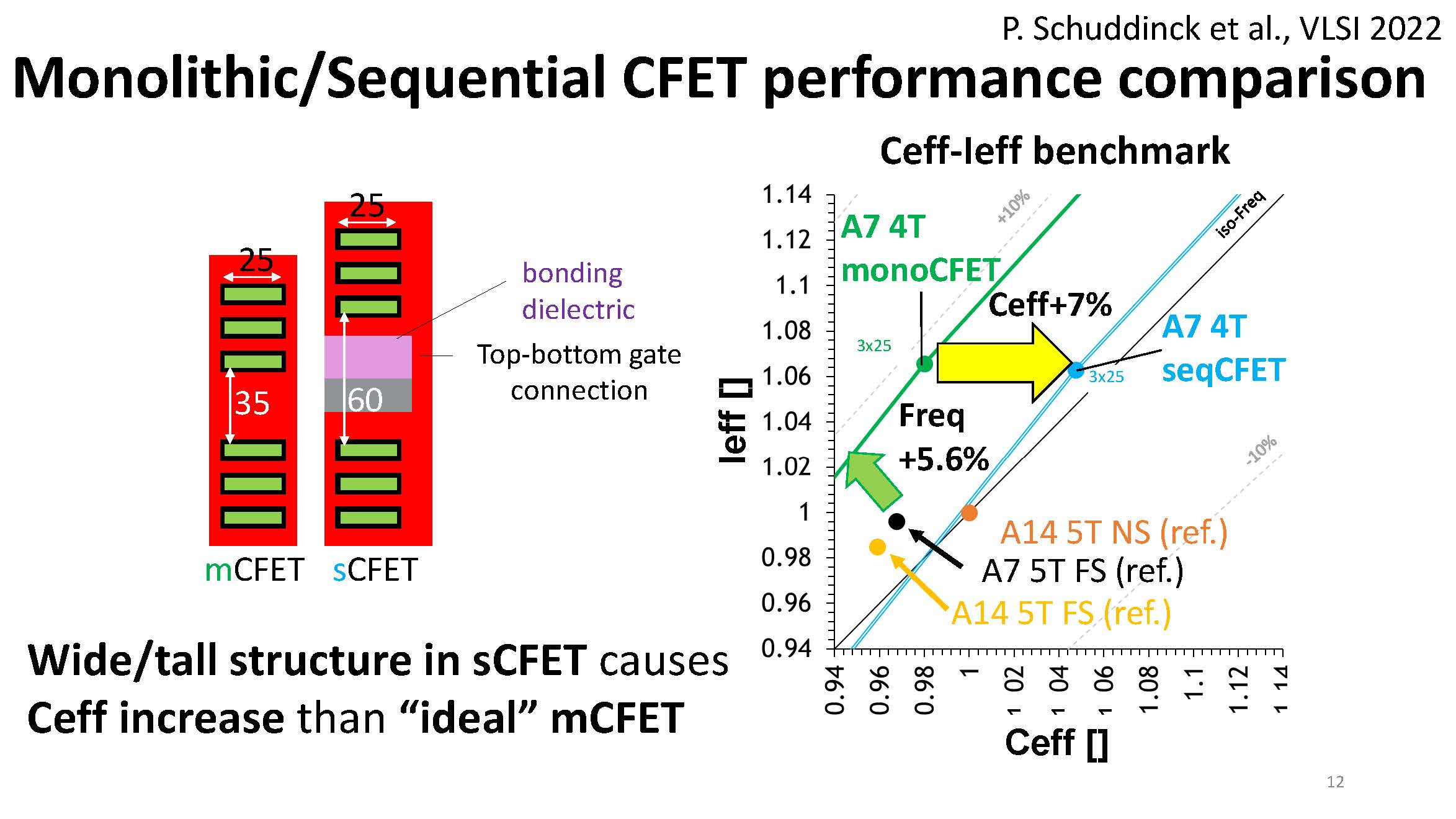

Liimauseristeen ansiosta rakenne on korkeampi ja sen kapasitanssia heikentävä suorituskyky on suurempi, katso kuva 8.

Peräkkäiset CFET:t ovat kalliimpia valmistaa kuin monoliittiset CFET:t, ja sen ja suorituskyvyn heikkenemisen välillä näyttää siltä, että teollisuus keskittyy monoliittisiin CFET:eihin.

Monoliittinen CFET-käsittely

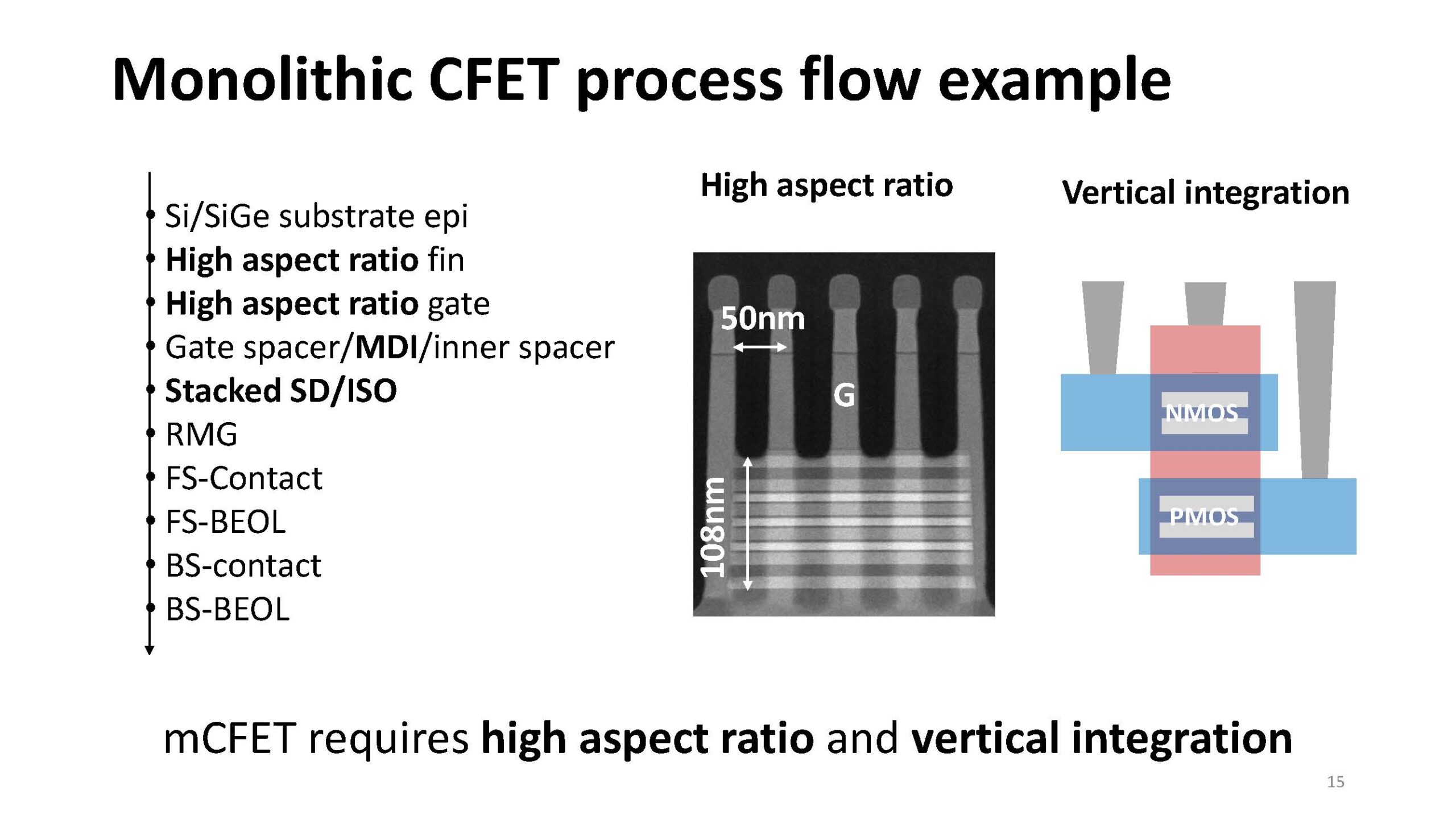

Monoliittinen CFET-prosessi on kuvattu kuvassa 9.

Lihavoidut vaiheet ovat erityisen haastavia:

- Vaakasuuntaisilla nanoarkkipinoilla (rivat) on jo korkea kuvasuhde, joten CFET:n tekemiseksi pinot nFET- ja pFET-pinot päällekkäin suhteellisen paksulla kerroksella, joka yli kaksinkertaistaa korkeuden.

- Portin muodostuksella on myös korkea kuvasuhde, kuten edellisessä kohdassa kuvattiin.

- Epitaksiaaliset lähde/viemärit on eristettävä pystysuunnassa toisistaan.

- Ei nimenomaisesti kutsuttu, alin laitteen lähde/viemäri valmistetaan ja sitten ylemmän laitteen ylempi lähde/viemäri valmistetaan. Ylälaitteen lämpökäsittely ja sitä seuraavat vaiheet on suoritettava riittävän alhaisissa lämpötiloissa, jotta pohjalaite ei heikkene.

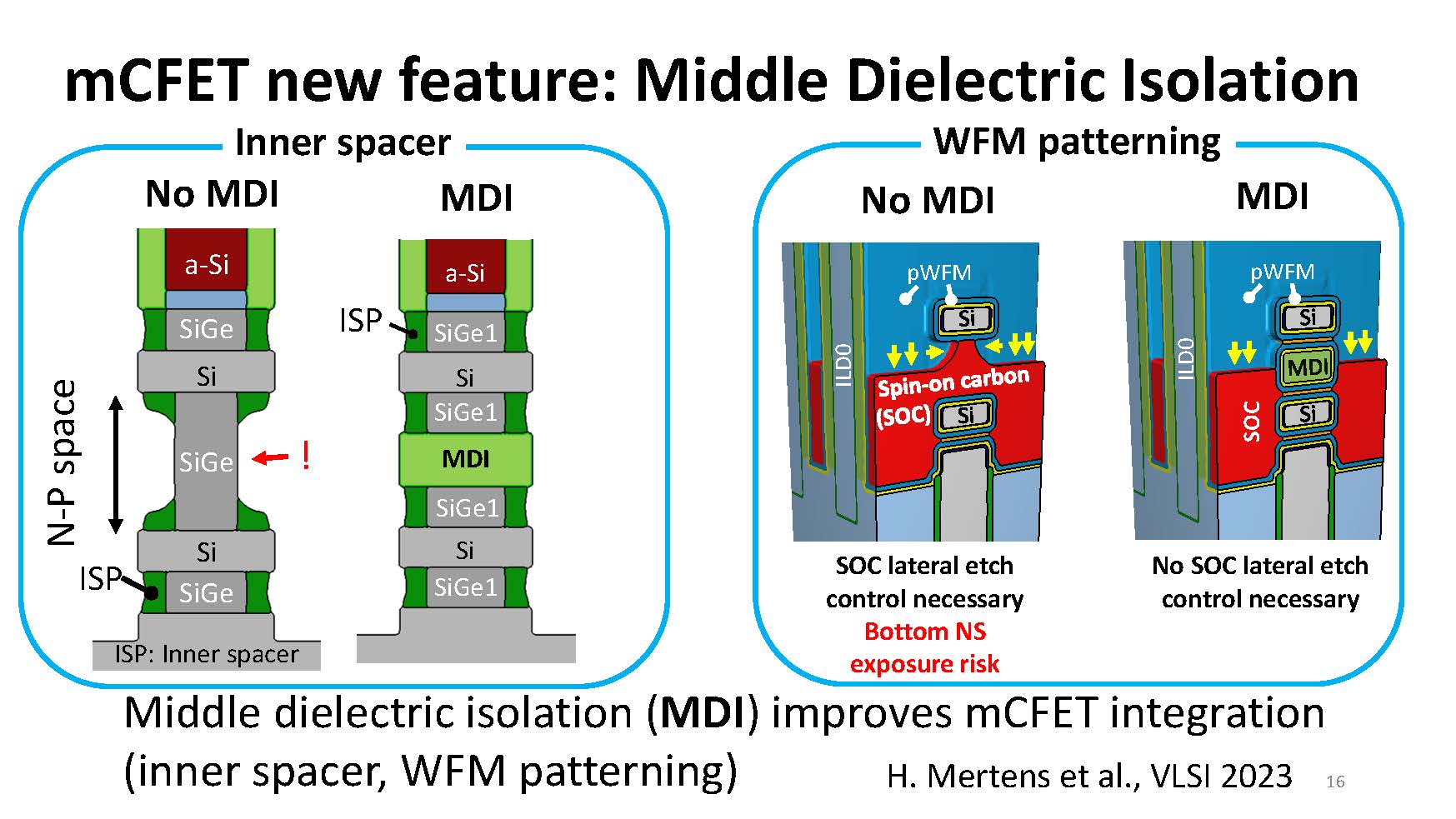

Yksi erityisen mielenkiintoinen osa tätä esitystä oli Middle Dilectric Isolation (MDI) -osa, en ollut nähnyt tätä ongelmaa aiemmin. MDI todistaa sisäisen välikappaleen ja Work Function Material (WFM) -kuvioinnin.

Kuva 10 havainnollistaa MDI-vaikutusta sisemmän välikkeen muodostukseen (vasen puoli) ja WFM-kuviointiin (oikea puoli).

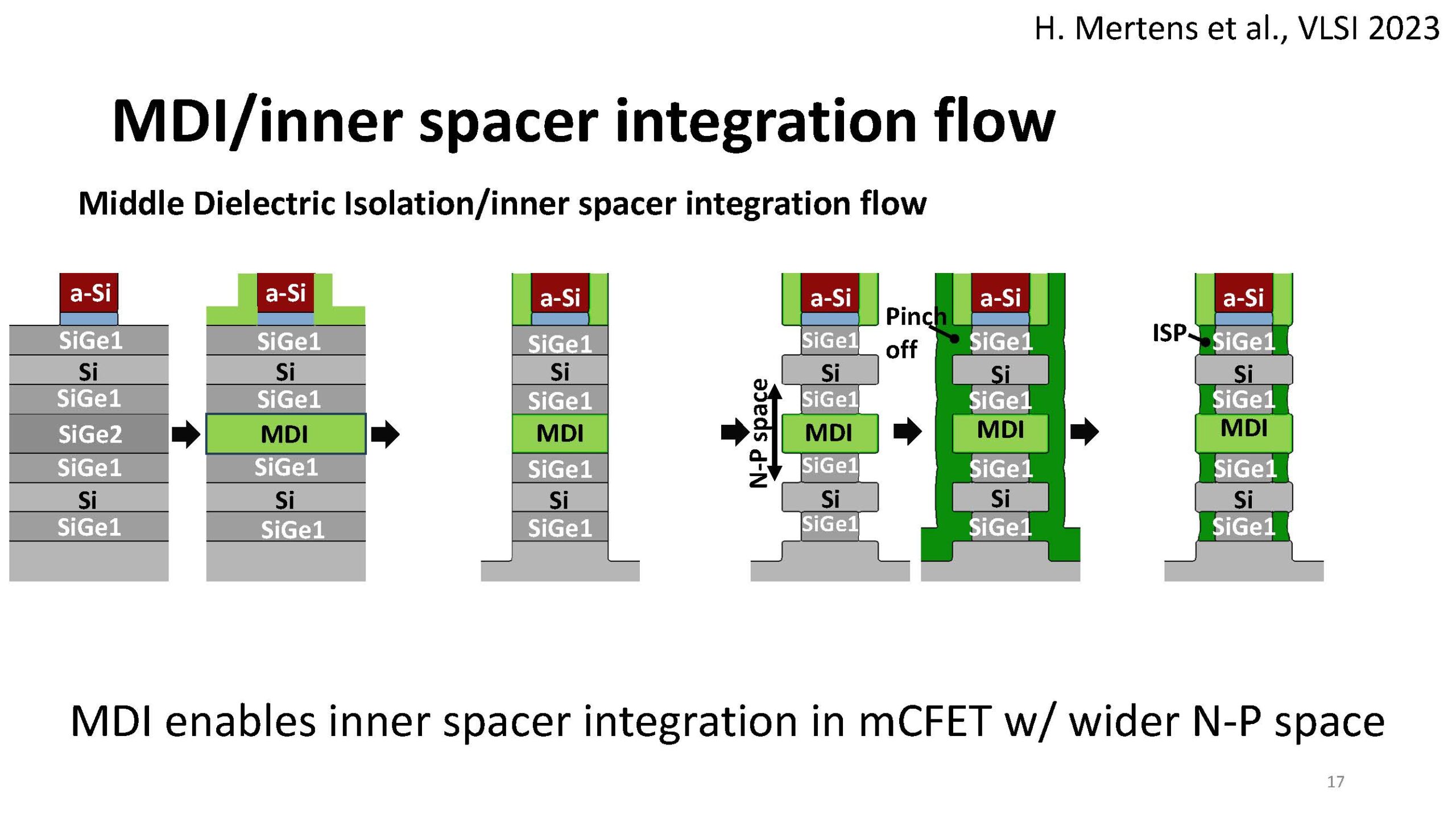

Kuva 11 esittää MDI-integrointivuon.

Integroimalla MDI pystysuoraa etäisyyttä nFET:n ja pFET:n välillä voidaan kasvattaa vaikuttamatta sisäiseen välikappaleen muodostukseen.

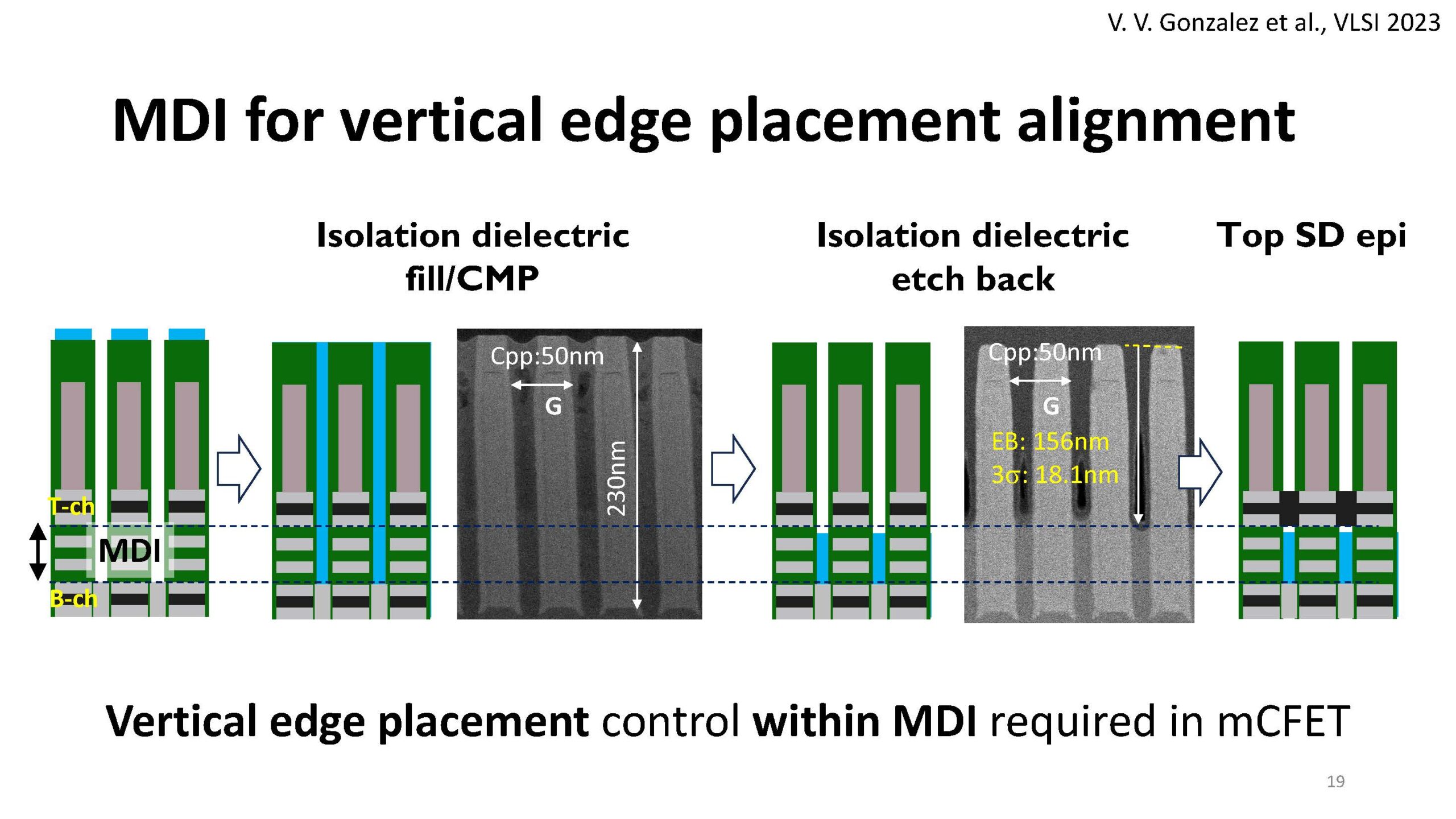

Kuten aiemmin mainittiin, alin laitteen lähde/viemäri valmistetaan ja sitten ylempi laitteen lähde/viemäri. Pohjalähteen/viemärin muodostuksen jälkeen eristysdielektri kerrostetaan ja syövytetään takaisin ylälaitteen paljastamiseksi lähde/viemärin epitaksiaalista muodostumista varten. Eristesyövytystä on ohjattava MDI-korkeudella, katso kuva 12.

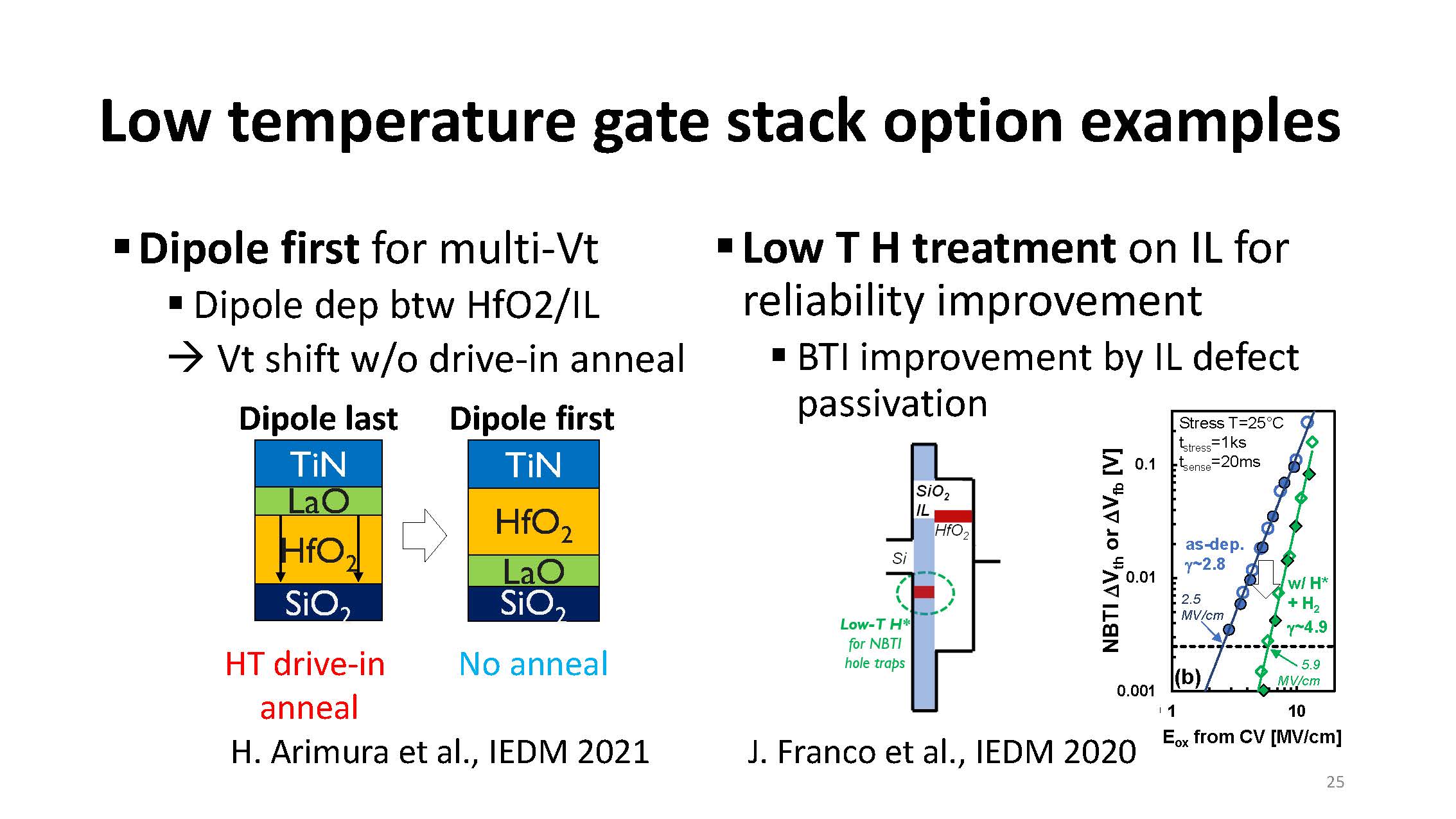

Laitteen suorituskyvyn termisen heikkenemisen minimoimiseksi uusia WFM-vaihtoehtoja, joissa on dipoliensimmäinen käsittely, eikä hehkutusta ja matalan lämpötilan kerrosten välisiä muodostusprosesseja tarvita, katso kuva 13.

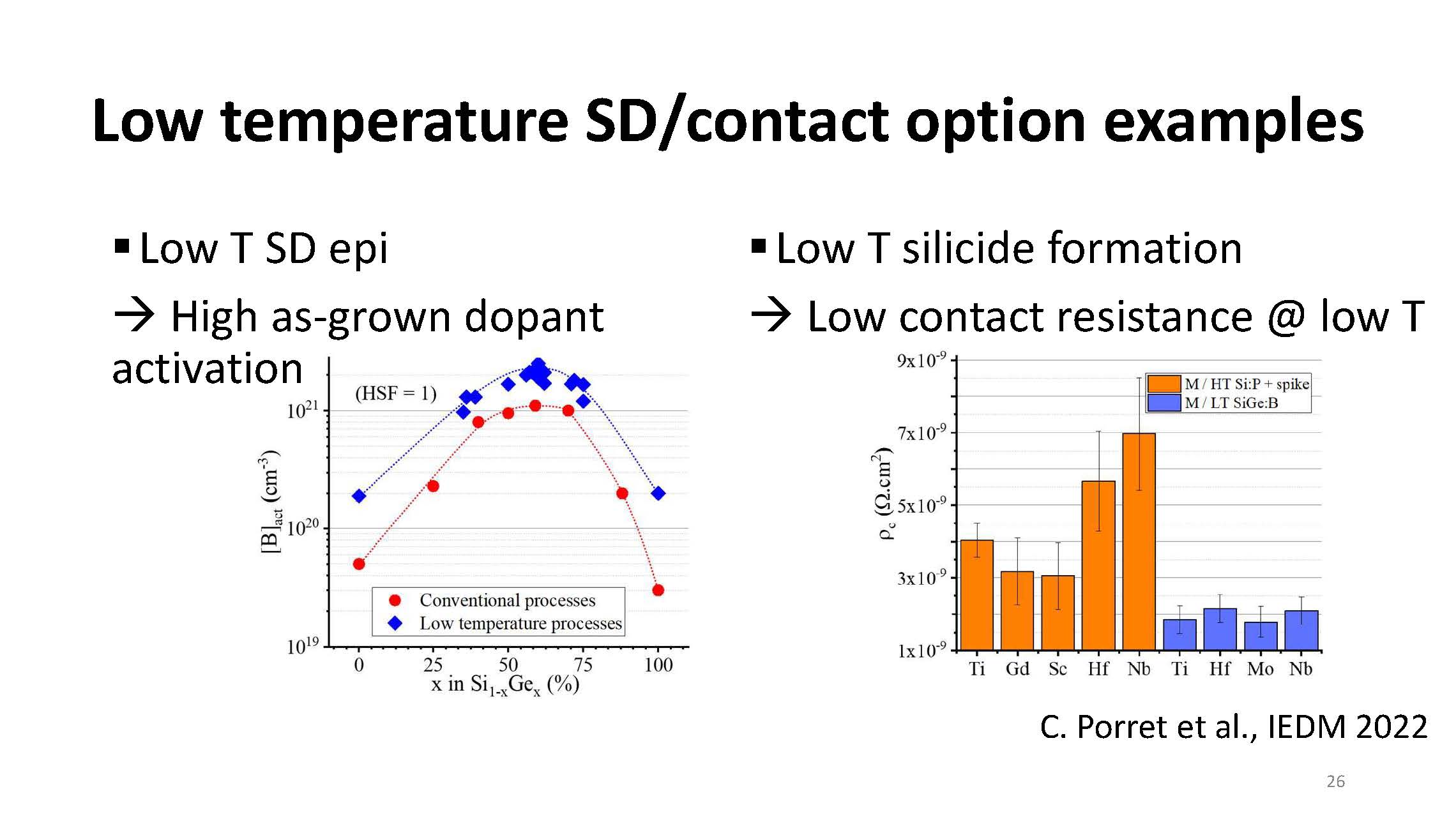

Tarvitaan myös matalan lämpötilan lähde/viemäröinti ja matalan lämpötilan silisidit kontaktin muodostukseen, katso kuva 14.

Matalan lämpötilan silisidi on erityisen tärkeä takapuolen suorassa kosketuksessa pohjalaitteeseen. CFET-yhdysliitäntä vaatii koskettimet ala- ja ylälaitteeseen, ja takapuolen virransyötön myötä ylälaitteeseen otetaan yhteyttä etupuolen liitäntäpinosta ja alalaitteeseen takapuolelta. Molybdeeni (Mo) ja niobium (Nb) ovat lupaavia pFET:lle ja Scandium (Sc) lupaavia nFET:lle, vaikka Sc:tä on vaikea tallettaa ALD:n kanssa.

Takapuolen ja keskilinjan liitäntä

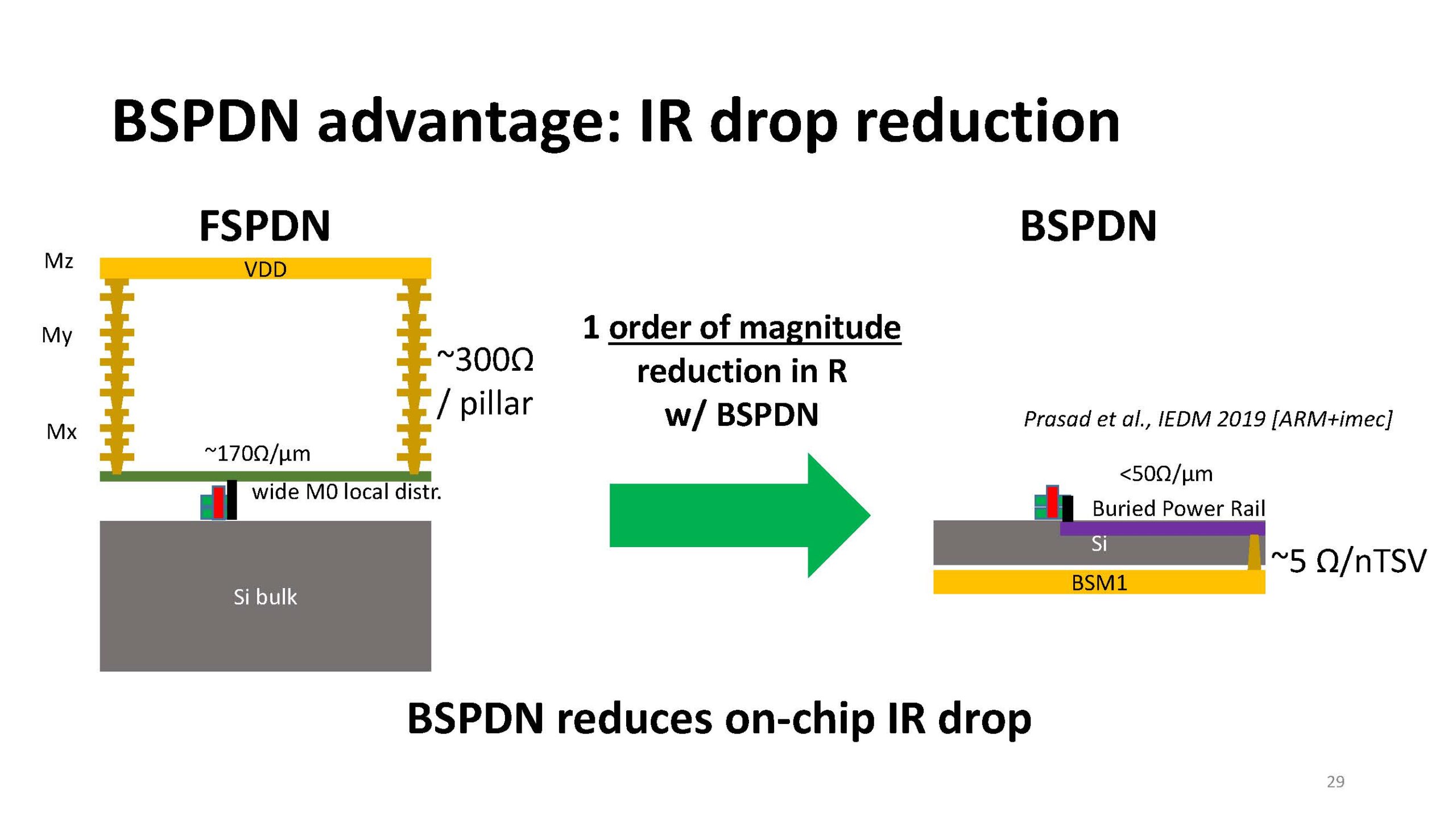

Kuten olen aiemmin kirjoittanut tätä Intelin ja Samsungin ja TSMC:n odotetaan ottavan tänä vuonna käyttöön Back Side Power Delivery Networkin (BSPDN) vuonna 2026. Yhteenliittämisen jakaminen etupuolen signaaliliitäntöihin ja takapuolen virtaliitäntöihin vähentää IR-häviötä (tehohäviö) suuruusluokkaa, katso kuva 15.

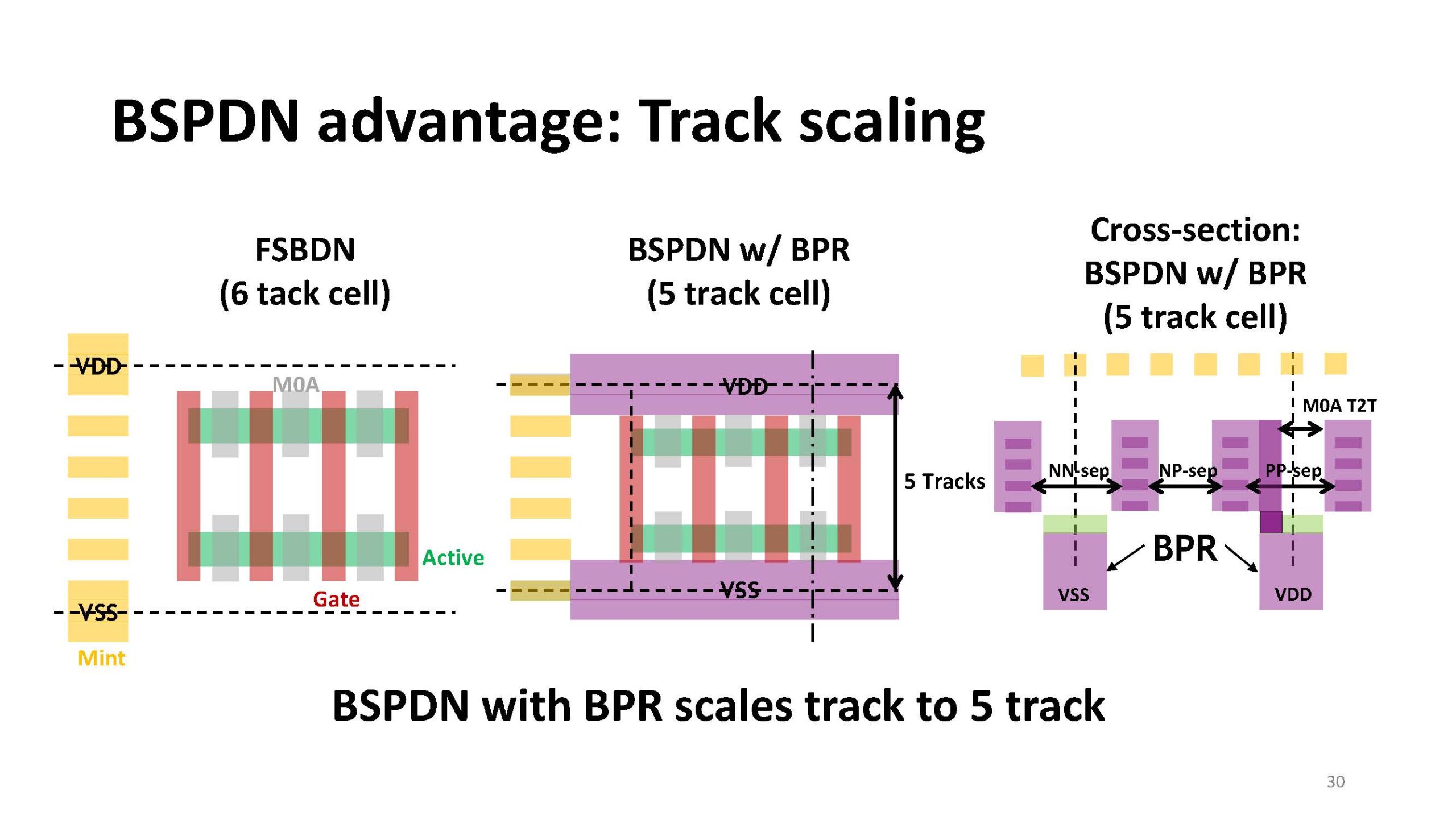

BSPDN parantaa myös raidan skaalausta tukemalla pienentämistä 6-raitaisesta solusta 5-raitaiseen soluun, katso kuva 16.

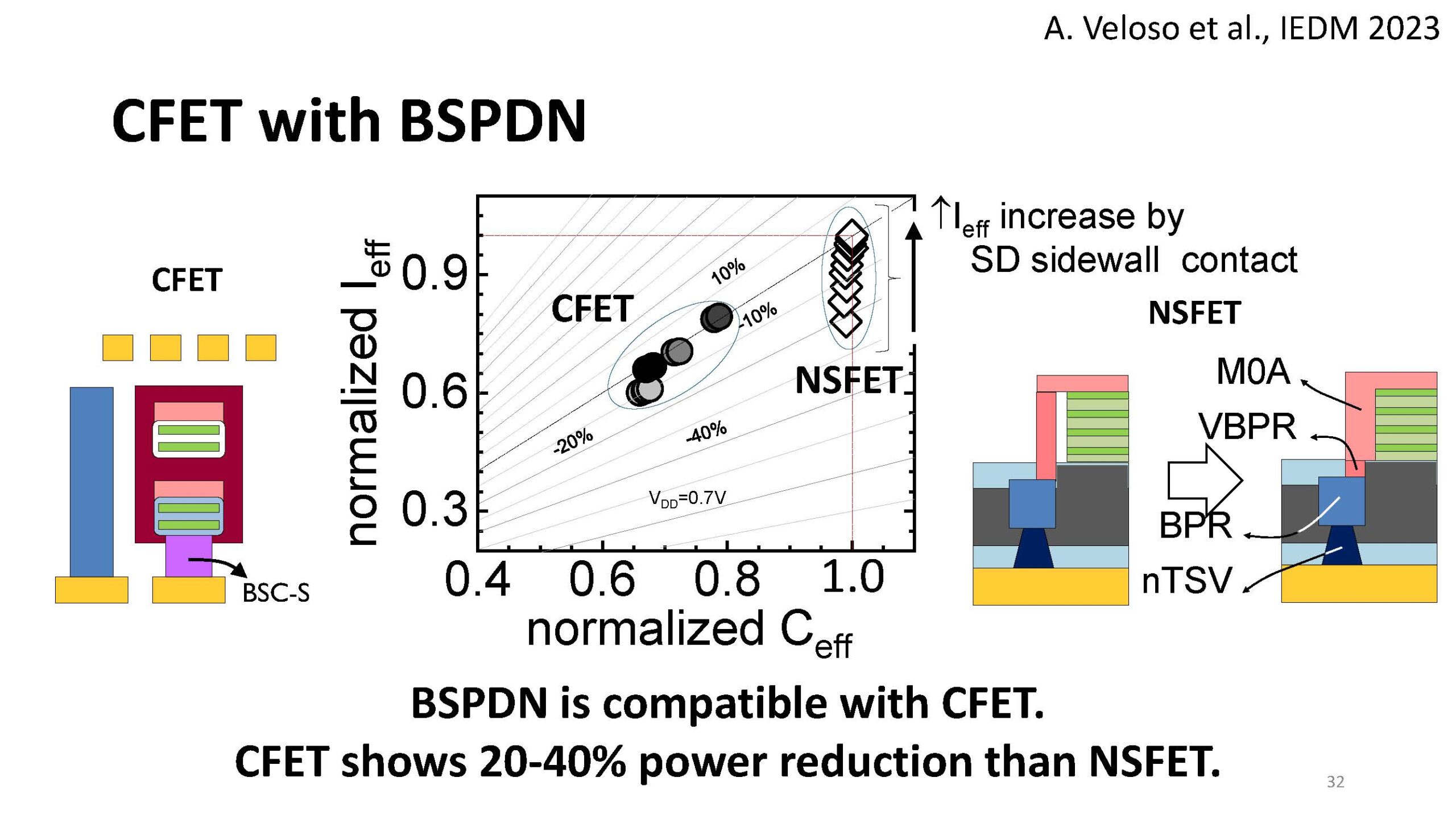

BSPDN:n integrointi CFET:n kanssa voi vähentää tehoa 20–40 % verrattuna Horizontal Stacked NanoSheets (HNS) -taulukkoon, katso kuva 17.

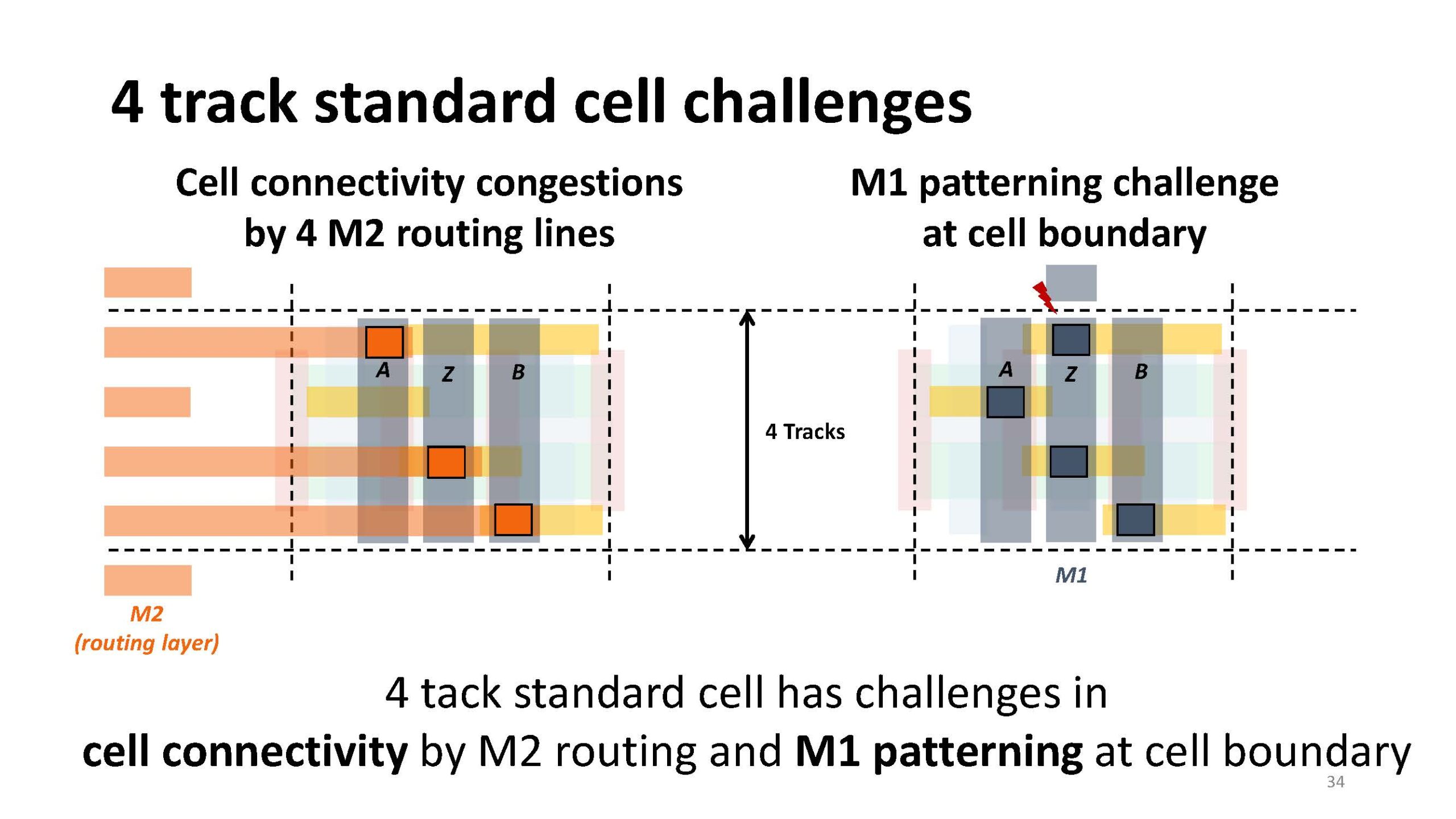

Jotta voidaan siirtyä 5-raitaisen solun lisäksi 4-raitaisen solun yhdistämiseen, on voitettava haasteet, katso kuva 18.

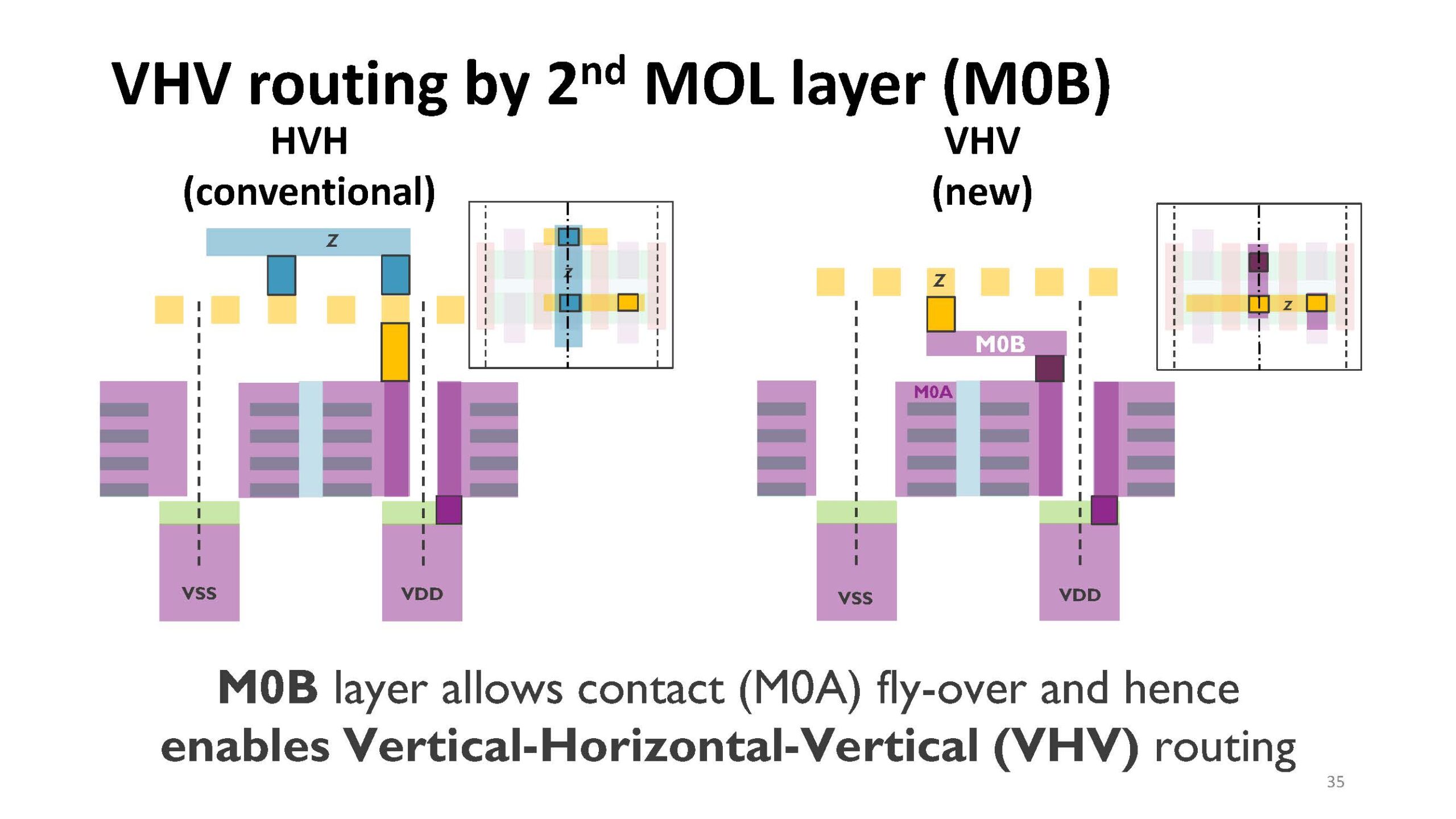

Pysty-vaaka-pystyasettelu ylimääräisillä Middle of Line (MOL) -tasoilla voi ottaa käyttöön 4-raitaiset solut, katso kuva 19.

Olen aiemmin kirjoittanut Imecin työstä tällä alalla tätä joten en toista näitä tietoja.

Kysyin Naotolta, mitä tarvitsisi siirtyä 4-raiteisen solun lisäksi 3-raitaiseen soluun, hän vastasi, että Imec työskentelee parhaillaan optimoinnin parissa, että se saattaa vaatia MOL-kerrosten lisäämistä ja mahdollisesti ylhäältä alas -liitännän viereen. laite, joka vaikuttaisi normaaliin soluasetteluun.

Kysyin myös Naotolta, milloin hän ajatteli, että saatamme nähdä CFET:t toteutettuina, ja hän sanoi, että mahdollisesti A10-logiikkasukupolvi tai A7-sukupolvi.

Kirjoittajat huomauttavat, että Intel, Samsung ja TSMC julkaisivat kaikki CFET-työt IEDM:ssä tänä vuonna, ja sekä Intelillä että TSMC:llä on teknologiavaihtoehtokartat, joissa FinFETit väistyvät HNS:lle ja sitten CFET:ille.

Yhteenveto

Imec osoittaa edelleen erinomaista edistystä CFET:ien kehittämisessä seuraavan sukupolven vaihtoehtona HNS:n jälkeen. Tässä työssä on kuvattu laiteintegraatiovaihtoehdot sekä BSPDN- ja MOL-vaihtoehdot.

Lue myös:

IEDM 2023 – 300 mm:n kiekkokankaan hiilipäästöjen mallinnus

SMIC N+2 Huawei Mate Pro 60:ssä

ASML-päivitys SEMICON West 2023

Jaa tämä viesti:

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiwiki.com/semiconductor-services/340811-iedm-2023-imec-cfet/

- :on

- :On

- :ei

- $ YLÖS

- 06

- 07

- 08

- 09

- 1

- 10

- 11

- 12

- 13

- 14

- 15%

- 16

- 17

- 19

- 2023

- 2026

- 25

- 26

- 29

- 30

- 32

- 35%

- 7

- 8

- 9

- a

- Meistä

- Lisäksi

- lisä-

- Etu

- tulo

- Jälkeen

- uudelleen

- Kaikki

- jo

- Myös

- Vaikka

- aina

- an

- ja

- näyttää

- lähestymistavat

- OVAT

- ALUE

- AS

- ulkomuoto

- At

- takaisin

- perustua

- BE

- koska

- tulevat

- tulee

- ollut

- ennen

- välillä

- Jälkeen

- tappi

- sekä

- pohja

- by

- soittaa

- nimeltään

- CAN

- hiili

- solu

- Solut

- haasteet

- haastava

- mahdollisuus

- vertailu

- täydentävä

- liitäntä

- Liitännät

- rajoitteet

- ottaa yhteyttä

- Yhteydet

- jatkuu

- jatkuva

- hallinnassa

- toimitus

- tallettaa

- talletettu

- on kuvattu

- Kehitys

- laite

- Laitteet

- eri

- ohjata

- keskustelu

- do

- tehty

- kaksinkertaistui

- Pudota

- kukin

- helppo

- reuna

- vaikutus

- mahdollistaa

- mahdollistaa

- nauttia

- tarpeeksi

- lopulta

- erinomainen

- odotettu

- kallis

- selittää

- nimenomaisesti

- FET

- Kuva

- evä

- lopullinen

- FINE

- Etunimi

- virtaus

- keskityttiin

- seurata

- varten

- muodostus

- alkaen

- etuosa

- toiminto

- pohjimmiltaan

- portti

- sukupolvi

- Antaminen

- Go

- Kasvu

- HAD

- Kova

- Olla

- he

- korkeus

- Korkea

- korkeampi

- korostus

- hänen

- Vaakasuora

- HTTPS

- Huawei

- i

- havainnollistaa

- Vaikutus

- vaikuttavia

- täytäntöön

- tärkeä

- parani

- parantaa

- in

- kasvoi

- teollisuus

- tiedot

- sisempi

- sen sijaan

- Integrointi

- integraatio

- Intel

- mielenkiintoinen

- tulee

- esitellä

- yksittäinen

- eristäminen

- kysymys

- IT

- jpg

- kerros

- kerrokset

- Layout

- johtajat

- Liidit

- vasemmalle

- linja

- logiikka

- pois

- Matala

- tehdä

- Kartat

- perämies

- materiaali

- max-width

- Saattaa..

- mainitsi

- Keskimmäinen

- ehkä

- minimoida

- mallintaminen

- MOL

- yhtenäinen

- lisää

- liikkuvat

- moninkertainen

- täytyy

- välttämätön

- Tarve

- tarvitaan

- verkko

- Uusi

- seuraava

- Nro

- huomata

- nyt

- numero

- of

- on

- kerran

- ONE

- optimointi

- Vaihtoehto

- Vaihtoehdot

- or

- tilata

- Muut

- meidän

- ulos

- Voittaa

- sivulla

- osa

- erityisesti

- suorituskyky

- Piki

- sijoitus

- Platon

- Platonin tietotieto

- PlatonData

- plus

- Kohta

- mahdollisesti

- Kirje

- teho

- esittää

- esitys

- esitetty

- lahjat

- edellinen

- aiemmin

- kohti

- prosessi

- Prosessit

- käsittely

- Edistyminen

- lupaava

- osoittautuu

- toimittaa

- julkaistu

- puhtaasti

- suhde

- Lue

- vähentää

- Vähentynyt

- vähentää

- vähentäminen

- suhteellisesti

- toistaa

- edellyttää

- Vaatii

- herkkä

- oikein

- reititys

- Said

- Samsung

- SC

- skaalaus

- Toinen

- nähdä

- nähneet

- näyttää

- näyttää

- puoli

- signaali

- So

- puhua

- pino

- pinottu

- pinoaminen

- Stacks

- standardi

- Askeleet

- rakenne

- myöhempi

- Tukea

- ottaa

- puhuminen

- Elektroniikka

- Teknologian kehitys

- kuin

- että

- -

- sitten

- lämpö-

- tätä

- Tämä vuosi

- ajatus

- aika

- että

- ylin

- raita

- siirtynyt

- tsmc

- kaksi

- Päivitykset

- Vastaan

- pystysuora

- pystysuoraan

- kautta

- vs

- oli

- Tapa..

- we

- HYVIN

- Länsi

- Mitä

- kun

- laajempi

- tulee

- with

- ilman

- Referenssit

- työskentely

- olisi

- kirjoittaa

- kirjallinen

- vuosi

- te

- zephyrnet