Kun ajattelet "FPGA", mitä tulee mieleen? Massiiviset, kalliit osat, jotka pystyvät pitämään sisällään paljon logiikkaa, mutta kuluttavat myös paljon tehoa. Uudelleenkonfiguroitavat alustat, jotka voivat niellä RTL:n SoC-suunnittelua varten piitestauksessa. Suuret, loisteliaat yritysostot, joissa sijoittajat tekivät tonnia rahaa. Eksoottiset 3D-pakkaukset ja edistyneet liitännät. Mutta luultavasti ei halpa, pieni paketti, pieni pintojen määrä, vähän valmiustilaa, eikö niin? Flex Logixin eFPGA palaa perusasioihin vähätehoisen ohjelmoitavan logiikan osalta, joka kestää alhaisemmat kustannukset, suurempi äänenvoimakkuus ja kokorajoitetut laitteet.

Kaksi ohjelmoitavaa tietä tarjosi valinnan

Uhkalla seurustella itseni, ensimmäinen altistuminen niin kutsutulle FPGA-teknologialle tapahtui, kun Altera toi EPROM-pohjaisen EP1200-perheensä 40-nastaisessa DIP-paketissa 16 MHz:n kellolla, 400 mW:lla aktiiviteholla ja 15 mW valmiustilassa. tehoa. Sen mukana tuli kaavamainen editori ja kirjasto porttimakroja. Suunnittelijat piirtävät logiikkansa, "polttivat" osansa, testasivat sitä, heittivät sen UV-lampun alle ja pyyhkivät sen pois, jos se ei toimi, ja yrittävät uudelleen.

Pian sen jälkeen toisessa laboratoriossamme ilmestyi taulu, jossa oli joitain ensimmäisiä Xilinx FPGA:ita. Nämä olivat RAM-pohjaisia EPROM-pohjaisten sijaan – isompia, nopeampia ja uudelleenohjelmoitavia ilman UV-lampun odottamista tai osan poistamista levyltä. Sisäinen logiikka oli myös monimutkaisempi, kun otettiin käyttöön nopeita kertoimia. Nämä osat eivät voi vain lakaista logiikkaa, vaan niitä voitaisiin käyttää myös mukautetun digitaalisen signaalinkäsittelykyvyn tutkimiseen nopeilla uudelleensuunnittelusykleillä.

Tämä aloitti ohjelmoitavan piin asevarustelun, ja PLD:n (ohjelmoitavan logiikkalaitteen) ja FPGA:n välille kehittyi haarautuminen. Valmistajat tekivät valintoja: Altera ja Xilinx valitsivat FPGA-skaalautuvuuden korkean tien ja Actel, Lattice ja muut valitsivat PLD-joustavuuden alemman tien "liimalogiikkaan" materiaalikustannusten vähentämiseksi.

eFPGA siirtää pienitehoista ohjelmoitavaa logiikkayhtälöä

Kaikki tämä kuulostaa kypsiltä markkinoilta, joiden toisessa päässä on korkea markkinoille pääsyn este ja toisaalta hyödykkeistetty tarjonta. Mutta entä jos ohjelmoitava logiikka olisi IP-lohko, joka voitaisiin suunnitella mihin tahansa siruun tällä satujen aikakaudella – mukaan lukien pieni, vähän tehoa käyttävä FPGA? Tämä kiertäisi esteen (ainakin matalan ja keskitason tarjonnassa) ja kaupallistamisen.

Flex Logix otti haasteen vastaan EFLX 1K eFPGA -laatalla. Jokaisessa logiikkaruudussa on 560 kuuden tulon hakutaulukkoa (LUT), joissa on RAM-muisti, kellotus ja liitäntä. EFLX-laattojen järjestäminen antaa mahdollisuuden käsitellä erilaisia logiikka- ja DSP-rooleja. Mutta sen näkyvimmät ominaisuudet voivat olla sen koko ja virranhallinta.

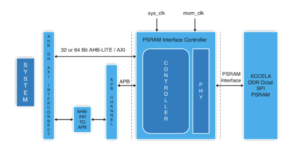

TSMC 40ULP -materiaalista valmistettu EFLX 1K -laatta sopii 1.5 mm:iin2 ja tarjoaa tehoportin syvän unen tiloihin tilan säilyttämisellä – paljon aggressiivisemmin kuin perinteiset PLD:t. EFLX 1K:ssa on myös tuotantovalmiita ominaisuuksia, jotka on lainattu FPGA:sta. Se sisältää AXI- tai JTAG-liitännät bittivirran konfigurointia varten, pehmeän virheentarkistuksen mahdollistavan lukupiirin ja virtaviivaistettujen vektoreiden testitilan, joka parantaa peittoa ja lyhentää testiaikoja.

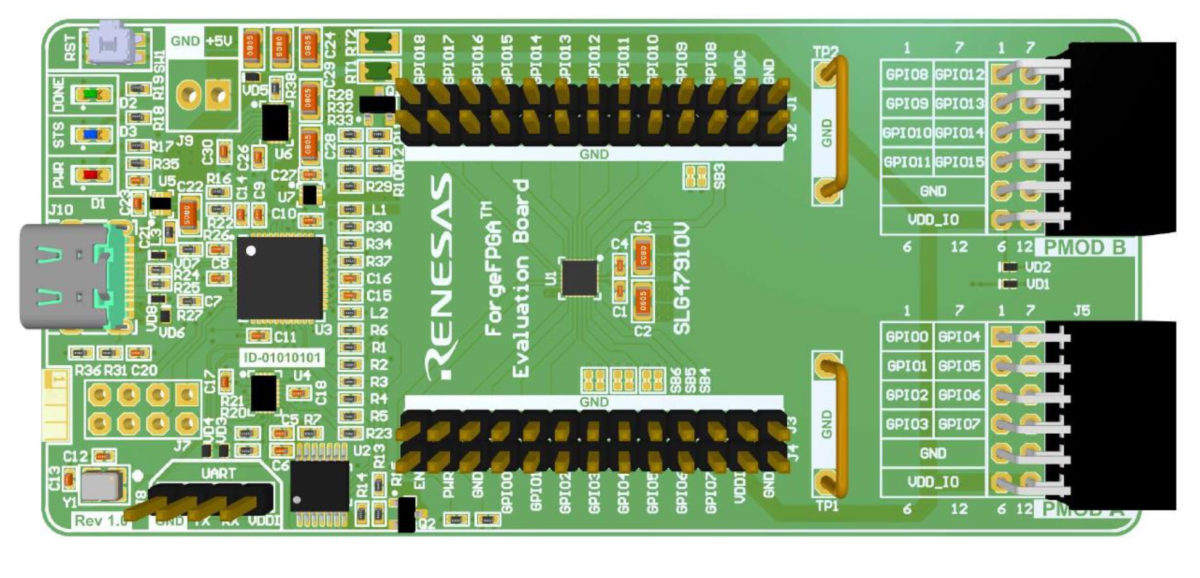

Näetkö sirun tämän seuraavan kuvan keskellä? Se on Renesasin ForgeFPGA QFN-24-paketissa, joka perustuu EFLX 1K IP:hen, jonka Renesas tarjoaa alle 1 dollarin hintapisteen volyymilla. Sen valmiustilan tavoitevirta on alle 20 uA. Pienempi koko, alhaisemmat kustannukset ja vähemmän virtaa avoimet ovet, jotka aiemmin suljettiin FPGA:lle. ForgeFPGA:n sukujuuret juontavat juurensa Silego Technologyan ja sitten Dialog Semiconductoriin, jonka Renesas osti vuonna 2021.

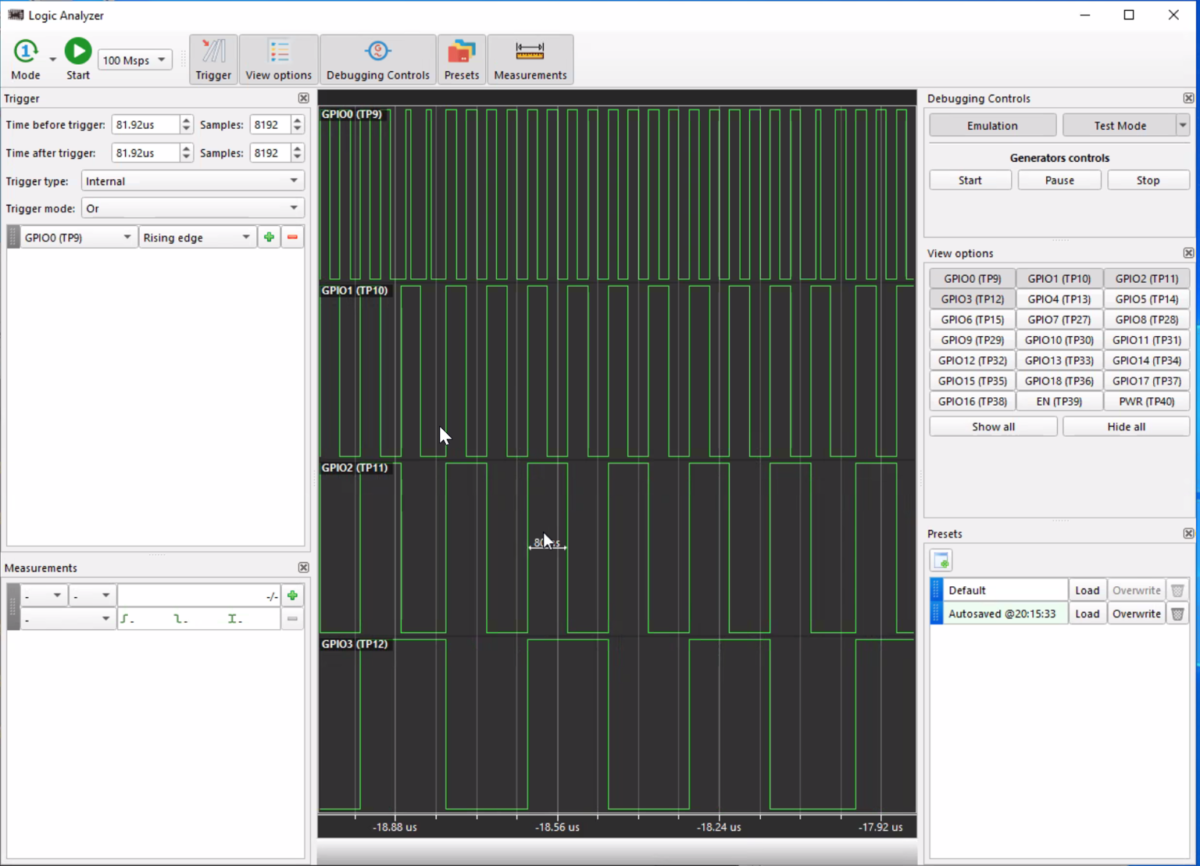

Renesas tuo Go Configure IDE -ympäristön ja asettaa graafisen käyttöliittymän Flex Logix EFLX -kääntäjän päälle. Se tukee ForgeFPGA-nastajen kartoittamista, Verilogin kääntämistä, bittivirran generointia ja siinä on kevyt logiikka-analysaattori.

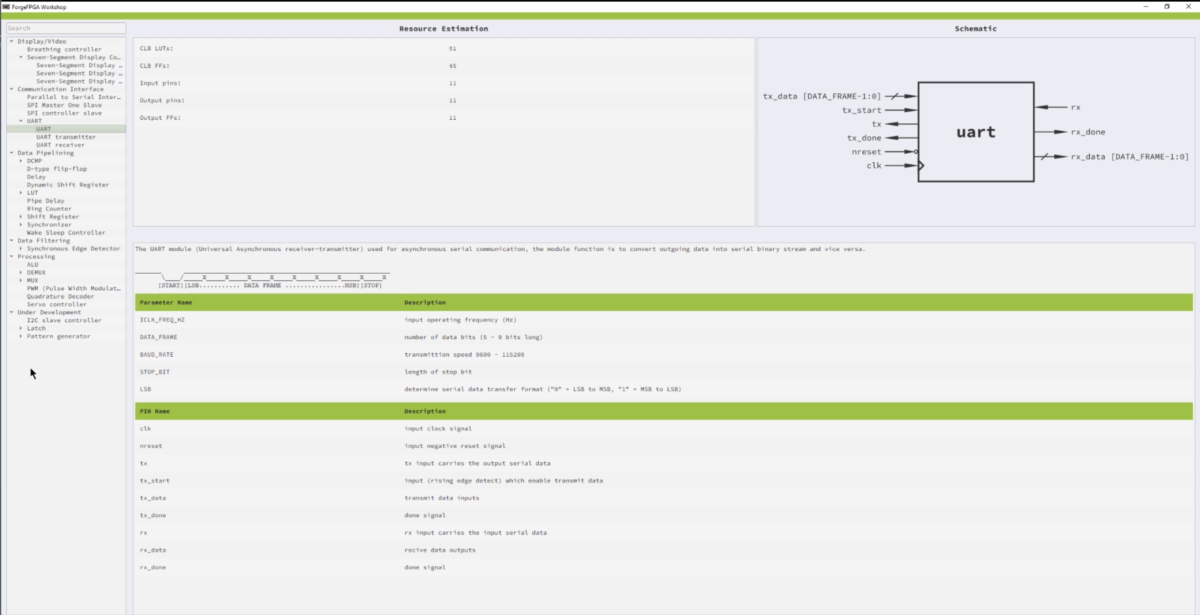

ForgeFPGA:n valmiiksi rakennetuissa sovelluslohkoissa on mielenkiintoinen, johon Flex Logixin Geoff Tate huomauttaa: UART. UART:n luominen logiikassa ei ole kovin vaikeaa, mutta käy ilmi, että jokainen on tehnyt sen eri tavalla, ja se on juuri tarpeeksi logiikkaa enemmän kuin pari erillistä sirua. ForgeFPGA on pala uudelleenkonfiguroitavaa logiikkaa, joka voi ratkaista tämän ongelman, jolloin yksi laitteistototeutus mukautuu nopeasti erilaisiin kokoonpanoihin.

ForgeFPGA on vain yksi esimerkki siitä, mitä voidaan tehdä Flex Logix EFLX 1K eFPGA -laatalla. Flex Logix voi mukauttaa IP:n eri prosessisolmuille, ja mix-and-match-laatoitusominaisuus tarjoaa skaalautuvuuden. Se saavuttaa uudet matalat tasot pienitehoiselle ohjelmoitavalle logiikalle ja antaa sirujen valmistajille mahdollisuuden erottaa ratkaisut merkittävillä tavoilla. Lisätietoja on osoitteessa:

Lue myös:

eFPGA:t, jotka käsittelevät salauksen ketteryyttä PQC:llä varustetuille SoC:ille

Flex Logix: Alan ensimmäinen AI-integroitu Mini-ITX-pohjainen järjestelmä

Flex Logix tekee yhteistyötä sisäisen tunnuksen kanssa suojatakseen eFPGA-alustan

Jaa tämä viesti:

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- Platoblockchain. Web3 Metaverse Intelligence. Tietoa laajennettu. Pääsy tästä.

- Lähde: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :On

- $ YLÖS

- 1

- 2021

- 3d

- a

- kyky

- Meistä

- siitä

- päästään

- hankittu

- yritysostot

- aktiivinen

- sopeuttaa

- kehittynyt

- Jälkeen

- aggressiivinen

- AI

- Kaikki

- Salliminen

- mahdollistaa

- ja

- Toinen

- Hakemus

- At

- takaisin

- este

- perustua

- Perusasiat

- BE

- välillä

- Iso

- suurempi

- Tukkia

- Blocks

- hallitus

- lainattu

- Tuo

- toi

- by

- nimeltään

- CAN

- kykenee

- keskus

- haaste

- tarkkailun

- Tarkastukset

- siru

- sirut

- valintoja

- kello

- suljettu

- monimutkainen

- Konfigurointi

- Yrityksen

- Hinta

- kustannukset

- voisi

- Pari

- kattavuus

- Luominen

- Nykyinen

- asiakassuhde

- jaksoa

- Tapailla

- syvä

- Malli

- suunniteltu

- suunnittelijat

- kehitetty

- laite

- Laitteet

- Vuoropuhelu

- eriyttää

- vaikea

- digitaalinen

- Kasta

- ovet

- kukin

- toimittaja

- mahdollistaa

- tarpeeksi

- merkintä

- ympäristö

- Aikakausi

- virhe

- arviointi

- jokainen

- esimerkki

- Eksoottinen

- kallis

- tutkia

- Valotus

- perhe

- FAST

- nopeampi

- Ominaisuudet

- Etunimi

- Joustavuus

- varten

- FPGA

- alkaen

- tuottaa

- antaa

- Go

- Goes

- kahva

- Käsittely

- Palvelimet

- Olla

- Korkea

- korkeampi

- pito

- HTTPS

- ID

- kuva

- täytäntöönpano

- parantaminen

- in

- Mukaan lukien

- teollisuuden

- halpa

- tiedot

- sen sijaan

- integroitu

- mielenkiintoinen

- liitäntä

- rajapinnat

- luontainen

- esittely

- Sijoittajat

- IP

- IT

- SEN

- jpg

- vain yksi

- Labs

- Kirjasto

- kevyt

- pitää

- Erä

- Matala

- alentamalla

- Lows

- Makro

- makrot

- tehty

- Makers

- johto

- Valmistajat

- kartoitus

- markkinat

- massiivinen

- kypsä

- max-width

- mielessä

- tila

- tilat

- raha

- lisää

- eniten

- Uusi

- seuraava

- solmut

- of

- tarjoamalla

- tarjoukset

- Tarjoukset

- on

- ONE

- avata

- Muut

- Muuta

- paketti

- pakkaus

- osa

- kumppani

- osat

- mänty

- Platforms

- Platon

- Platonin tietotieto

- PlatonData

- Ole hyvä

- pistettä

- Kirje

- teho

- esitetty

- lahjat

- aiemmin

- hinta

- todennäköisesti

- Ongelma

- prosessi

- käsittely

- näkyvä

- Putting

- nopeasti

- Rotu

- RAM

- nopea

- Lue

- uudistamiseksi

- vähentää

- huomattava

- poistamalla

- säilyttäminen

- Riski

- tie

- tiet

- roolit

- skaalautuvuus

- turvallinen

- puolijohde

- setti

- Vuorot

- signaali

- Pii

- Koko

- nukkua

- pieni

- pienempiä

- Pehmeä

- Ratkaisumme

- SOLVE

- jonkin verran

- Osavaltio

- virtaviivainen

- Tukee

- Sweep

- ottaa

- ottaen

- Kohde

- Elektroniikka

- testi

- Testaus

- että

- -

- heidän

- Nämä

- kertaa

- että

- tonnia

- ylin

- perinteinen

- tsmc

- varten

- käyttäjä

- Käyttöliittymä

- eri

- kautta

- Vierailla

- tilavuus

- odottaa

- tavalla

- Mitä

- joka

- with

- ilman

- Referenssit

- olisi

- zephyrnet