Desde su debut en la década de 1980 con LAN compartidas de 10 Mbps a través de cables coaxiales, Ethernet ha experimentado avances constantes y ahora tiene el potencial de admitir velocidades de hasta 1.6 Tbps. Esta progresión ha permitido que Ethernet sirva para una gama más amplia de aplicaciones, como transmisión en vivo, redes de acceso por radio y control industrial, enfatizando la importancia de una transferencia de paquetes confiable y la calidad del servicio. Con el ancho de banda de Internet actual de ~500 Tbps, existe una demanda creciente de un mejor manejo del tráfico back-end dentro del centro de datos. Aunque los servidores individuales aún no están operando a niveles de Terabit por segundo, el tráfico general del centro de datos se está acercando a esta escala, lo que llevó al grupo 802.3dj del IEEE a emprender esfuerzos de estandarización y requirió controladores Ethernet robustos y SerDes para administrar el flujo de datos en expansión. En medio de este contexto de demandas crecientes, la comunicación entre procesadores ya está alcanzando estas velocidades.

La comunicación entre procesadores encabeza la necesidad de velocidades de 1.6 T con latencia mínima. Si bien los dispositivos individuales están restringidos por sus capacidades de procesamiento inherentes y el tamaño del chip, la combinación de chips puede ampliar significativamente estas capacidades. Se espera que a la primera generación de aplicaciones le sigan conexiones de conmutador a conmutador dentro del centro de datos, lo que permitirá la combinación de procesadores y memoria de alto rendimiento, impulsando la escalabilidad y la eficiencia dentro de la computación en la nube.

Iniciativa 802.3dj de IEEE: avances en los estándares Ethernet para una interoperabilidad de 1.6 Tbps

El cumplimiento de los esfuerzos de estandarización en evolución es fundamental para una interoperabilidad perfecta del ecosistema. El grupo 802.3dj del IEEE está en el proceso de formular el próximo estándar Ethernet, que abarca capas físicas y parámetros de gestión para velocidades desde 200G hasta 1.6 Terabits por segundo. El objetivo del grupo es una velocidad de datos Ethernet MAC de 1.6 Tbps, apuntando a una tasa máxima de error de bits de no más de 10-13 en la capa MAC. Otras disposiciones incluyen interfaces de unidad de conexión (AUI) opcionales de 16 y 8 carriles adecuadas para diferentes aplicaciones de chip, aprovechando SerDes de 112G y 224G. Físicamente, la especificación de 1.6 Tbps implica la transmisión a través de 8 pares de cables twinax de cobre de hasta un metro y 8 pares de fibra para distancias que oscilan entre 500 metros y 2 km. Aunque se prevé la ratificación completa de la norma para la primavera de 2026, se prevé que el conjunto principal de características se complete en 2024.

Sobrecarga de ancho de banda y corrección de errores en subsistemas Ethernet de 1.6T

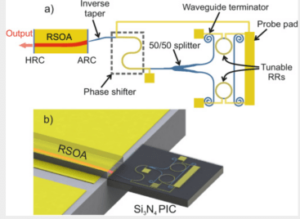

Fig. 1: Diagrama que muestra los componentes de un subsistema Ethernet de 1.6 T.

En iteraciones anteriores de Ethernet, el PCS se centraba principalmente en la codificación de datos para una detección confiable de paquetes. Sin embargo, con el aumento a velocidades de Ethernet de 1.6 T, la necesidad de corrección de errores de reenvío (FEC) se vuelve evidente, particularmente para contrarrestar la degradación de la señal incluso en enlaces cortos. Para este propósito, Ethernet 1.6T continúa utilizando Reed-Solomon FEC. Este enfoque crea una palabra de código que comprende 514 símbolos de 10 bits codificados en un bloque de 544 símbolos, lo que genera una sobrecarga de ancho de banda del 6%. Estas palabras de código FEC se distribuyen entre los enlaces físicos de AUI para que cada enlace físico (8 para Ethernet de 1.6 T) no lleve una palabra de código completa. Este método no sólo brinda protección adicional contra ráfagas de errores sino que también permite la paralelización en el decodificador del otro extremo, reduciendo así la latencia.

El accesorio de medio físico (PMA), que incluye una caja de cambios y SerDes, lleva la señal de Ethernet a los canales transmitidos. Para Ethernet de 1.6 T, esto implica 8 canales, cada uno de los cuales funciona a 212 Gbps, lo que representa una sobrecarga de FEC del 6 %. La técnica de modulación empleada es la modulación de amplitud de pulso de 4 niveles (PAM-4), que codifica dos bits de datos para cada símbolo de transmisión, duplicando así efectivamente el ancho de banda cuando se yuxtapone con el enfoque tradicional sin retorno a cero (NRZ). El mecanismo de transmisión se basa en la conversión de digital a analógico, mientras que en el extremo receptor una conversión de analógico a digital combinada con DSP garantiza una extracción precisa de la señal.

Además, es importante tener en cuenta que Ethernet PCS introduce un “FEC externo” que se extiende de extremo a extremo en un enlace Ethernet. Para reforzar los canales de mayor alcance, se está preparando una capa adicional de corrección de errores para líneas físicas individuales, probablemente adoptando un código de Hamming FEC. Se prevé que esta corrección encuentre su aplicación principal en módulos transceptores ópticos donde dicha corrección es imperativa.

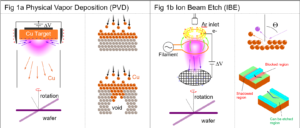

Fig. 2: Diagrama que muestra la sobrecarga adicional agregada al usar un FEC concatenado para un alcance extendido.

En el sistema de ejemplo representado en la figura 2, el MAC y el PCS están conectados mediante un módulo óptico y un tramo de fibra. El PCS tiene una tasa de error de bits de 10-5 en el enlace del módulo óptico, además de errores del propio enlace óptico. Usar un único RS-FEC de extremo a extremo no sería suficiente para lograr los 10-13 Estándar Ethernet, lo que hace que el enlace no sea confiable. Una opción sería una implementación triple de RS FEC separado en cada salto, lo que aumentaría significativamente los costos y la latencia. Una solución más eficaz es la integración de un código Hamming FEC concatenado específicamente para el enlace óptico, que soluciona los errores aleatorios típicos de las conexiones ópticas. Esta capa FEC interna crea una expansión adicional de la velocidad de línea de 212 Gbps a 226 Gbps, por lo que es esencial que SerDes pueda admitir esta velocidad de línea.

Desafíos de latencia en sistemas Ethernet de 1.6T

Fig. 3: Ruta de latencia para el subsistema Ethernet 1.6T.

Varios componentes contribuyen a la latencia de Ethernet: la cola de transmisión, la duración de la transmisión, el tiempo de recorrido medio y varios tiempos de procesamiento y recepción. Para visualizar esto, considere la figura 3, que muestra un subsistema Ethernet 1.6T completo. Si bien la latencia puede verse influenciada por el tiempo de reacción de la aplicación del extremo lejano, este factor es externo a Ethernet y, por lo tanto, a menudo se excluye durante el análisis de latencia. Minimizar la latencia en la interfaz Ethernet requiere comprender las circunstancias específicas. Por ejemplo, la latencia puede no ser una preocupación principal para las conexiones troncales entre conmutadores debido a retrasos inherentes en enlaces de clientes más lentos. La distancia también influye; longitudes mayores introducen más latencia. Por supuesto, esto no significa que debamos pasar por alto la latencia en otros escenarios, reducir la latencia es siempre un objetivo.

La latencia de transmisión está inherentemente ligada a la velocidad de Ethernet y al tamaño de la trama. Específicamente, para un sistema Ethernet de 1.6 T, la transmisión de un paquete de tamaño mínimo requiere 0.4 ns (esencialmente, una trama Ethernet por tic de un reloj de 2.5 GHz). Por otro lado, la transmisión de una trama de tamaño máximo estándar tarda 8 ns, extendiéndose a 48 ns para las tramas Jumbo. El medio elegido dicta además la latencia. Por ejemplo, la fibra óptica suele tener una latencia de 5 ns por metro, mientras que el cableado de cobre es ligeramente más rápido, con 4 ns por metro.

Un segmento sustancial de la latencia general tiene su origen en el controlador del receptor. El decodificador RS FEC introduce inherentemente latencia. Para iniciar la corrección de errores, el sistema debe recibir 4 palabras de código, que, a 1.6 Tbps, equivalen a 12.8 ns. Las actividades posteriores, incluida la corrección de errores y el almacenamiento en búfer, amplifican esta latencia. Si bien la duración del almacenamiento de la palabra clave FEC sigue siendo constante, la latencia durante la recepción del mensaje depende de la implementación específica. Sin embargo, la latencia se puede optimizar empleando meticulosas estrategias de diseño digital.

En esencia, existe una latencia inherente e inevitable debido al mecanismo FEC y a la distancia física o longitud del cable. Más allá de estos factores, la experiencia en diseño juega un papel fundamental para minimizar la latencia del controlador Ethernet. Aprovechar una solución completa que integra y optimiza MAC, PCS y PHY allana el camino para la implementación más eficiente y de baja latencia.

Resumen

Fig. 4: Éxito del silicio de primer paso para Synopsys 224G Ethernet PHY IP en un proceso de 3 nm que muestra ojos PAM-4 altamente lineales.

Ethernet de 1.6 Tbps está diseñado para las aplicaciones más exigentes en ancho de banda y sensibles a la latencia. Con el surgimiento de la tecnología SerDes 224G, junto con los avances en MAC y PCS IP, ahora se puede acceder a soluciones integrales que se ajustan continuamente a los estándares Ethernet 1.6T en evolución. Además, debido a la latencia intrínseca del protocolo y los métodos de corrección de errores, el diseño analógico y digital de IP debe ser elaborado diligentemente por diseñadores expertos para evitar introducir latencia innecesaria en la ruta de datos.

Lograr el máximo rendimiento para diseños de SoC de 1.6 T requiere una arquitectura optimizada de manera eficiente y prácticas de diseño meticulosas para cada componente del chip. Esto enfatiza la conservación de energía y minimiza la huella de silicio, haciendo realidad las velocidades de datos de 1.6T. IP PHY Ethernet Synopsys 224G probada con silicio ha preparado el escenario para el controlador PCS y MAC 1.6T. Utilizando técnicas de diseño, análisis, simulación y medición de vanguardia, Synopsys continúa brindando integridad de señal y rendimiento de fluctuación excepcionales, con un Solución Ethernet completa que incluye MAC+PCS+PHY.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :posee

- :es

- :no

- :dónde

- $ UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- de la máquina

- accesible

- Contabilidad

- preciso

- Lograr

- a través de

- actividades

- adicional

- Adicionales

- Adicionalmente

- Adopción

- avances

- seguir

- en contra

- Con el objetivo

- permitido

- ya haya utilizado

- también

- Aunque

- hacerlo

- en medio de

- cantidades

- amplian

- an

- análisis

- y

- anticipado

- Aplicación

- aplicaciones

- enfoque

- arquitectura

- somos

- AS

- At

- evitar

- Back-end

- fondo

- Ancho de banda

- BE

- se convierte en

- entre

- Más allá de

- Poco

- Bloquear

- reforzar

- impulsar

- Trae

- construye

- pero

- by

- cable

- cables

- PUEDEN

- capacidades

- llevar

- retos

- canales

- chip

- Papas fritas

- elegido

- circunstancias

- cliente

- Reloj

- Soluciones

- la computación en nube

- código

- combinado

- combinar

- Comunicación

- completar

- terminación

- componente

- componentes

- exhaustivo

- que comprende

- informática

- Protocolo de Tratamiento

- conjunción

- conectado

- Conexiones

- CONSERVACIÓN

- Considerar

- consideraciones

- consistente

- continúa

- continuamente

- contribuir

- control

- controlador

- Conversión

- Cobre

- Core

- Precio

- contrarrestar

- curso

- Elaborado

- crea

- Current

- datos

- Datacenter

- debut

- retrasos

- entregamos

- Demanda

- exigente

- demandas

- representando

- Diseño

- diseñadores

- diseños

- Detección

- Dispositivos

- dicta

- una experiencia diferente

- digital

- diligentemente

- distancia

- distribuidos

- No

- duplicación

- dos

- duración

- durante

- cada una

- Más temprano

- ecosistema

- Eficaz

- de manera eficaz

- eficiencia

- eficiente

- eficiente.

- esfuerzos

- aparición

- enfatiza

- enfatizando

- empleado

- empleando

- permite

- permitiendo

- engloba

- final

- de extremo a extremo

- asegura

- Todo

- error

- Errores

- escalada

- esencia

- esencial

- esencialmente

- Éter (ETH)

- Incluso

- Cada

- evidente

- evolución

- ejemplo

- Servicio

- excluidos

- en expansión

- expansión

- esperado

- experto

- Experiencia

- ampliar

- extensión

- externo

- Extracción

- Ojos

- factor

- factores importantes

- muchos

- más rápida

- Caracteristicas

- Con la participación de:

- Figura

- Encuentre

- Nombre

- Primera generación

- de tus señales

- centrado

- seguido

- Footprint

- formulando

- adelante

- FRAME

- Desde

- promover

- generación de AHSS

- da

- mayor

- Grupo procesos

- Grupo

- Creciendo

- mano

- Manejo

- Alta

- Alto rendimiento

- altamente

- Sin embargo

- HTML

- HTTPS

- INDISPENSABLE

- implementación

- importancia

- importante

- mejorado

- in

- En otra

- incluir

- Incluye

- creciente

- INSTRUMENTO individual

- industrial

- influenciado

- inherente

- inherentemente

- iniciar

- Iniciativa

- ejemplo

- Integra

- integración

- integridad

- Interfaz

- las interfaces

- Internet

- Interoperabilidad

- dentro

- intrínseco

- introducir

- Presenta

- Presentamos

- implica

- IP

- IT

- iteraciones

- SUS

- sí mismo

- jpg

- Lane

- Estado latente

- .

- ponedoras

- Longitud Mínima

- aprovechando

- que otros

- línea

- líneas

- LINK

- enlaces

- para vivir

- por más tiempo

- Baja

- Mac

- Realizar

- gestionan

- Management

- max-ancho

- máximas

- Puede..

- personalizado

- multiplataforma

- mecanismo

- mediano

- Salud Cerebral

- mensaje

- Método

- métodos

- meticuloso

- mínimo

- minimizar

- minimiza

- minimizando

- módulo

- Módulos

- más,

- MEJOR DE TU

- debe

- acercándose

- ¿ Necesita ayuda

- telecomunicaciones

- sin embargo

- no

- nota

- ahora

- objetivo

- of

- a menudo

- on

- ONE

- , solamente

- funcionamiento

- optimizado

- Optimiza

- Optión

- or

- Otro

- Más de

- total

- pares

- parámetros

- particularmente

- camino

- PCs

- para

- actuación

- actuaciones

- los libros físicos

- Físicamente

- industrial

- esencial

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- juega

- más

- posible

- industria

- prácticas

- las cuales

- primario

- tratamiento

- procesadores

- progresión

- proyectado

- Protección

- protocolo

- pulso

- propósito

- Emprendedor

- calidad

- Radio

- azar

- distancia

- Rate

- Tarifas

- en comunicarse

- alcanzando

- reacción

- Realidad

- recepción

- aprovecha

- recepción

- la reducción de

- confianza

- permanece

- representación

- requiere

- límite

- resultante

- robusto

- Función

- Arraigado

- correr

- Escalabilidad

- Escala

- escenarios

- sin costura

- Segundo

- visto

- segmento

- sensible

- separado

- ayudar

- de coches

- set

- Varios

- compartido

- En Corto

- tienes

- Demostramos a usted

- Signal

- significativamente

- Silicio

- simulación

- Tamaño

- So

- a medida

- Soluciones

- se extiende

- encabezando

- soluciones y

- específicamente

- especificación

- velocidades

- primavera

- Etapa

- estándar

- estandarización

- estándares de salud

- STORAGE

- estrategias

- en streaming

- posterior

- sustancial

- comercial

- tal

- adecuado

- SOPORTE

- símbolo

- te

- adaptado

- toma

- la técnica

- técnicas

- Tecnología

- que

- esa

- La

- su

- Ahí.

- de este modo

- por lo tanto

- Estas

- así

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- Así

- garrapata

- Atado

- equipo

- veces

- a

- parte superior

- tradicional

- tráfico

- transferir

- transmitir

- Triple

- dos

- principiante

- típicamente

- inevitable

- comprensión

- emprender

- unidad

- próximos

- a

- usando

- utilizar

- vía

- visualizar

- Camino..

- we

- cuando

- que

- mientras

- más ancho

- dentro de

- se

- aún

- zephyrnet

- cero