La resistividad del cobre depende de su estructura cristalina, volumen de huecos, límites de grano y desajuste de la interfaz del material, que se vuelve más significativo a escalas más pequeñas. La formación de alambres de cobre (Cu) se realiza tradicionalmente grabando un patrón de zanja en dióxido de silicio de bajo k mediante un proceso de grabado de zanja y posteriormente llenando la zanja con Cu mediante un flujo damasquinado. Desafortunadamente, este método produce estructuras multicristalinas con importantes límites de grano y huecos, lo que aumenta la resistencia del alambre de Cu. En este proceso también se utiliza un material de revestimiento de TaN altamente resistivo para evitar la difusión de Cu durante el proceso de recocido damasquinado.

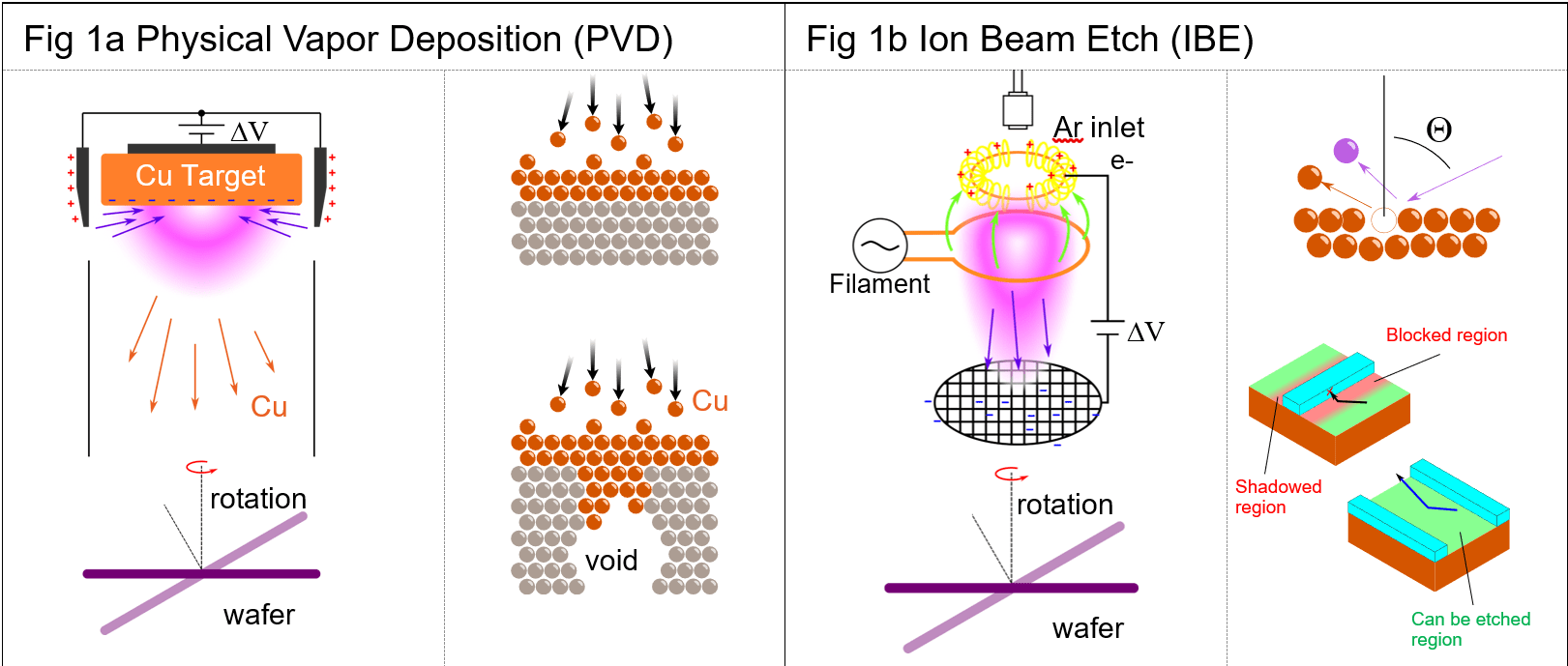

La deposición física de vapor (PVD) se puede utilizar para depositar cobre a altas energías cinéticas (entre 10 y 100 eV), formando estructuras monocristalinas densas y de baja resistencia. Un inconveniente del PVD es que la deposición de PVD tiene una línea de visión extendida y sólo puede depositarse uniformemente sobre superficies planas. No se puede utilizar para rellenar agujeros o zanjas profundas (figura 1a). Para formar formas de alambre aisladas, se debe depositar una capa uniforme de Cu sobre una superficie plana y luego grabarla físicamente mediante haces de iones. El Cu no forma compuestos volátiles con los gases reactivos, por lo que no se puede utilizar un proceso de grabado con iones reactivos. Los iones de Ar acelerados creados durante el grabado con haz de iones (IBE) pueden eliminar el Cu si el ángulo de incidencia es muy alto. Desafortunadamente, las regiones grabables estarán limitadas debido a los efectos de sombreado de la máscara. La Figura 1b muestra las regiones (en rojo) donde el material no se puede grabar cuando la máscara es perpendicular al haz de iones entrante. Este fallo de grabado se produce debido a la sombra o al bloqueo del camino del átomo expulsado. Cuando la máscara es paralela a la trayectoria del ion, se pueden grabar todas las regiones desenmascaradas. Por lo tanto, el grabado con haz de iones se limita al grabado de máscaras en forma de línea de longitudes arbitrariamente largas.

![]()

Fig. 1: (1a) Deposición física de vapor (PVD); (1b) Grabado con haz de iones (IBE).

Pasos del proceso y proceso de fabricación virtual.

Para comprender el efecto de la deposición y el grabado en la resistencia de la línea, ahora modelamos los procesos de grabado de PVD e IBE utilizando las funciones de deposición y grabado de visibilidad de SEMulator3D. El PVD se reprodujo utilizando un proceso de deposición con visibilidad de extensión angular de 30 grados en SEMulator3D, que modela con precisión la naturaleza aleatoria de los átomos de Cu expulsados durante el bombardeo con iones AR. El IBE se reprodujo en el modelo utilizando un grabado de visibilidad con una extensión angular de 2 grados y una inclinación de ángulo polar de 60 grados, para reflejar el comportamiento de los iones acelerados por la rejilla con divergencia de haz bajo. Se supone que ambas obleas tienen rotación libre. Otros pasos del proceso se han ajustado en el proceso de fabricación virtual para adaptarse a las limitaciones de IBE y PVD. La Figura 2 muestra la misma estructura creada utilizando un relleno de Cu damasquinado (figura 2a) y un proceso PVD/IBE (figura 2b). Se incluyeron pasos de proceso adicionales para incorporar ciertas limitaciones de PVD/IBE y crear la forma equivalente para nuestras estructuras finales deseadas.

![]()

Fig. 2: (2a) Fabricación de alambre de Cu con relleno damasquino; (2b) Fabricación de alambre PVD/IBE Cu.

Luego demostramos que se puede fabricar una celda de circuito SRAM equivalente de 16 nm con cables PVD/IBE respetando estas limitaciones. Dado que todas las capas de metal sobre el extremo medio de la línea están fabricadas a partir de una superficie plana, esto lo convierte en un candidato ideal para cables PVD/IBE, a diferencia de las complejas topologías de interconexión que se ven en un dispositivo finFET. La Figura 3 muestra la estructura aislada de cada capa metálica y los pasos necesarios para crear una estructura finFET de tres capas metálicas utilizando PVD/IBE.

![]()

Fig. 3: (3a) FinFET MEOL de 16 nm y 3 capas de metal; (3b) Fabricación de capas metálicas paso a paso mediante PVD/IBE.

Resultados de resistencia y conclusión.

Luego medimos la resistencia eléctrica de los cables desde la capa metálica superior hasta las vías de los canales finFET P y N, tanto para el flujo damasquinado como para la deposición física de vapor. La Figura 4 muestra el punto inicial y final de la medición de resistencia en los canales P y N (todos los demás materiales aislantes son transparentes). Para compensar la resistencia de la interfaz entre el revestimiento de TaN y el cable de cobre, se aumentó la resistividad del cobre utilizando una constante de caída exponencial de 1 nm en función de la distancia más cercana a la interfaz de TaN. Dado que no se espera que una deposición de Cu de relleno damasquinado sea completamente cristalina, la resistividad del Cu se incrementó en un 50%. El proceso de cobre PVD/IBE no utiliza un revestimiento de TaN, por lo que no se aplicó la función de caída exponencial y en este modelo se utilizó la resistividad global del cobre. En la figura 4 se incluye una tabla de resistividad que compara un flujo damasquino versus PVD.

![]()

Fig. 4: Punto inicial y punto final de la medición de resistencia en los canales P y N.

Los valores de resistencia calculados a partir de nuestro modelo indican que podemos lograr una disminución del 67% en la resistencia utilizando el método de fabricación IBE/PVD en comparación con un grabado en zanja convencional seguido de deposición damasquinada. Esto ocurre porque no se necesita un revestimiento de TaN en IBE/PVD y hay una menor resistividad de CU durante este proceso. Nuestros resultados indican que se pueden lograr mejoras de resistividad utilizando IBE/PVD en comparación con el relleno damasquinado durante la formación de líneas metálicas, a costa de un proceso de fabricación más complejo.

timoteo yang

(todos los mensajes)

Timothy Yang es ingeniero de aplicaciones de software en Coventor, una empresa de investigación de Lam. Trabaja en aplicaciones de desarrollo de procesos, integración y mejora de rendimiento, con experiencia en tecnologías de memoria. Antes de trabajar en Coventor, Yang trabajó en Tokyo Electron desarrollando esquemas de grabado, técnicas de mejora de patrones postlitográficos, control de flujo de procesos para aplicaciones de patrones SADP y SAQP, y tecnología fotorresistente de litografía de inmersión y EUV. Yang recibió su licenciatura en física de UCLA, una maestría en ciencia de materiales del Instituto de Tecnología de Chiba y un doctorado. Licenciado en Ciencias de Materiales por la Universidad de Tohoku.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Acuñando el futuro con Adryenn Ashley. Accede Aquí.

- Fuente: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :posee

- :es

- ][pag

- 1

- 10

- 100

- a

- arriba

- acelerado

- acomodar

- precisamente

- Lograr

- alcanzado

- Adicionales

- Equilibrado

- Todos

- Todos los Artículos

- y

- Angular

- aplicaciones

- aplicada

- AR

- somos

- AS

- ficticio

- At

- átomo

- BE

- Manga

- se convierte en

- esto

- entre

- límites

- by

- calculado

- PUEDEN

- candidato

- no puede

- a ciertos

- canales

- compañía

- en comparación con

- comparar

- integraciones

- constante

- restricciones

- control

- convencional

- Cobre

- Cost

- Para crear

- creado

- Cristal

- datos

- disminuir

- profundo

- Grado

- demostrar

- depende

- depositar

- depositado

- deseado

- el desarrollo

- Desarrollo

- dispositivo

- Difusión

- distancia

- Divergencia

- DE INSCRIPCIÓN

- durante

- cada una

- efecto

- los efectos

- ya sea

- ingeniero

- Equivalente a

- EV

- esperado

- Experiencia

- exponencial

- Fracaso

- Figura

- llenar

- plano

- de tus señales

- seguido

- formulario

- formación

- Formularios

- Gratuito

- Desde

- completamente

- función

- funciones

- Cuadrícula

- Tienen

- he

- Alta

- altamente

- Agujeros

- HTTPS

- idea

- inmersión

- es la mejora continua

- mejoras

- in

- incidente

- incluido

- Entrante

- incorporar

- aumentado

- Los aumentos

- indicar

- Innovadora

- integración

- Interfaz

- aislado

- IT

- SUS

- jpg

- Lam

- .

- ponedoras

- limitaciones

- Limitada

- línea

- líneas

- Largo

- Baja

- HACE

- máscara

- Mascarillas

- materiales

- materiales

- max-ancho

- medir

- Salud Cerebral

- metal

- Método

- Ed. Media

- modelo

- modelos

- más,

- Naturaleza

- necesario

- of

- on

- solicite

- Otro

- nuestros

- Paralelo

- camino

- Patrón de Costura

- los libros físicos

- Físicamente

- Física

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- punto

- polar

- Publicación

- Artículos

- evitar

- Anterior

- en costes

- azar

- recibido

- Rojo

- reflejar

- regiones

- remove

- la investigación

- Resistencia

- Resultados

- s

- mismo

- escamas

- esquemas

- Ciencia:

- semiconductor

- Forma

- en forma de

- formas

- Shows

- Visión

- importante

- Silicio

- desde

- soltero

- menores

- So

- Software

- propagación

- Comience a

- Estado

- paso

- pasos

- estructura

- Después

- Superficie

- mesa

- técnicas

- Tecnologías

- Tecnología

- esa

- La

- Estas

- Tres

- uña del pulgar

- a

- Tokio

- más alto

- tradicionalmente

- transparente

- UCLA

- entender

- universidad

- utilizan el

- usado

- utilizado

- Valores

- vía

- Virtual

- la visibilidad

- volátiles

- volumen

- vs

- que

- mientras

- seguirá

- Cable

- Actividades:

- trabajado

- funciona

- Rendimiento

- zephyrnet