Banias Labs ist ein Halbleiterunternehmen, das Infrastrukturlösungen für die Kommunikation der nächsten Generation entwickelt. Sein Zielmarkt ist der Markt für Hochleistungs-Computing-Infrastrukturen, einschließlich Hyperscale-Rechenzentren, Netzwerken, KI, optischen Modulen und Ethernet-Switch-SoCs für neue Hochleistungs-Computing-Designs. Diese SoCs erfordern Hochgeschwindigkeits-Ethernet-Designs und Lösungen mit geringer Latenz, um eine höhere Systemleistung zu bieten und die Markteinführungszeit zu verkürzen. Das Unternehmen hat einen optischen DSP-SoC auf 5-nm-Prozesstechnologie entwickelt, um den Anforderungen dieses Marktes gerecht zu werden.

![]()

Ein optischer DSP-SoC ist ein spezieller Typ eines System-on-Chip (SoC), der für den Einsatz in optischen Hochgeschwindigkeitskommunikationssystemen entwickelt wurde. Zusätzlich zum DSP umfasst das optische DSP-SoC typischerweise Hochgeschwindigkeitsschnittstellen-IP-Blöcke, wie z. B. Ethernet PHY IP, PCIe IP und DDR-Speichercontroller. Diese Arten von SoCs ermöglichen schnelle Datenübertragungen mit geringen Latenzen für die Signalverarbeitung in Echtzeit. Sie sind außerdem auf einen minimalen Stromverbrauch ausgelegt und eignen sich daher ideal für Anwendungen, die einen effizienten Betrieb mit reduzierten thermischen Problemen erfordern. Mit den Vorteilen gehen auch Herausforderungen einher. Aufgrund der speziellen Anforderungen optischer Kommunikationssysteme ist der Entwurf eines optischen DSP-SoCs anspruchsvoller als der Entwurf eines normalen SoCs.

Implementierungsherausforderungen

Die Herausforderungen drehen sich um die Komplexität des Designs, die strengen Leistungs- und Leistungsanforderungen und die Notwendigkeit, verschiedene Industriestandards zu erfüllen. Die Integration mehrerer IP-Blöcke, einschließlich des DSP-Prozessors, Ethernet-PHY-IP und anderer benutzerdefinierter Blöcke, erfordert sorgfältiges Design und Validierung. Zusätzliche Hochgeschwindigkeitsschnittstellen wie PCIe und DDR erhöhen die Komplexität des Designs zusätzlich. Die Hochgeschwindigkeitsschnittstellen und mehreren IP-Blöcke im System können zu Signalverzerrungen, Übersprechen und elektromagnetischen Störungen führen, die sich auf die Systemleistung und -zuverlässigkeit auswirken können. Die Analyse und Optimierung der Signal- und Leistungsintegrität muss früh im Entwurfszyklus durchgeführt werden, um sicherzustellen, dass das System seine Leistungs- und Zuverlässigkeitsanforderungen erfüllen kann. Schließlich kann es eine Herausforderung sein, die Time-to-Market-Anforderungen zu erfüllen. Der Markt für Hochleistungs-Computing-Infrastrukturen entwickelt sich rasant weiter und SoC-Entwicklungsteams müssen ihre Designs schnell liefern, um der Konkurrenz einen Schritt voraus zu sein.

So erreichen Sie den ersten Schritt zum Silicon-Erfolg

Die Bewältigung der oben genannten Herausforderungen erfordert einen umfassenden Ansatz. Eine der entscheidenden Komponenten leistungsstarker Lösungen mit geringer Latenz ist die Ethernet-PHY-IP. Die Ethernet-PHY-IP ist für die Schnittstelle der physikalischen Schicht zwischen dem SoC und dem Ethernet-Netzwerk verantwortlich. Das IP muss Hochgeschwindigkeits-Ethernet-Schnittstellen unterstützen, einschließlich 10G, 25G, 40G, 50G, 100G, 200G, 400G und 800G, und eine geringe Latenz und einen geringen Stromverbrauch bieten. Darüber hinaus muss das IP verschiedene Standards unterstützen, darunter IEEE 802.3 und Ethernet Alliance. Ein weiterer wichtiger Bestandteil ist die EDA Design Suite. Die EDA-Design-Suite muss eine umfassende Lösung für den Entwurf und die Überprüfung des SoC bieten, einschließlich Leistungsoptimierung, Leistungsanalyse, Flächenoptimierung und Ertragsanalyse. Insofern umfasst die EDA-Designsuite erweiterte Funktionen wie künstliche Intelligenz (KI) und maschinelles Lernen (ML), die für eine höhere Produktivität und eine kürzere Markteinführungszeit sorgen.

Synopsys beschleunigt den First-Pass-Silicon-Erfolg

Synopsys bietet Lösungen, die sich den einzigartigen Herausforderungen der Entwicklung von SoCs für den Markt für Hochleistungs-Computing-Infrastrukturen stellen. Das Unternehmen bietet eine umfassende IP-Lösung, die eine Routing-Machbarkeitsstudie, Richtlinien für Verpackungssubstrate, Signal- und Leistungsintegritätsmodelle sowie eine gründliche Crosstalk-Analyse umfasst. Dies ist unerlässlich, um die Herausforderungen der Signal- und Leistungsintegrität bei der Entwicklung eines optischen DSP-SoCs zu bewältigen. Das 112G Ethernet PHY IP von Synopsys bietet geringe Latenz, flexible Reichweitenlängen und ausgereifte 5-nm-Prozesstechnologie und ist damit eine ideale Lösung für Hyperscale-Rechenzentren, Netzwerke, KI, optische Module und Ethernet-Switch-SoCs. Darüber hinaus bietet Synopsys eine EDA Design Suite, die hochwertige Ergebnisse mit optimierter Leistung, Leistung, Fläche und Ertrag liefert. Die KI-gesteuerte EDA Design Suite von Synopsys bietet Lösungen zur Steigerung der Systemleistung und zur Beschleunigung der Markteinführung und ist damit ein wesentlicher Bestandteil einer erfolgreichen Lösung für den Markt für Hochleistungs-Computing-Infrastrukturen.

Zusammenfassung

Synopsys bietet leistungsstarke Lösungen mit geringer Latenz, die die Entwicklung fortschrittlicher Ethernet-Switches und Netzwerk-SoCs beschleunigen. Um mehr über die umfassenden IP-Lösungen von Synopsys, ihre umfassende EDA Design Suite und ihre AI-Enhanced EDA Suite zu erfahren, besuchen Sie die folgenden Seiten.

Die umfassenden IP-Lösungen von Synopsys

Die umfassende EDA-Suite von Synopsys

Die KI-gesteuerte EDA Design Suite von Synopsys

Lesen Sie auch:

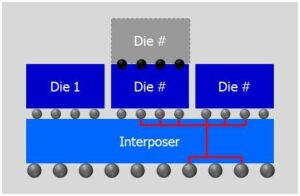

Multi-Die-Systeme: Die größte Störung im Computing seit Jahren

Mit High-Speed-Ethernet den wachsenden Hunger nach Bandbreite stillen

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :hast

- :Ist

- a

- Über uns

- oben

- beschleunigen

- beschleunigt

- Zusatz

- Zusätzliche

- zusätzlich

- Adresse

- advanced

- Vorteilen

- voraus

- AI

- Allianz

- ebenfalls

- an

- Analyse

- machen

- Ein anderer

- Anwendungen

- Ansatz

- SIND

- Bereich

- um

- künstlich

- künstliche Intelligenz

- Künstliche Intelligenz (AI)

- AS

- At

- Bandbreite

- BE

- Besser

- zwischen

- Größte

- Blockiert

- Auftrieb

- CAN

- vorsichtig

- Center

- Herausforderungen

- herausfordernd

- wie die

- Kommunikation

- Kommunikation

- Unternehmen

- Wettbewerb

- Komplexität

- Komponente

- Komponenten

- umfassend

- Computing

- Verbrauch

- erstellen

- kritischem

- Original

- Zyklus

- technische Daten

- Data Center

- Übergeben

- liefert

- Design

- entworfen

- Entwerfen

- Designs

- entwickelt

- Entwicklung

- Entwicklung

- entwickelt

- Störung

- Früh

- effizient

- aufstrebenden

- ermöglichen

- verbesserte

- gewährleisten

- essential

- sich entwickelnden

- konfrontiert

- FAST

- Eigenschaften

- Endlich

- Vorname

- flexibel

- Folgende

- Aussichten für

- für

- weiter

- persönlichem Wachstum

- Richtlinien

- Hohe Leistungsfähigkeit

- hochwertige

- HTML

- HTTPS

- Hunger

- ideal

- IEEE

- Image

- Impact der HXNUMXO Observatorien

- Imperativ

- wichtig

- in

- Dazu gehören

- Einschließlich

- hat

- Energiegewinnung

- Industrie-Standards

- Infrastruktur

- Integration

- Integrität

- Intelligenz

- Schnittstelle

- Schnittstellen

- IP

- Probleme

- IT

- SEINE

- Labs

- Latency

- Schicht

- LERNEN

- lernen

- Sneaker

- Maschine

- Maschinelles Lernen

- um

- Making

- Markt

- Reife

- max-width

- Triff

- Treffen

- Memory

- erwähnt

- ML

- für

- Modulen

- mehr

- mehrere

- Need

- Netzwerk

- Vernetzung

- nächste Generation

- of

- Angebote

- on

- EINEM

- Betrieb

- Optimierung

- optimiert

- Andere

- besitzen

- Verpackung

- passieren

- Leistung

- physikalisch

- Plato

- Datenintelligenz von Plato

- PlatoData

- Post

- Werkzeuge

- Prozessdefinierung

- Verarbeitung

- Prozessor

- PRODUKTIVITÄT

- die

- bietet

- schnell

- schnell

- erreichen

- Lesen Sie mehr

- Echtzeit

- Reduziert

- regulär

- Zuverlässigkeit

- erfordern

- Voraussetzungen:

- erfordert

- für ihren Verlust verantwortlich.

- Die Ergebnisse

- Risiko

- Halbleiter

- Signal

- Silizium

- Lösung

- Lösungen

- spezialisiert

- Normen

- bleiben

- Studie

- Erfolg

- erfolgreich

- so

- Suite

- Support

- Schalter

- System

- Systeme und Techniken

- Target

- Teams

- Technologie

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- ihr

- Sie

- Thermal-

- Diese

- vom Nutzer definierten

- fehlen uns die Worte.

- zu

- auch

- Transfers

- Typen

- typisch

- einzigartiges

- -

- Bestätigung

- verschiedene

- verifizieren

- Besuchen Sie

- welche

- mit

- Ausbeute

- Ihr

- Zephyrnet