Synopsys veranstaltete kürzlich ein branchenübergreifendes Panel zum Stand von Multi-Chip-Systemen, das ich nicht zuletzt wegen seiner Relevanz für die schnelle Beschleunigung KI-zentrierter Hardware interessant fand. Mehr dazu weiter unten. Zu den Diskussionsteilnehmern, die alle wichtige Rollen in Multi-Die-Systemen innehaben, gehörten Shekhar Kapoor (Senior Director of Product Management, Synopsys), Cheolmin Park (Corporate VP, Samsung), Lalitha Immaneni (VP Architecture, Design and Technology Solutions, Intel) und Michael Schaffert (Senior VP, Bosch) und Murat Becer (VP R&D, Ansys). Moderiert wurde das Panel von Marco Chiappetta (Mitbegründer und Hauptanalyst, HotTech Vision and Analysis).

Ein großer Nachfragetreiber

Es ist üblich, unter dieser Überschrift alle üblichen Verdächtigen (HPC, Automotive usw.) aufzulisten, aber diese Liste vernachlässigt vielleicht den größten zugrunde liegenden Faktor – den aktuellen Kampf um die Vorherrschaft in allen LLM- und generativen KI-Bereichen. Große Sprachmodelle bieten neue Ebenen von SaaS-Diensten in den Bereichen Suche, Dokumentenerstellung und andere Funktionen, mit großen Wettbewerbsvorteilen für denjenigen, der dies zuerst richtig macht. Auf mobilen Geräten und im Auto lassen die überlegene Steuerung und Rückmeldung auf natürlicher Sprache bestehende sprachbasierte Optionen vergleichsweise primitiv erscheinen. Mittlerweile können generative Methoden zum Erstellen neuer Bilder mithilfe von Diffusions- und Poisson-Strömungsmodellen spektakuläre Grafiken hervorbringen, die auf Text oder einem Foto basieren und durch Bildbibliotheken ergänzt werden. Als Verbrauchermagnet könnte sich dies als das nächste große Ding für zukünftige Telefonveröffentlichungen erweisen.

Während transformatorbasierte KI eine große Chance bietet, bringt sie auch Herausforderungen mit sich. Die Technologien, die solche Methoden ermöglichen, haben sich bereits in der Cloud bewährt und entstehen am Rande, sind jedoch bekanntermaßen speicherhungrig. Produktions-LLMs umfassen Milliarden bis Billionen Parameter, die in den Transformator geladen werden müssen. Ebenso hoch ist die Nachfrage nach In-Process-Arbeitsplätzen; Bei der diffusionsbasierten Bildgebung wird einem Gesamtbild nach und nach Rauschen hinzugefügt, um dann wiederum über transformatorbasierte Plattformen zu einem modifizierten Bild zurückzukehren.

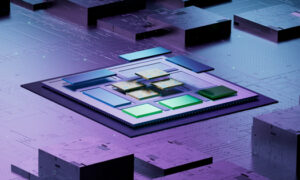

Abgesehen von einem anfänglichen Ladevorgang kann sich keiner dieser Prozesse den Aufwand leisten, der mit der Interaktion mit externem DRAM verbunden ist. Latenzen wären inakzeptabel und der Strombedarf würde den Akku eines Telefons entladen oder das Strombudget eines Rechenzentrums sprengen. Der gesamte Speicher muss sich in der Nähe – sehr nahe – der Recheneinheit befinden. Eine Lösung besteht darin, SRAM auf den Beschleuniger zu stapeln (wie AMD und jetzt Intel für ihre Serverchips demonstriert haben). Der integrierte Speicher mit hoher Bandbreite stellt eine weitere etwas langsamere Option dar, ist aber immer noch nicht so langsam wie Off-Chip-DRAM.

All dies erfordert Multi-Die-Systeme. Wo stehen wir also, wenn es darum geht, diese Option serienreif zu machen?

Ansichten darüber, wo wir uns befinden

Ich habe viel Enthusiasmus für das Wachstum in diesem Bereich gehört, in Bezug auf Akzeptanz, Anwendungen und Tools. Intel, AMD, Qualcomm und Samsung sind in diesem Bereich eindeutig sehr aktiv. Apple M2 Ultra ist bekanntermaßen ein Dual-Die-Design und AWS Graviton 3 ein Multi-Die-System. Ich bin mir sicher, dass es unter den großen System- und Halbleiterhäusern noch viele andere Beispiele gibt. Ich habe den Eindruck, dass die Chips immer noch überwiegend intern beschafft werden (außer vielleicht bei HBM-Stacks) und in Foundry-Packaging-Technologien von TSMC, Samsung oder Intel zusammengebaut werden. Allerdings hat Tenstorrent gerade bekannt gegeben, dass sie Samsung für die Herstellung ihres KI-Designs der nächsten Generation als Chiplet (ein Chip, der für die Verwendung in einem Multi-Chip-System geeignet ist) ausgewählt haben, sodass sich dieser Bereich bereits auf eine breitere Chip-Beschaffung zubewegt.

Alle Diskussionsteilnehmer waren natürlich begeistert von der allgemeinen Richtung, und es ist offensichtlich, dass sich Technologien und Tools schnell weiterentwickeln, was für die Begeisterung verantwortlich ist. Lalitha begründete diese Begeisterung damit, dass die Art und Weise, wie Multi-Chip-Systeme derzeit entwickelt und entworfen werden, noch in den Kinderschuhen steckt und noch nicht bereit ist, einen umfassenden wiederverwendbaren Markt für Chips zu eröffnen. Das überrascht mich nicht. Eine Technologie dieser Komplexität sollte zunächst in engen Partnerschaften zwischen Systemdesignern, Gießereien und EDA-Unternehmen reifen, möglicherweise über mehrere Jahre hinweg, bevor sie einem größeren Publikum zugänglich gemacht werden kann.

Ich bin mir sicher, dass Gießereien, Systembauer und EDA-Unternehmen nicht alle ihre Karten zeigen und möglicherweise weiter sind, als sie anpreisen. Ich freue mich darauf, mehr zu hören. Sie können sich die Podiumsdiskussion ansehen KLICKEN SIE HIER.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/artificial-intelligence/336319-synopsys-panel-updates-on-the-state-of-multi-die-systems/

- :Ist

- :nicht

- :Wo

- 180

- 300

- a

- LiveBuzz

- Beschleunigung

- Beschleuniger

- Trading Konten

- aktiv

- Fügt

- Adoption

- Vorteilen

- Werbung (Advertise)

- aufs Neue

- AI

- Alle

- entlang

- bereits

- am

- AMD

- unter

- an

- Analyse

- Analytiker

- und

- angekündigt

- Ein anderer

- von jedem Standort

- Apple

- Anwendungen

- Architektur

- SIND

- AS

- montiert

- At

- Publikum

- Automobilindustrie

- AWS

- Zurück

- Bandbreite

- austauschbare Akkus

- BE

- Bevor

- Sein

- unten

- zwischen

- Big

- Größte

- Milliarden

- blasen

- Bosch

- breiteres

- Haushalt

- Bauherren

- aber

- by

- CAN

- Fähigkeiten

- Auto

- Karten

- Herausforderungen

- Pommes frites

- Auswählen

- gewählt

- Cloud

- Co-Gründer

- kommt

- gemeinsam

- Unternehmen

- Vergleich

- wettbewerbsfähig

- Komplexität

- Berechnen

- Verbraucher

- Smartgeräte App

- Unternehmen

- könnte

- Erstellen

- Schaffung

- Strom

- Zur Zeit

- Datacenter

- Demand

- Synergie

- Design

- entworfen

- Designer

- Geräte

- Sterben

- Rundfunk

- Richtung

- Direktor

- Diskussion

- Dokument

- Tut nicht

- Domain

- Herrschaft

- abtropfen

- zeichnen

- Zeichnung

- Edge

- aufstrebenden

- Begeisterung

- begeistert

- gleichermaßen

- etc

- alles

- sich entwickelnden

- Beispiele

- Außer

- vorhandenen

- erweitern

- umfangreiche

- extern

- Faktor

- prächtig

- FAST

- Feedback

- Vorname

- Fluss

- Aussichten für

- vorwärts

- gefunden

- Giesserei

- für

- voller

- weiter

- Zukunft

- Allgemeines

- Generation

- generativ

- Generative KI

- bekommen

- Grafik

- Wachstum

- Hardware

- Haben

- Überschrift

- gehört

- Hörtests

- GUTE

- gehostet

- Houses

- aber

- hpc

- HTML

- HTTPS

- riesig

- Hungrig

- i

- Image

- Bilder

- Imaging

- in

- Anfangs-

- Intel

- Interaktion

- interessant

- innen

- IT

- SEINE

- jpg

- nur

- Kapoor

- bekannt

- Sprache

- grosse

- größer

- starten

- am wenigsten

- Cholesterinspiegel

- Bibliotheken

- !

- Gefällt mir

- Liste

- Belastung

- aussehen

- Los

- M2

- Dur

- um

- Making

- Management

- Marco

- Markt

- reifen

- max-width

- Kann..

- vielleicht

- me

- Mittlerweile

- Memory

- Methoden

- Michael

- Mobil

- mobile Geräte

- für

- geändert

- mehr

- Multi

- sollen

- Natürliche

- In der Nähe von

- Bedürfnisse

- Neu

- weiter

- Lärm

- Andere

- Bemerkens

- jetzt an

- of

- bieten

- on

- EINEM

- Gelegenheit

- Option

- Optionen

- or

- Andere

- übrig

- Verpackung

- Tafel

- Podiumsdiskussion

- Parameter

- Park

- Partnerschaften

- vielleicht

- Telefon

- Plattformen

- Plato

- Datenintelligenz von Plato

- PlatoData

- Reichlich

- möglich

- Post

- Werkzeuge

- überwiegend

- Geschenke

- Primitive

- Principal

- anpassen

- Produkt

- Produktmanagement

- Produktion

- zunehmend

- Belegen

- zuverlässig

- Pumpe

- Qualcomm

- F&E

- schnell

- bereit

- kürzlich

- Mitteilungen

- Relevanz

- erfordert

- wiederverwendbar

- Recht

- Rollen

- Rollen

- Führen Sie

- SaaS

- Samsung

- Suche

- scheint

- Verkauft

- Halbleiter

- Senior

- Server

- Lösungen

- mehrere

- Short

- sollte

- zeigt

- signifikant

- langsam

- So

- Lösung

- Lösungen

- etwas

- bezogen

- Sourcing

- Raumfahrt

- spektakulär

- Stapel

- Stacks

- Bundesstaat

- Immer noch

- so

- geeignet

- Oberteil

- sicher

- Überraschung

- System

- Systeme und Techniken

- Technologies

- Technologie

- Text

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- The Buzz

- Der Staat

- ihr

- dann

- Dort.

- Diese

- vom Nutzer definierten

- Ding

- fehlen uns die Worte.

- Durch

- zu

- Werkzeuge

- Top

- gegenüber

- Transformator

- Billionen

- TSMC

- Ultra-

- für

- zugrunde liegen,

- Updates

- benutzt

- Verwendung von

- üblich

- sehr

- Seh-

- vp

- wurde

- Ansehen

- Weg..

- we

- waren

- welche

- wer auch immer

- werden wir

- mit

- Werk

- würde

- Jahr

- noch

- U

- Zephyrnet