Designer haben viele Möglichkeiten, RISC-V-Lösungen zu differenzieren. Ein Pfad führt zu verschiedenen RISC-V-Kernanpassungen und -Erweiterungen gemäß der Spezifikation. Ein anderer Schwerpunkt liegt auf der Auswahl und Zusammenstellung von IP-Blöcken in einem vollständigen System-on-Chip (SoC)-Design um einen oder mehrere RISC-V-Kerne. Ein dritter Ansatz zeichnet sich ab: die Verbindung von RISC-V-Kernen und anderen IP-Blöcken mit einem Network-on-Chip (NoC) anstelle einer einfachen Busstruktur. Und das nicht nur im High-End-Bereich – die Kombination von RISC-V-Kernen mit NoCs löst viele SoC-Designherausforderungen, bei denen Daten in jeder Arbeitslast unter Verwendung eines beliebigen On-Chip-Protokolls effizient fließen müssen.

Leistungsstufen ändern sich mit fortschrittlichen Verbindungsschemata

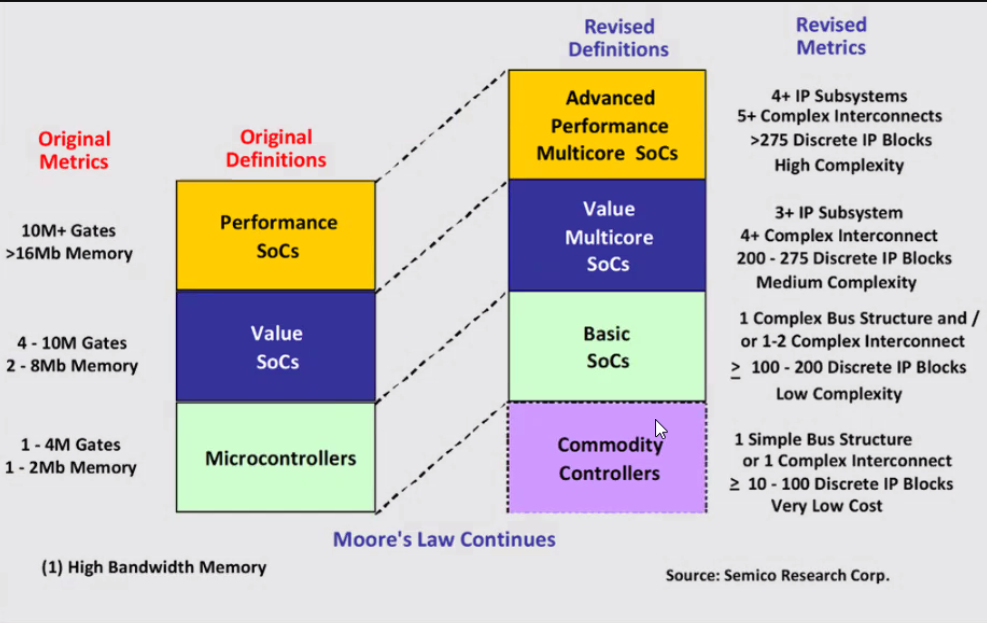

Das bloße Zählen von Gates, Kernen und Peripherieblöcken beschreibt nicht mehr das Leistungspotenzial eines SoC-Designs. Laut Semico Research definieren Verbindungsschemata nun die Grenzen zwischen SoC-Leistungsstufen, und es wurde eine neue Stufe eröffnet, in der Verbindungen von einfachen Busstrukturen zu anspruchsvolleren Schemata wechseln.

Die aktualisierte Definition von Semico erkennt drei Kräfte am Werk: die Verbreitung von Multicore-Designs, eine höhere Messlatte für das, was als komplexes Design gilt, und die daraus resultierende Verwischung der Grenze zwischen „Mikrocontroller“ und „SoC“. Nach Semicos neuester Ansicht verschwindet der Begriff der Gate-Zählung als Metrik, da ein moderner Prozessorkern viele Gates mit sich ziehen kann. Die Komplexität wird zu einer Funktion von Verbindungen, die je nach Subsystemen und verschiedenen IP-Blöcken variieren.

SoC-Leistungsstufen, Bild mit freundlicher Genehmigung von Semico Research Corp.

Wo ein einfacher Bus ausreicht, wahrscheinlich ein Teil mit einem einzelnen Prozessorkern und Peripheriegeräten mit niedrigem Arbeitszyklus, die nicht ständig um den Bus konkurrieren, sieht Semico eine Standard-Controller-Ebene. Alles, was darüber hinausgeht, wird zu einem SoC, wobei vermutlich zumindest einige Peripheriegeräte um On-Chip-Bandbreite und die Aufmerksamkeit der Prozessorkerne kämpfen. Höhere SoC-Stufen verfügen über mehrere Kerne und mehrere IP-Subsysteme, jedes mit abgestimmter Verbindungstechnologie.

NoCs übernehmen mehr Protokolle und Subsysteme

RISC-V ist in diesen Leistungsstufen schnell aufgestiegen, da leistungsstärkere Kerne auf den Markt kamen, wobei die Anwendbarkeit am unteren Ende der Semico-Skala nicht geringer ist. Allerdings haben RISC-V-Entwickler möglicherweise weniger Erfahrung mit komplexen Verbindungsschemata, die in den höheren Ebenen zu finden sind. „TileLink mag der erste Gedanke für RISC-V-Verbindungen sein, aber es kann schwierig sein, es in komplexeren Szenarien zu verwenden“, sagt Frank Schirrmeister, VP of Solutions and Business Development bei Arteris.

Die Superleistung eines NoC liegt in seiner Fähigkeit, Subsysteme mithilfe verschiedener Protokolle zu verbinden, und SoC-Designer werden wahrscheinlich selbst bei mäßiger Komplexität auf mehrere Protokolle stoßen. AXI hat die Wettbewerbsbedingungen für einfache IP-Blockverbindungen geebnet. Multicore-Lösungen mit Co-Processing-Blöcken erfordern Cache-Kohärenz, was zum CHI-Protokoll führt. Die gemeinsame Nutzung des I/O-Speichers trug zur Entwicklung der schnelleren CXL-Verbindung bei. „Wenn es an der Zeit ist, Rechenleistung und Transport mit verschiedenen Subsystemen und Protokollen gemeinsam zu optimieren, ist ein NoC die bessere Lösung“, fährt Schirrmeister fort.

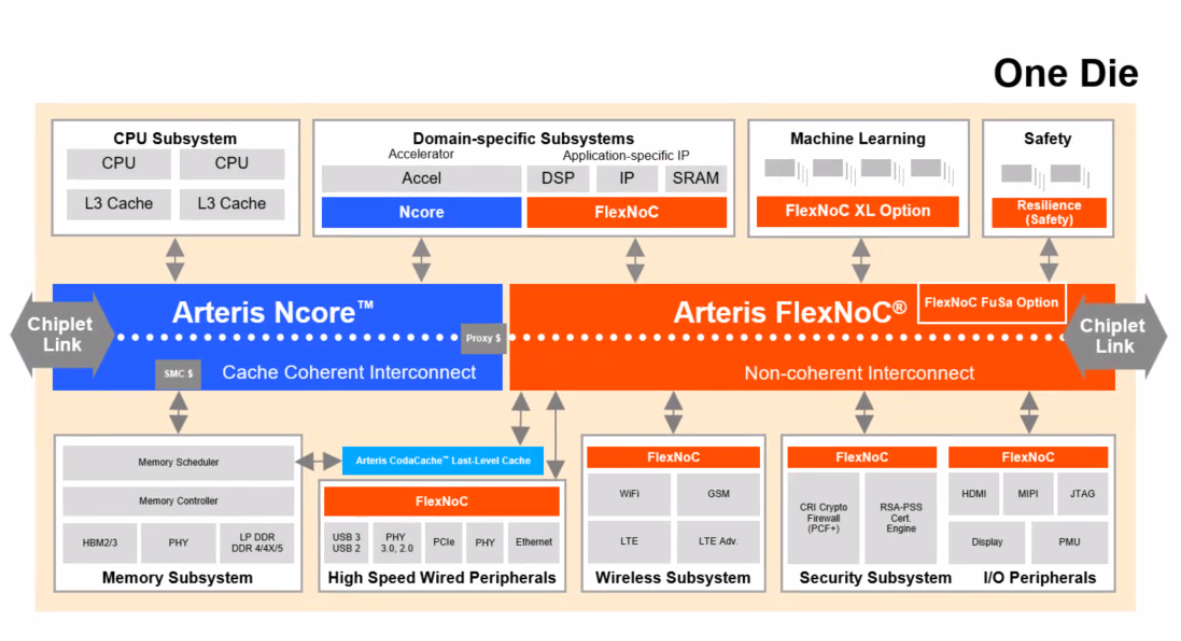

Wie kann die Paarung von RISC-V-Kernen mit NoCs aussehen? Arteris-Kunde Tenstorrent gibt einen Einblick in die Möglichkeiten. Ihr jüngster Schwerpunkt liegt auf der Entwicklung eines wiederverwendbaren Chiplets, das RISC-V-Kerne, IP zur Beschleunigung maschinellen Lernens und Standardperipheriegeräte kombiniert, die in vielen Edge-KI-Anwendungen zu finden sind. Im Maßstab könnte eine Single-Die-Implementierung wie im folgenden Diagramm aussehen und die Cache-kohärente Verbindung Arteris Ncore und mehrere Segmente der nicht-kohärenten Verbindung Arteris FlexNoC verwenden.

Bild mit freundlicher Genehmigung von Arteris

Ein Smart Memory Controller (SMC) bietet eine leistungsstarke Speicherverbindung auf Serverniveau in speicherintensiven Anwendungen. Der unbenannte „Chiplet-Link“ könnte UCIe sein, eine relativ neue Spezifikation, die für eine engere Chiplet-Integration optimiert ist. Wenn neue Subsystemverbindungen entstehen, ist die Anpassung eines Abschnitts des NoC einfacher zu bewältigen, als die gesamte Chip-weite Struktur aufzureißen.

Die Kombination von RISC-V-Kernen mit NoCs senkt das Risiko und die Markteinführungszeit

Wenn dieses Diagramm komplex aussieht und zugegebenermaßen die meisten RISC-V-Anwendungen derzeit vielleicht nicht so komplex sind, bedenken Sie Folgendes: Chiplets treiben die Integration bereits viel weiter voran. Der heutige fortschrittliche RISC-V-Multicore-Teil wird im nächsten Jahr der Value-SoC sein, wenn die Innovation an Fahrt gewinnt.

Die Entwicklungstools Arteris Ncore und Arteris FlexNoC geben RTL zur Implementierung aus und bieten mehrere Vorteile. Die physikalische NoC-Schätzung ist in einem EDA-Workflow unkompliziert. Auch NoC-Parameteranpassungen, wie etwa die Anzahl der Pipeline-Stufen, sind in EDA-Tools nur ein paar Klicks entfernt. Die oben erwähnten Modifikationen zum Hinzufügen eines Subsystemprotokolls können ebenfalls problemlos durchgeführt werden. „Im High-End-Bereich erhalten Anwender sofortigen Zugriff auf unsere NoC-Expertise“, sagt Schirrmeister. „Am unteren Ende sind unsere Tools einfach zu verwenden, um im ersten Durchgang erfolgreich zu sein und einen Wachstumspfad für ehrgeizigere zukünftige Projekte mit komplexen Verbindungen bereitzustellen.“

Die Kombination von RISC-V-Kernen mit NoCs verringert das Risiko, dass ein weiterer IP-Block in ein Design eindringt und eine Welle von Neugestaltungen der Verbindungen auf dem gesamten Chip auslöst. Außerdem verkürzt sich die Markteinführungszeit für komplexe SoC-Designs im Vergleich zu Do-it-yourself-Verbindungsstrukturen. Die anderen Vorteile von NoCs, wie etwa Bandbreiten- und Energieverwaltung, haben wir hier nicht besprochen, aber die Argumente für NoCs in RISC-V-Designs sprechen schon allein angesichts eines vielfältigen Protokollmixes.

Besuchen Sie die Arteris-Website Weitere Informationen zu NoCs finden Sie hier und andere Produkte.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- a

- Fähigkeit

- oben

- Beschleunigung

- Zugang

- erreicht

- Nach

- über

- Hinzufügen

- Anpassungen

- advanced

- Vorteilen

- AI

- bereits

- ebenfalls

- ehrgeizig

- an

- machen

- Ein anderer

- Antworten

- jedem

- etwas

- erscheinen

- Anwendungen

- SIND

- um

- AS

- At

- Aufmerksamkeit

- ein Weg

- Bandbreite

- Bar

- BE

- wird

- Vorteile

- Besser

- zwischen

- Blockieren

- Blockiert

- Bus

- Geschäft

- Geschäftsentwicklung

- aber

- CAN

- Häuser

- Herausforderungen

- Übernehmen

- Ändern

- Chip

- Vereinigung

- Ware

- verglichen

- abschließen

- Komplex

- Komplexität

- Berechnen

- Vernetz Dich

- Verbindung

- Verbindungen

- Geht davon

- betrachtet

- Berücksichtigung

- weiter

- ständig

- Controller

- Kernbereich

- Corp

- könnte

- Zählen

- Erstellen

- Kunde

- technische Daten

- definieren

- Definition

- Demand

- Design

- Designer

- Designs

- Entwicklung

- Entwicklungswerkzeuge

- anders

- schwer

- diskutiert

- verschieden

- do

- Fahren

- jeder

- Einfache

- Edge

- effizient

- entstehen

- aufstrebenden

- Ende

- Eingabe

- Ganz

- Sogar

- ERFAHRUNGEN

- Expertise

- Erweiterungen

- beschleunigt

- wenige

- Feld

- Kampf

- Vorname

- Fluss

- Setzen Sie mit Achtsamkeit

- konzentriert

- Folgende

- Aussichten für

- Streitkräfte

- gefunden

- frank

- für

- Funktion

- Zukunft

- Gewinnen

- Gates

- Unterstützung

- Blick

- erteilt

- Wachstum

- Haben

- dazu beigetragen,

- hier

- GUTE

- Hohe Leistungsfähigkeit

- höher

- aber

- HTTPS

- Image

- unmittelbar

- Implementierung

- in

- Information

- Innovation

- beantragen müssen

- Integration

- vernetzen

- verbindet

- in

- IP

- IT

- SEINE

- nur

- neueste

- startet

- am wenigsten

- weniger

- Gefällt mir

- wahrscheinlich

- Line

- Linien

- länger

- aussehen

- aussehen wie

- SIEHT AUS

- Sneaker

- senken

- Management

- viele

- max-width

- Kann..

- vielleicht

- Memory

- erwähnt

- Metrisch

- mischen

- moderieren

- modern

- Änderungen

- mehr

- vor allem warme

- gerührt

- viel

- mehrere

- sollen

- Neu

- weiter

- nicht

- Notion

- jetzt an

- Anzahl

- of

- on

- EINEM

- geöffnet

- optimiert

- or

- Andere

- UNSERE

- Möglichkeiten für das Ausgangssignal:

- Frieden

- Paarung

- Parameter

- Teil

- Weg

- für

- Leistung

- peripher

- Peripheriegeräte

- physikalisch

- wählen

- Picks

- Pipeline

- Plato

- Datenintelligenz von Plato

- PlatoData

- Play

- spielend

- Möglichkeiten

- Post

- Potenzial

- Werkzeuge

- größte treibende

- Prozessor

- Produkte

- Projekte

- Protokoll

- Protokolle

- die

- bietet

- Bereitstellung

- schnell

- leicht

- kürzlich

- erkennt

- Redesign

- reduziert

- verhältnismäßig

- Forschungsprojekte

- wiederverwendbar

- Recht

- Ripple

- Rise

- Risiko

- Führen Sie

- s

- sagt

- Skalieren

- Szenarien

- Regelungen

- Abschnitt

- gesehen

- sieht

- Segmente

- Auswahl

- mehrere

- Form

- ,,teilen"

- Einfacher

- da

- Single

- smart

- Lösung

- Lösungen

- einige

- anspruchsvoll

- Spezifikation

- Stufen

- Standard

- einfach

- stark

- Struktur

- Strukturen

- Folge

- Erfolg

- so

- Supermacht

- Technologie

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- ihr

- Diese

- Dritte

- fehlen uns die Worte.

- dachte

- nach drei

- Tier

- Krawatten

- Fester

- Zeit

- zu

- heutigen

- gemeinsam

- Werkzeuge

- Transportwesen

- Auslösen

- UNBENANNT

- aktualisiert

- -

- Nutzer

- Verwendung von

- Wert

- verschiedene

- Variieren

- Anzeigen

- vp

- we

- Webseite

- Was

- Was ist

- wann

- werden wir

- mit

- Arbeiten

- Arbeitsablauf.

- Zephyrnet