Im Laufe der Jahre haben DRC-Tools hervorragende Arbeit geleistet, um mit dem enormen Wachstum der IC-Designgröße Schritt zu halten. Dennoch dauern DRC-Läufe zur Freigabe des vollständigen Entwurfs unter Verwendung von Foundry-Rule-Decks viele Stunden. Diese langen Laufzeiten sind für die endgültige Freigabe akzeptabel, aber es gibt viele Situationen, in denen DRC-Ergebnisse schnell benötigt werden, wenn kleine Änderungen am Design vorgenommen werden, um Probleme in der Spätphase zu beheben. Siemens EDA hat in Zusammenarbeit mit MaxLinear ein Whitepaper verfasst, das zeigt, wie Calibre RealTime Digital In-Design DRC schnell DRC-Ergebnisse liefern kann, wenn kleine Änderungen am Design vorgenommen wurden. Eine schnellere DRC-Abwicklung für lokalisierte Änderungen kann die iterative Fehlerbehebung beschleunigen, die oft erforderlich ist, um ein Tapeout zu erreichen.

In dem Whitepaper mit dem Titel „MaxLinear und Calibre RealTime Digital: Schnellere Signoff-DRC-Konvergenz plus Designoptimierung für Herstellbarkeit“ sprechen MaxLinear und Siemens über die Umstände, unter denen die Möglichkeit besteht, DRC in einem kleinen Bereich eines Designs mit dem vollständigen Foundry-Regelwerk auszuführen Sparen Sie viele Stunden und schmerzhafte langsame Iterationen.

Moderne P&R-Tools leisten hervorragende Arbeit bei der Erstellung eines DRC-richtigen Layouts. Es gibt jedoch immer Fälle, in denen die Ursachen von Verstößen komplexer sind und bei P&R übersehen werden. Diese erfordern in der Regel eine manuelle Korrektur unter Berücksichtigung komplexer Designregeln. Bei diesen manuellen Korrekturen besteht auch die Möglichkeit, dass neue Fehler auftreten. Siemens stellt in dem Whitepaper Informationen von MaxLinear vor, die hervorheben, wie Calibre RealTime Digital in Verbindung mit seinem P&R-Tool es ihnen ermöglicht, manuelle Korrekturen schnell zu implementieren und zu validieren. Die Alternative besteht darin, einen vollständigen DRC-Lauf durchzuführen, um zu sehen, ob die Änderungen in einem kleinen Bereich korrekt sind.

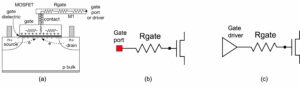

MaxLinear stellt Chips mit analogen und digitalen Blöcken her. Die analogen Blöcke erfordern weniger Metallschichten. Um die Herstellungskosten zu senken, versuchen sie daher, die Routing-Schichten im gesamten Design zu reduzieren. Dies führt zu Problemen mit der Routing-Dichte, die oft im Widerspruch zur Aufrechterhaltung eines hohen DFM-Rankings stehen. Single-Cut-Durchkontaktierungen beanspruchen am wenigsten Platz, tragen aber zu einem niedrigen DFM-Ranking bei. Wenn es darauf ankommt, können MaxLinear-Designer manuell zwischen den Via-Typen wechseln, um Routability- und DFM-Kompromisse zu berücksichtigen. Diese müssen jedoch mit einem umfassenden DRC nachverfolgt werden, um beispielsweise auf Verstöße gegen das Multi-Patterning zu prüfen. Mit Calibre RealTime Digital können Designer zwischen Typen wechseln und dann schnell erkennen, ob DRC-Fehler vorliegen.

Vias sind nicht das einzige Problem, das zu DRC-Problemen führen kann, deren Lösung Zeit und Mühe erfordert. Das Whitepaper beschreibt mehrere Situationen, in denen manuelle Arbeit erforderlich ist und die einzige Möglichkeit, diese Probleme endgültig zu lösen, darin besteht, einen sauberen DRC-Lauf durchzuführen. Eine dieser Situationen, die spät im Prozess auftritt, ist, wenn Re-Tapeout-Prüfungen (RTO) erforderlich sind, um sicherzustellen, dass ECOs mit vorhandenen Masken kompatibel sind. RTO-Regeln sind naturgemäß restriktiver als die ursprünglichen DRC-Regeln.

Das Whitepaper geht auch auf Elektromigrationsprobleme ein, die durch die Verwendung falscher Durchkontaktierungen verursacht werden können. Auch hier war Calibre ReatTime Digital maßgeblich für MaxLinear bei der Implementierung der DRC-Korrektur durch Ersatz verantwortlich. Insgesamt gibt es viele Umstände, die DRC-Prüfungen erfordern, nachdem kleine Änderungen vorgenommen wurden, um Funktions- oder Herstellbarkeitsprobleme in einem Design zu beheben. Die Möglichkeit, sofortige Ergebnisse zu erzielen, anstatt bei einem vollständigen DRC-Durchlauf einen Tag oder länger auf die Bearbeitungszeit warten zu müssen, kann die Projektlaufzeit um Tage oder Wochen verkürzen. Es ist nicht gut, nach einem großen DRC-Lauf Überraschungen zu erleben. Die Siemens Calibre RealTime Digital-Schnittstelle zu P&R-Tools scheint dafür ideal zu sein. Dieses Siemens-Whitepaper finden Sie auf der Siemens EDA-Website.

Teile diesen Beitrag über:

Quelle: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/

- Alle

- Bereich

- Artikel

- verursacht

- Schecks

- Pommes frites

- Konflikt

- Inhalt

- Tag

- Deal

- Design

- digital

- Endlich

- passen

- Fixieren

- Giesserei

- voller

- gut

- Wachstum

- hier

- GUTE

- Ultraschall

- HTTPS

- riesig

- Information

- Probleme

- Job

- Aufbewahrung

- führen

- Lang

- Herstellung

- Masken

- Metall

- Papier

- Projekt

- Veteran

- Die Ergebnisse

- Ohne eine erfahrene Medienplanung zur Festlegung von Regeln und Strategien beschleunigt der programmatische Medieneinkauf einfach die Rate der verschwenderischen Ausgaben.

- Führen Sie

- Siemens

- Größe

- klein

- So

- Raumfahrt

- Geschwindigkeit

- Stufe

- Schalter

- Daumennagel

- Zeit

- Gegen

- Webseite

- WHITE PAPER

- Arbeiten

- Jahr