Im Laufe des Jahrzehnts 2010 begannen die Vorteile des Mooreschen Gesetzes zu schwinden. Das Mooresche Gesetz besagt, dass sich die Transistordichte alle zwei Jahre verdoppelt und die Rechenkosten entsprechend um 50 % sinken würden. Die Änderung des Mooreschen Gesetzes ist auf die zunehmende Designkomplexität bei der Entwicklung der Transistorstruktur von planaren Bauteilen hin zu Finfets zurückzuführen. Finfets benötigen für die Lithographie eine mehrfache Strukturierung, um Gerätedimensionen von unter 20-nm-Knoten zu erreichen.

Zu Beginn dieses Jahrzehnts ist der Computerbedarf explodiert, vor allem aufgrund der zunehmenden Verbreitung von Rechenzentren und der Menge der generierten und verarbeiteten Daten. Tatsächlich werden künstliche Intelligenz (KI) und Techniken wie maschinelles Lernen (ML) heute zur Verarbeitung immer größerer Datenmengen eingesetzt und haben dazu geführt, dass Server ihre Rechenkapazität erheblich steigern.

Server haben viel mehr CPU-Kerne hinzugefügt, größere GPUs integriert, die ausschließlich für ML und nicht mehr für Grafiken verwendet werden, und verfügen über eingebettete benutzerdefinierte ASIC-KI-Beschleuniger oder ergänzende, FPGA-basierte KI-Verarbeitung. Frühe KI-Chipdesigns wurden mit größeren monolithischen SoCs implementiert, von denen einige die durch das Fadenkreuz vorgegebene Größenbeschränkung von etwa 700 mm erreichten2.

An diesem Punkt scheint die Aufteilung in einen kleineren SoC plus verschiedene Compute- und IO-Chiplets die richtige Lösung zu sein. Mehrere Chiphersteller wie Intel, AMD oder Xilinx haben diese Option für Produkte gewählt, die in Produktion gehen. In dem hervorragenden Whitepaper der Linley Group mit dem Titel „Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small“ wurde gezeigt, dass diese Option im Vergleich zu monolithischen SoCs aufgrund der Auswirkung größerer Chips zu geringeren Kosten führt.

Die größten Auswirkungen dieses Trends auf IP-Anbieter betreffen vor allem die Verbindungsfunktionen, die zur Verbindung von SoCs und Chiplets verwendet werden. Zum jetzigen Zeitpunkt (3. Quartal 2021) werden mehrere Protokolle verwendet, und die Branche versucht, für viele davon formalisierte Standards zu entwickeln.

Zu den derzeit führenden D2D-Standards gehören i) Advanced Interface Bus (AIB, AIB2), der ursprünglich von Intel definiert wurde und jetzt eine lizenzgebührenfreie Nutzung bietet, ii) High Bandwidth Memory (HBM), bei dem DRAM-Chips übereinander auf einem Silizium-Interposer gestapelt sind und über TSVs verbunden sind, iii) Die Untergruppe Open Domain-Specific Architecture (ODSA), eine Industriegruppe, hat zwei weitere Schnittstellen definiert, Bunch of Wires (BoW) und OpenHBI.

Das heterogene Chiplet-Design ermöglicht es uns, unterschiedliche Anwendungen oder Marktsegmente anzusprechen, indem wir nur die relevanten Chiplets modifizieren oder hinzufügen, während der Rest des Systems unverändert bleibt. Neue Entwicklungen könnten schneller und mit deutlich geringeren Investitionen auf den Markt gebracht werden, da sich die Neugestaltung nur auf das Gehäusesubstrat auswirkt, das zur Unterbringung der Chiplets verwendet wird.

Beispielsweise kann das Rechenchiplet von TSMC 5 nm auf TSMC 3 nm umgestaltet werden, um einen größeren L1-Cache oder leistungsstärkere CPU-Kerne zu integrieren, während der Rest des Systems unverändert bleibt. Am anderen Ende des Spektrums kann nur das Chiplet, das SerDes integriert, für schnellere Raten auf neuen Prozessknoten umgestaltet werden, die mehr IO-Bandbreite für eine bessere Marktpositionierung bieten.

Intel PVC ist ein perfektes Beispiel für heterogene Integration (verschiedene funktionale Chiplets, CPUs, Switches usw.), die wir als vertikale Integration bezeichnen könnten, wenn derselbe Chiphersteller die verschiedenen Chiplet-Komponenten besitzt (mit Ausnahme von Speichergeräten).

Chiphersteller, die SoCs für High-End-Anwendungen wie HPC, Rechenzentren, KI oder Netzwerke entwickeln, dürften zu den ersten Anwendern von Chiplet-Architekturen gehören. Spezifische Funktionen, wie SRAMs für größeren L3-Cache oder KI-Beschleuniger, entweder Ethernet-, PCIe- oder CXL-Standards, sollten die ersten Schnittstellenkandidaten für Chiplet-Designs sein.

Wenn diese frühen Anwender die Gültigkeit heterogener Chiplets, die mehrere unterschiedliche Geschäftsmodelle nutzen, und natürlich die Machbarkeit der Herstellung für Tests und Verpackungen unter Beweis gestellt haben, wird ein Ökosystem geschaffen sein, das für die Unterstützung dieser neuen Technologie von entscheidender Bedeutung ist. An diesem Punkt können wir mit einer breiteren Marktakzeptanz rechnen, nicht nur für Hochleistungsanwendungen.

Wir könnten uns vorstellen, dass heterogene Produkte noch weiter gehen können, wenn ein Chiphersteller ein System aus verschiedenen Chiplets auf den Markt bringt, das auf Rechen- und IO-Funktionalität abzielt. Dieser Ansatz macht die Konvergenz auf ein D2D-Protokoll zwingend erforderlich, da ein IP-Anbieter, der Chiplets mit einem hauseigenen D2D-Protokoll anbietet, für die Branche nicht attraktiv ist.

Eine Analogie dazu ist das SoC-Gebäude in den 2000er Jahren, als Halbleiterunternehmen dazu übergingen, verschiedene Design-IPs aus unterschiedlichen Quellen zu integrieren. Die IP-Anbieter der 2000er Jahre werden unweigerlich zu den Chiplet-Anbietern der 2020er Jahre. Für bestimmte Funktionen, wie zum Beispiel erweiterte SerDes oder komplexe Protokolle wie PCIe, Ethernet oder CXL, verfügen IP-Anbieter über das beste Know-how, um sie auf Silizium zu implementieren.

Bei komplexer Design-IP müssen Anbieter die IP auf Silizium validieren, um die Leistung zu gewährleisten, auch wenn vor der Auslieferung an Kunden eine Simulationsverifizierung durchgeführt wurde. Für digitales IP kann die Funktion im FPGA implementiert werden, da dies schneller und weitaus kostengünstiger ist als die Herstellung eines Testchips. Für Mixed-Signal-IP, wie z. B. ein SerDes-basiertes PHY, wählen Anbieter die Test-Chip-Option (TC), die es ihnen ermöglicht, das IP im Silizium vor dem Versand an den Kunden zu charakterisieren.

Auch wenn es sich bei einem Chiplet nicht einfach um einen TC handelt, da er vor dem Einsatz im Feld umfassend getestet und qualifiziert wird, ist der Umfang der zusätzlichen Arbeit, die der Anbieter für die Entwicklung eines Serien-Chiplets leisten muss, weitaus geringer. Mit anderen Worten: Der IP-Anbieter ist am besten in der Lage, schnell ein Chiplet freizugeben, das aus seinem eigenen IP erstellt wurde, das bestmögliche TTM anzubieten und das Risiko zu minimieren.

Das Geschäftsmodell für heterogene Integration begünstigt seitdem die Herstellung verschiedener Chiplets durch den jeweiligen IP-Anbieter (z. B. ARM für ARM-basierte CPU-Chiplets, Si-Five für Risc-V-basierte Rechenchiplets und Alphawave für Hochgeschwindigkeits-SerDes-Chiplets). Sie sind Inhaber des Design-IP.

Nichts davon hindert Chiphersteller daran, ihre eigenen Chiplets zu entwerfen und komplexe Design-IPs zu beschaffen, um ihre einzigartigen Architekturen zu schützen oder hausgemachte Verbindungen zu implementieren. Ähnlich wie beim SoC Design IP in den 2000er Jahren wird die Kauf- oder Herstellungsentscheidung für Chiplets zwischen dem Schutz der Kernkompetenzen und der Beschaffung nicht differenzierender Funktionen abgewogen.

Wir haben gesehen, dass das historische und moderne Wachstum des Design-IP-Geschäfts seit den 2000er Jahren durch die kontinuierliche Einführung externer Beschaffung aufrechterhalten wurde. Beide Modelle werden nebeneinander existieren (Chiplet selbst entwickelt oder von einem IP-Anbieter), aber die Geschichte hat gezeigt, dass die Kaufentscheidung letztendlich Vorrang vor der Marke hat.

In der Branche besteht inzwischen Konsens darüber, dass ein wahnsinniger Fokus auf die Umsetzung des Mooreschen Gesetzes für fortschrittliche Technologieknoten nicht mehr gültig ist, z. 7 nm und darunter. Die Chip-Integration findet immer noch statt, wobei an jedem neuen Technologieknoten mehr Transistoren pro Quadratmillimeter hinzugefügt werden. Allerdings steigen auch die Kosten pro Transistor mit jedem neuen Knoten.

Die Chiplet-Technologie ist eine Schlüsselinitiative, um die Integration des Haupt-SoC voranzutreiben und gleichzeitig ältere Knoten für andere Funktionen zu nutzen. Diese Hybridstrategie verringert sowohl die Kosten als auch das Designrisiko, das mit der Integration anderer Design-IP direkt in das Haupt-SoC verbunden ist.

IPnest geht davon aus, dass dieser Trend zwei wesentliche Auswirkungen auf das Schnittstellen-IP-Geschäft haben wird: Zum einen wird es bald ein starkes Wachstum der D2D-IP-Umsätze geben (2021–2025) und zum anderen wird es die Schaffung eines heterogenen Chiplet-Marktes zur Ergänzung des High-End-Siliziums geben IP-Markt.

Es wird erwartet, dass dieser Markt aus komplexen Protokollfunktionen wie PCIe, CXL oder Ethernet besteht. IP-Anbieter, die in I/O-SoCs (USB, HDMI, DP, MIPI usw.) integrierte Schnittstellen-IP bereitstellen, entscheiden sich möglicherweise dafür, stattdessen I/O-Chiplets zu liefern.

Die anderen IP-Kategorien, die von dieser Revolution betroffen sind, werden IP-Anbieter von SRAM-Speicher-Compilern für L3-Cache sein. Naturgemäß ist zu erwarten, dass die Cache-Größe je nach Prozessor variiert. Dennoch kann die Entwicklung eines L3-Cache-Chiplets für IP-Anbieter eine Möglichkeit sein, die Einnahmen aus dem Design von IP durch das Angebot eines neuen Produkttyps zu steigern.

Auch die NVM-IP-Kategorie kann positiv beeinflusst werden, da NVM-IP nicht mehr in SoCs integriert ist, die auf fortschrittlichen Prozessknoten entwickelt wurden. Dies wäre eine Möglichkeit für NVM-IP-Anbieter, durch das Angebot von Chiplets neue Geschäfte zu generieren.

Wir glauben, dass FPGA- und KI-Beschleuniger-Chiplets eine neue Einnahmequelle für ASSP-Chiphersteller sein werden, glauben aber nicht, dass sie streng genommen als IP-Anbieter eingestuft werden können.

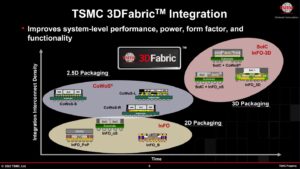

Wenn Schnittstellen-IP-Anbieter wichtige Akteure dieser Silizium-Revolution sein werden, werden auch die Silizium-Foundries, die die fortschrittlichsten Knoten bedienen, wie TSMC und Samsung, eine Schlüsselrolle spielen. Wir glauben nicht, dass Foundries Chiplets entwickeln werden, aber sie könnten die Entscheidung treffen, IP-Anbieter zu unterstützen und sie dazu zu drängen, Chiplets für die Verwendung mit SoCs in 3 nm zu entwickeln, so wie sie es heute tun, wenn sie fortschrittliche IP-Anbieter bei der Vermarktung ihrer High-End-SerDes unterstützen als Hard IP in 7nm und 5nm.

Intels jüngster Übergang zu 3rd Es wird erwartet, dass Party-Foundries auch IPs von Drittanbietern sowie die Einführung heterogener Chiplets durch Halbleiter-Schwergewichte nutzen werden. In diesem Fall besteht kein Zweifel daran, dass Hyperskalare wie Microsoft, Amazon und Google ebenfalls Chiplet-Architekturen übernehmen werden … wenn sie Intel bei der Chiplet-Einführung nicht voraus sind.

By Eric Esteve (PhD.) Analyst, Inhaber IPnest

Teile diesen Beitrag über: Quelle: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- Beschleuniger

- Beschleuniger

- Adoption

- Fortschrittliche Technologie

- AI

- Zulassen

- Amazon

- AMD

- Analytiker

- Anwendungen

- Architektur

- ARM

- künstliche Intelligenz

- Künstliche Intelligenz (AI)

- ASIC

- BESTE

- bauen

- Building

- Haufen

- Bus

- Geschäft

- Geschäftsmodell

- Kaufe

- rufen Sie uns an!

- Kapazität

- Übernehmen

- Chip

- Pommes frites

- Kommen

- Unternehmen

- Berechnen

- Computing

- Konsens

- Kosten

- Kunden

- technische Daten

- liefern

- Design

- entwickeln

- Geräte

- digital

- Früh

- frühzeitige Anwender

- Ökosystem

- etc

- Evolution

- Vorname

- Setzen Sie mit Achtsamkeit

- FPGA

- Frei

- Funktion

- GPUs

- Gruppe an

- persönlichem Wachstum

- Wachstum

- GUTE

- Geschichte

- Häuser

- HTTPS

- Hybrid

- Impact der HXNUMXO Observatorien

- Erhöhung

- Energiegewinnung

- Initiative

- Integration

- Intel

- Intelligenz

- Investition

- IP

- IT

- Aufbewahrung

- Wesentliche

- starten

- Recht

- führenden

- lernen

- geführt

- Hebelwirkung

- LINK

- Maschinelles Lernen

- Dur

- Hersteller

- Making

- Herstellung

- Markt

- Microsoft

- ML

- Modell

- Vernetzung

- neue Produkt

- Fiber Node

- bieten

- bieten

- XNUMXh geöffnet

- Option

- Andere

- Eigentümer

- Verpackung

- Papier

- Leistung

- Produkt

- Produktion

- Produkte

- Risiken zu minimieren

- Sicherheit

- Honorar

- Redesign

- REST

- Risiko

- Führen Sie

- Samsung

- Halbleiter

- Versand

- Simulation

- Größe

- Normen

- Strategie

- Support

- Schalter

- System

- Target

- Techniken

- Technologie

- Test

- Top

- us

- USB

- Anbieter

- Verification

- WHITE PAPER

- Worte

- Arbeiten

- Jahr

- Ausbeute