模拟 IC 设计人员可能会花费太多时间和精力重复使用旧的、熟悉的手动迭代方法进行电路设计,只是因为它一直都是这样做的。 电路优化是一种 EDA 方法,它可以通过跨 PVT 角和工艺变化运行 SPICE 仿真来自动调整单元中所有晶体管的大小,以满足模拟和混合信号设计要求。 听起来很有希望,对吧?

那么我应该考虑使用哪种电路优化器?

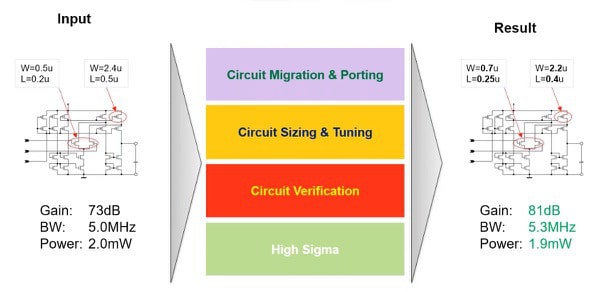

为了回答这个问题,即将举办一个网络研讨会,由 宗立达,一家 EDA 公司成立于 2001 年,他们的电路优化器名为 邪恶. 输入是 SPICE 网表以及设计要求,例如:增益、带宽和功耗。 输出是一个大小符合或超过设计要求的网表。

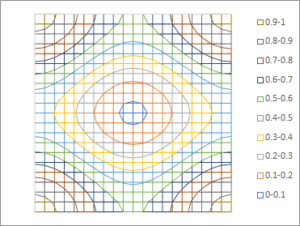

WiCkeD 的秘诀在于它如何建立机器学习 (ML) 模型来运行实验设计 (DOE) 来计算最坏情况下的 PVT 拐角,找到晶体管几何形状的敏感性,甚至计算片上变化 (OCV) )敏感性。 这种方法根据模拟数据创建和更新非线性、高维 ML 模型。

拥有 ML 模型使该工具能够解决优化挑战,然后通过运行 SPICE 仿真进行最终验证。 在满足所有要求之前,会进行自动迭代。 现在这听起来比旧的手动迭代方法快得多。 训练 ML 模型是完全自动的,而且非常高效。

电路设计师还将学习:

- 电路优化用在哪里

- 什么类型的电路好优化

- 电路优化给设计流程带来多少价值

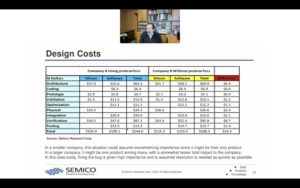

STMicroelectronics 的工程师使用了 WiCkeD 中的电路优化,MunEDA 谈到了他们在节省时间和改进满足要求方面的具体结果。 功率放大器公司Inplay Technologies展示了DAC 2018会议的电路优化结果。

网络研讨会详情

查看太平洋夏令时间 11 月 10 日上午 XNUMX 点的网络研讨会 在线注册.

相关博客

通过以下方式分享此帖子:- SEO 支持的内容和 PR 分发。 今天得到放大。

- 柏拉图区块链。 Web3 元宇宙智能。 知识放大。 访问这里。

- Sumber: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :是

- $UP

- 2001

- 2018

- a

- 关于我们

- 横过

- 所有类型

- 时刻

- 和

- 回答

- 的途径

- 四月

- 保健

- At

- 自动化

- 自动表

- 自动

- 背部

- 带宽

- 因为

- 带来

- 建立

- by

- 计算

- CAN

- 挑战

- 芯片

- 未来

- 公司

- 研讨会 首页

- 考虑

- 消费

- 角落

- 角落

- 创建

- data

- 设计

- 设计师

- 美国能源部

- 高效

- 努力

- 使

- 甚至

- 超过

- 熟悉

- 快

- 最后

- 找到最适合您的地方

- 流

- 针对

- 止

- Gain增益

- 几何

- 非常好

- 有

- 托管

- 创新中心

- HTTPS

- i

- 改善

- in

- IT

- 迭代

- 迭代

- JPG

- 学习用品

- 学习

- 喜欢

- 机

- 机器学习

- 手册

- 最大宽度

- 满足

- 会议

- 会见

- 方法

- ML

- 模型

- 命名

- of

- 老

- on

- 优化

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 帖子

- 功率

- 过程

- 生产率

- 有希望

- 题

- 岗位要求

- 成果

- 运行

- 运行

- 储

- 秘密

- 应该

- 模拟

- 尺寸

- 具体的

- 花

- 香料

- 开始

- 会谈

- 技术

- 这

- 其

- 次

- 至

- 也有

- 工具

- 产品培训

- 类型

- 最新动态

- 使用

- 折扣值

- 企业验证

- 通过

- 方法..

- 网络研讨会

- 这

- 将

- 和风网