设计人员有多种途径来实现 RISC-V 解决方案的差异化。 一种途径是根据规范启动各种 RISC-V 核心定制和扩展。 另一个重点是在围绕一个或多个 RISC-V 内核的完整片上系统 (SoC) 设计中选择和组装 IP 模块。 第三种正在兴起:使用片上网络 (NoC) 而不是简单的总线结构互连 RISC-V 内核和其他 IP 块。 不仅仅是高端领域,RISC-V 内核与 NoC 的配对解决了许多 SoC 设计挑战,其中数据必须使用任何片上协议在任何工作负载中高效流动。

性能层随着先进的互连方案而变化

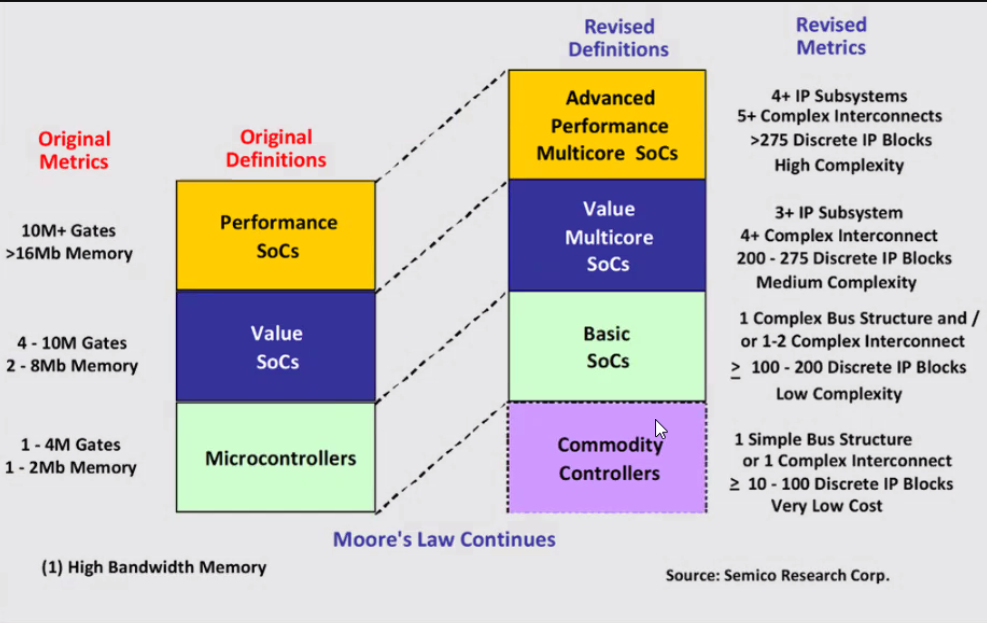

简单地计算门、内核和外围模块不再描述 SoC 设计的性能潜力。 Semico Research 表示,互连方案现在定义了 SoC 性能层之间的界限,并且新的层已经开放,其中互连从简单的总线结构变为更复杂的方案。

Semico 的更新定义承认了三种作用力:多核设计的普遍性、复杂设计的更高标准以及随后“微控制器”和“SoC”之间的模糊界限。 在 Semico 的最新观点中,门计数作为一种度量的概念消失了,因为一个现代处理器核心可以拖动许多门。 复杂性成为互连的函数,随着子系统和不同的 IP 块的不同而变化。

SoC 性能等级,图片由 Semico Research Corp. 提供

在简单的总线可以实现的地方,可能是具有单个处理器核心和低占空比外设的部件,这些外设不会持续竞争总线,Semico 看到了商品控制器层。 以上的任何东西都会成为 SoC,大概至少有一些外设争夺片上带宽和处理器核心的关注。 更高的 SoC 层具有多个内核和多个 IP 子系统,每个子系统都具有经过调整的互连技术。

NoC 采用更多协议和子系统

随着更强大的内核的出现,RISC-V 迅速提升了这些性能级别,在 Semico 规模的低端的适用性也丝毫不减。 然而,RISC-V 设计人员在较高层的复杂互连方案方面可能缺乏经验。 “TileLink 可能是 RISC-V 互连的第一个想法,但它可能很难在更复杂的场景中使用,”Arteris 解决方案和业务开发副总裁 Frank Schirrmeister 表示。

NoC 的超能力在于其使用不同协议连接子系统的能力,SoC 设计人员甚至可能会遇到多种复杂程度适中的协议。 AXI 为简单的 IP 块连接提供了公平的竞争环境。 具有协同处理块的多核解决方案需要缓存一致性,从而催生了 CHI 协议。 I/O 内存共享有助于形成更快的 CXL 互连。 “当需要与各种子系统和协议共同优化计算和传输时,NoC 是更好的解决方案,”Schirrmeister 继续说道。

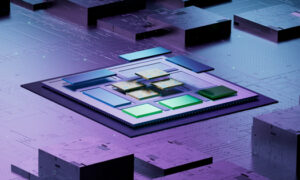

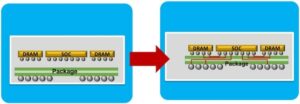

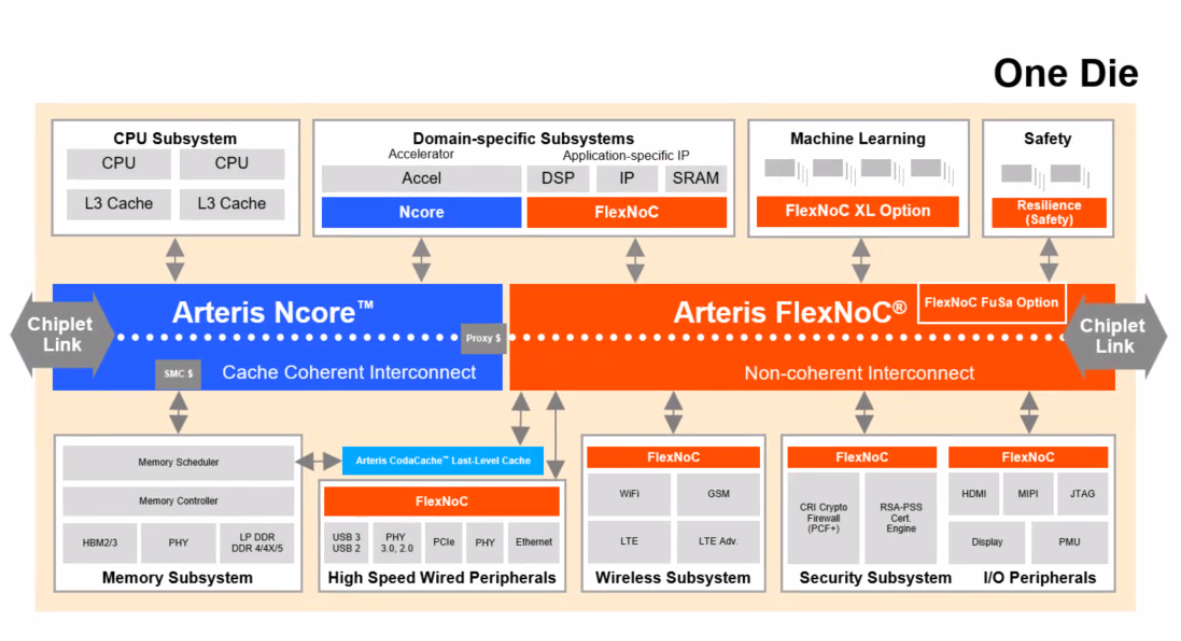

RISC-V 内核与 NoC 的配对会是什么样子? Arteris 客户 Tenstorrent 让我们得以一睹这种可能性。 他们最近的重点是创建一个可重复使用的小芯片,结合了 RISC-V 内核、机器学习加速 IP 和许多边缘 AI 应用中的标准外设。 从规模上看,单芯片实现可能如下图所示,使用 Arteris Ncore 缓存一致性互连和 Arteris FlexNoC 非一致性互连的多个部分。

图片由阿特里斯提供

智能内存控制器 (SMC) 在内存密集型应用中提供高性能、服务器级内存连接。 未命名的“小芯片链路”可能是 UCIe,这是一种针对更紧密的小芯片集成而优化的相对较新的规范。 当新的子系统互连出现时,调整片上网络的一部分比拆除整个芯片范围的结构更容易管理。

将 RISC-V 内核与 NoC 配对可降低风险并缩短上市时间

如果该图看起来很复杂,当然,也许大多数 RISC-V 应用现在并不那么复杂,请考虑一下:小芯片已经在推动集成度更高。 随着创新步伐的加快,当今先进的 RISC-V 多核部件将成为明年的价值 SoC。

Arteris Ncore 和 Arteris FlexNoC 开发工具输出 RTL 进行实施,具有多种优势。 物理 NoC 估计在 EDA 工作流程中非常简单。 NoC 参数调整(例如管道级数)也只需在 EDA 工具中单击几下即可完成。 上述用于添加子系统协议的修改也很容易完成。 “在高端,用户可以立即获得我们的 NoC 专业知识,”Schirrmeister 说道。 “在低端,我们的工具易于使用,可以一次性成功,并为具有复杂互连的更雄心勃勃的未来项目提供增长路径。”

将 RISC-V 内核与 NoC 配对可以降低多一个 IP 块进入设计并触发整个芯片互连重新设计的风险。 与 DIY 互连结构相比,它还缩短了复杂 SoC 设计的上市时间。 我们在这里没有讨论 NoC 的其他优势,例如带宽和电源管理,但考虑到不同的协议组合,RISC-V 设计中的 NoC 的情况就很充分。

访问 Arteris 网站 有关 NoC 的更多信息 和其他产品。

通过以下方式分享此帖子:

- :具有

- :是

- :不是

- :在哪里

- $UP

- a

- 对,能力--

- 以上

- 促进

- ACCESS

- 完成

- 根据

- 横过

- 添加

- 调整

- 高级

- 优点

- AI

- 已经

- 还

- 有雄心

- an

- 和

- 另一个

- 答案

- 任何

- 什么

- 出现

- 应用领域

- 保健

- 围绕

- AS

- At

- 关注我们

- 远离

- 带宽

- 酒吧

- BE

- 成为

- 好处

- 更好

- 之间

- 阻止

- 吹氣梢

- 总线

- 商业

- 业务发展

- 但是

- CAN

- 案件

- 挑战

- 更改

- 改变

- 芯片

- 结合

- 商品

- 相比

- 完成

- 复杂

- 复杂

- 计算

- 分享链接

- 地都

- 连接

- 考虑

- 考虑

- 考虑

- 继续

- 一直

- 调节器

- 核心

- 公司

- 可以

- 计数

- 创造

- 顾客

- data

- 定义

- 定义

- 需求

- 设计

- 设计师

- 设计

- 研发支持

- 开发工具

- 不同

- 难

- 讨论

- 不同

- do

- 驾驶

- 每

- 易

- 边缘

- 有效

- 出现

- 新兴经济体的新市场。

- 结束

- 进入

- 整个

- 甚至

- 体验

- 专门知识

- 扩展

- 快

- 少数

- 部分

- 战斗

- 姓氏:

- 流

- 专注焦点

- 重点

- 以下

- 针对

- 部队

- 发现

- 坦率

- 止

- 功能

- 未来

- Gain增益

- 盖茨

- 给予

- 一瞥

- 授予

- 事业发展

- 有

- 帮助

- 此处

- 高

- 高性能

- 更高

- 但是

- HTTPS

- 图片

- 即时

- 履行

- in

- 信息

- 創新

- 代替

- 积分

- 互连

- 互连

- 成

- IP

- IT

- 它的

- 只是

- 最新

- 启动

- 最少

- 减

- 喜欢

- 容易

- Line

- 线

- 不再

- 看

- 看起来像

- LOOKS

- 低

- 降低

- 颠覆性技术

- 许多

- 最大宽度

- 可能..

- 也许

- 内存

- 提到

- 公

- 混合

- 中度

- 现代

- 修改

- 更多

- 最先进的

- 移动

- 许多

- 多

- 必须

- 全新

- 下页

- 没有

- 概念

- 现在

- 数

- of

- on

- 一

- 打开

- 优化

- or

- 其他名称

- 我们的

- 产量

- 步伐

- 配对

- 参数

- 部分

- 径

- 为

- 性能

- 外围设备

- 外围设备

- 的

- 挑

- 精选

- 管道

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 播放

- 播放

- 可能性

- 帖子

- 潜力

- 功率

- 强大

- 处理器

- 热销产品

- 项目

- 协议

- 协议

- 提供

- 提供

- 优

- 很快

- 容易

- 最近

- 认识

- 重新设计

- 减少

- 相对

- 研究

- 可重复使用

- 右

- 纹波

- 上升

- 风险

- 运行

- s

- 说

- 鳞片

- 情景

- 方案

- 部分

- 看到

- 看到

- 中模板

- 选择

- 几个

- 形状

- 共享

- 简易

- 自

- 单

- 智能

- 方案,

- 解决方案

- 一些

- 极致

- 规范

- 实习

- 标准

- 简单的

- 强烈

- 结构体

- 结构

- 随后

- 成功

- 这样

- 超级大国

- 专业技术

- 比

- 这

- 其

- 博曼

- 第三

- Free Introduction

- 思想

- 三

- 一线

- 领带

- 更紧

- 次

- 至

- 今天的

- 一起

- 工具

- 运输

- 触发

- 无名

- 更新

- 使用

- 用户

- 运用

- 折扣值

- 各个

- 变化

- 通过

- 查看

- vp

- we

- 您的网站

- 什么是

- 什么是

- ,尤其是

- 将

- 工作

- 工作流程

- 和风网