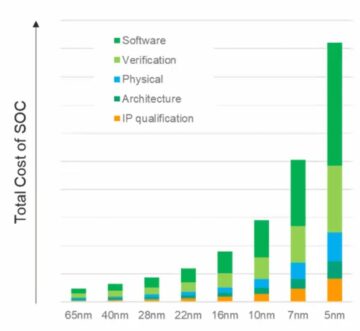

زیادہ قابل، تیز، چھوٹے اور کم پاور سسٹم کی طرف مارچ میں، مور کے قانون نے سافٹ ویئر کو 30 سال سے زیادہ یا اس سے زیادہ کے لیے مکمل طور پر سیمی کنڈکٹر کے عمل کے ارتقاء پر مفت سفر فراہم کیا۔ کمپیوٹ ہارڈویئر نے ہر سال بہتر کارکردگی/رقبہ/پاور میٹرکس فراہم کیے، جس سے سافٹ ویئر کو پیچیدگی میں وسعت ملتی ہے اور بغیر کسی کمی کے زیادہ صلاحیت فراہم ہوتی ہے۔ پھر آسان جیت کم آسان ہو گئی۔ مزید ترقی یافتہ عمل فی یونٹ رقبہ میں زیادہ گیٹ گنتی فراہم کرتے رہے لیکن کارکردگی اور طاقت میں فائدہ کم ہونا شروع ہوگیا۔ چونکہ جدت طرازی کے لیے ہماری توقعات ختم نہیں ہوئیں، اس لیے ہارڈ ویئر کے فن تعمیر کی ترقی سستی کو اٹھانے میں زیادہ اہم ہو گئی ہے۔

کور کاؤنٹ بڑھانے کے لیے ڈرائیورز

اس سمت میں ایک ابتدائی قدم نے ملٹی کور CPUs کا استعمال کیا تاکہ کوروں میں ہم آہنگی کے کاموں کے مرکب کو تھریڈنگ یا ورچوئلائز کرکے کل تھرو پٹ کو تیز کیا جاسکے، غیر فعال کور کو سست یا پاور ڈاون کرکے ضرورت کے مطابق طاقت کو کم کیا جائے۔ ملٹی کور آج معیاری ہے اور AWS، Azure، Alibaba اور دیگر کے کلاؤڈ پلیٹ فارمز میں دستیاب سرور مثال کے اختیارات میں کئی کور (چپ پر اس سے بھی زیادہ CPUs) کا رجحان پہلے سے ہی واضح ہے۔

ملٹی/مینی کور آرکیٹیکچرز ایک قدم آگے ہیں، لیکن سی پی یو کلسٹرز کے ذریعے ہم آہنگی موٹے دانے والی ہے اور اس کی اپنی کارکردگی اور طاقت کی حدیں ہیں، امڈاہل کے قانون کی بدولت۔ آرکیٹیکچرز زیادہ متضاد بن گئے، جس میں امیج، آڈیو اور دیگر خصوصی ضروریات کے لیے ایکسلریٹر شامل ہوئے۔ AI ایکسلریٹرس نے بھی ٹھیک دانے دار ہم آہنگی کو آگے بڑھایا ہے، سسٹولک صفوں اور دیگر ڈومین مخصوص تکنیکوں کی طرف بڑھ رہے ہیں۔ جو اس وقت تک بہت اچھا کام کر رہا تھا جب تک کہ ChatGPT 175 بلین پیرامیٹرز کے ساتھ GPT-3 کے ساتھ GPT-4 میں 100 ٹریلین پیرامیٹرز کے ساتھ نمودار ہوا – جس کی شدت کے آرڈر آج کے AI سسٹمز سے زیادہ پیچیدہ ہیں – AI ایکسلریٹر کے اندر مزید خصوصی ایکسلریشن خصوصیات کو مجبور کر رہے ہیں۔

ایک مختلف محاذ پر، آٹوموٹو ایپلی کیشنز میں ملٹی سینسر سسٹمز اب بہتر ماحول کی آگاہی اور بہتر PPA کے لیے سنگل SoCs میں ضم ہو رہے ہیں۔ یہاں، آٹوموٹیو میں خودمختاری کی نئی سطحیں 2X، 4X یا 8X کے ذریعے نقل کرنے والے ذیلی نظاموں میں، ایک ہی ڈیوائس کے اندر متعدد سینسر کی اقسام کے فیوز ان پٹ پر منحصر ہیں۔

Michał Siwinski (CMO at Arteris) کے مطابق، ایپلی کیشنز کی ایک وسیع رینج میں متعدد ڈیزائن ٹیموں کے ساتھ ایک ماہ کے دوران ہونے والی بات چیت کے نمونے لینے سے پتہ چلتا ہے کہ وہ ٹیمیں قابلیت، کارکردگی اور طاقت کے اہداف کو پورا کرنے کے لیے فعال طور پر اعلیٰ بنیادی شماروں کی طرف رجوع کر رہی ہیں۔ وہ مجھے بتاتا ہے کہ وہ بھی اس رجحان میں تیزی دیکھ رہے ہیں۔ عمل میں پیشرفت اب بھی SoC گیٹ کی گنتی میں مدد کرتی ہے، لیکن کارکردگی اور طاقت کے اہداف کو پورا کرنے کی ذمہ داری اب آرکیٹیکٹس کے ہاتھ میں ہے۔

مزید کور، زیادہ باہم مربوط

ایک چپ پر زیادہ کور ان کوروں کے درمیان زیادہ ڈیٹا کنکشن کا مطلب ہے۔ ہمسایہ پروسیسنگ عناصر کے درمیان ایک ایکسلریٹر کے اندر، مقامی کیشے تک، اسپارس میٹرکس اور دیگر خصوصی ہینڈلنگ کے لیے ایکسلریٹر تک۔ ایکسلریٹر ٹائلز اور سسٹم لیول بسوں کے درمیان درجہ بندی کا رابطہ شامل کریں۔ آن چپ ویٹ اسٹوریج، ڈیکمپریشن، براڈکاسٹ، جمع اور دوبارہ کمپریشن کے لیے کنیکٹیویٹی شامل کریں۔ کام کرنے والے کیشے کے لیے HBM کنیکٹیویٹی شامل کریں۔ اگر ضرورت ہو تو فیوژن انجن شامل کریں۔

CPU پر مبنی کنٹرول کلسٹر کو ان میں سے ہر ایک نقل شدہ ذیلی نظام سے اور تمام معمول کے افعال سے جڑنا ضروری ہے - کوڈیکس، میموری مینجمنٹ، حفاظتی جزیرہ اور اگر مناسب ہو تو اعتماد کی جڑ، UCIe اگر ملٹی چپلیٹ نفاذ، اعلی بینڈوتھ I/O کے لیے PCIe ، اور نیٹ ورکنگ کے لیے ایتھرنیٹ یا فائبر۔

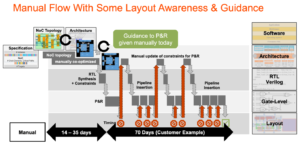

یہ بہت زیادہ آپس میں جڑا ہوا ہے، جس کے براہ راست نتائج پروڈکٹ کی مارکیٹ ایبلٹی کے ہیں۔ 16nm سے نیچے کے عمل میں، NoC انفراسٹرکچر اب رقبے میں 10-12% کا حصہ ڈالتا ہے۔ اس سے بھی زیادہ اہم، کور کے درمیان مواصلاتی شاہراہ کے طور پر، یہ کارکردگی اور طاقت پر نمایاں اثر ڈال سکتا ہے۔ اس بات کا حقیقی خطرہ ہے کہ ایک ذیلی زیادہ سے زیادہ نفاذ متوقع فن تعمیر کی کارکردگی اور طاقت کے فوائد کو ضائع کردے گا، یا اس سے بھی بدتر، نتیجے میں متعدد ری ڈیزائن لوپس آپس میں مل جائیں گے۔ اس کے باوجود ایک پیچیدہ SoC فلورپلان میں ایک اچھا نفاذ تلاش کرنا اب بھی پہلے سے سخت ڈیزائن کے نظام الاوقات میں سست آزمائش اور غلطی کی اصلاح پر منحصر ہے۔ ہمیں NoC ڈیزائن کو جسمانی طور پر آگاہ کرنے کی ضرورت ہے، تاکہ پیچیدہ NoC درجہ بندیوں سے مکمل کارکردگی اور پاور سپورٹ کی ضمانت دی جا سکے اور ہمیں ان اصلاحات کو تیز تر بنانے کی ضرورت ہے۔

جسمانی طور پر آگاہ NoC ڈیزائن مور کے قانون کو ٹریک پر رکھتے ہیں۔

مور کا قانون شاید مردہ نہ ہو لیکن آج کارکردگی اور طاقت میں پیشرفت عمل سے ہونے کی بجائے فن تعمیر اور NoC ایک دوسرے سے جڑی ہوئی ہے۔ آرکیٹیکچر زیادہ ایکسلریٹر کورز، ایکسلریٹر کے اندر زیادہ ایکسلریٹر، اور زیادہ سب سسٹم ریپلیکشن آن چپ کو آگے بڑھا رہا ہے۔ سبھی آن چپ انٹرکنیکٹ کی پیچیدگی میں اضافہ کرتے ہیں۔ جیسا کہ ڈیزائن بنیادی تعداد میں اضافہ کرتے ہیں اور 16nm اور اس سے نیچے جیومیٹریز پر کارروائی کرتے ہیں، SoC اور اس کے ذیلی نظاموں پر پھیلے ہوئے متعدد NoC آپس میں جڑے ہوئے ہیں صرف ان پیچیدہ ڈیزائنوں کی مکمل صلاحیت کی حمایت کر سکتے ہیں اگر جسمانی اور وقت کی پابندیوں کے خلاف بہترین طور پر لاگو کیا جائے - جسمانی طور پر آگاہ نیٹ ورک کے ذریعے۔ چپ ڈیزائن پر.

اگر آپ بھی ان رجحانات کے بارے میں فکر مند ہیں، تو آپ Arteris FlexNoC 5 IP ٹیکنالوجی کے بارے میں مزید جان سکتے ہیں۔ HERE.

اس پوسٹ کو بذریعہ شیئر کریں:

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو بلاک چین۔ Web3 Metaverse Intelligence. علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- : ہے

- $UP

- 100

- a

- ہمارے بارے میں

- رفتار کو تیز تر

- تیز

- تیزی

- مسرع

- ایکسلریٹر

- کے پار

- فعال طور پر

- اعلی درجے کی

- ترقی

- کے خلاف

- AI

- اے آئی سسٹمز

- Alibaba

- تمام

- اجازت دے رہا ہے

- پہلے ہی

- اور

- شائع ہوا

- ایپلی کیشنز

- مناسب

- فن تعمیر

- کیا

- رقبہ

- AS

- At

- آڈیو

- آٹوموٹو

- دستیاب

- کے بارے میں شعور

- AWS

- Azure

- بینڈوڈتھ

- BE

- بن

- نیچے

- کے درمیان

- ارب

- نشر

- بسیں

- by

- کیشے

- کر سکتے ہیں

- صلاحیت رکھتا

- چیٹ جی پی ٹی

- چپ

- بادل

- کلسٹر

- CMO

- کس طرح

- مواصلات

- پیچیدہ

- پیچیدگی

- کمپیوٹنگ

- سمورتی

- رابطہ قائم کریں

- کنکشن

- رابطہ

- نتائج

- رکاوٹوں

- جاری رہی

- کنٹرول

- تقارب

- کور

- CPU

- خطرے

- اعداد و شمار

- مردہ

- نجات

- ڈیلیور

- انحصار کرتا ہے

- ڈیزائن

- ڈیزائن

- آلہ

- مختلف

- براہ راست

- سمت

- بات چیت

- نیچے

- نیچے کی طرف

- ہر ایک

- ابتدائی

- عناصر

- انجن

- ماحولیات

- بھی

- ہر کوئی

- ارتقاء

- تیار ہوتا ہے

- توسیع

- توقعات

- توقع

- تیز تر

- خصوصیات

- تلاش

- مضبوطی سے

- کے لئے

- آگے

- مفت

- سے

- سامنے

- مکمل

- افعال

- فیوژن

- فوائد

- اہداف

- اچھا

- اس بات کی ضمانت

- ہینڈلنگ

- ہاتھوں

- ہارڈ ویئر

- ہے

- مدد

- یہاں

- ہائی

- اعلی

- ہائی وے

- HTTPS

- تصویر

- اثر

- نفاذ

- عملدرآمد

- اہم

- بہتر

- in

- غیر فعال

- اضافہ

- اضافہ

- انفراسٹرکچر

- جدت طرازی

- مثال کے طور پر

- انضمام کرنا

- IP

- جزائر

- IT

- میں

- کودنے

- قانون

- جانیں

- سطح

- سطح

- حدود

- مقامی

- بہت

- بنا

- انتظام

- مارچ

- میٹرکس

- زیادہ سے زیادہ چوڑائی

- سے ملو

- اجلاس

- یاد داشت

- پیمائش کا معیار

- شاید

- مہینہ

- زیادہ

- منتقل

- منتقل

- ایک سے زیادہ

- ضرورت ہے

- ضرورت

- ضروریات

- نیٹ ورک

- نیٹ ورکنگ

- نئی

- متعدد

- of

- on

- آپشنز کے بھی

- احکامات

- دیگر

- دیگر

- خود

- پیرامیٹرز

- کارکردگی

- جسمانی

- جسمانی طورپر

- پلیٹ فارم

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوسٹ

- ممکنہ

- طاقت

- طاقتور

- خوبصورت

- عمل

- عمل

- پروسیسنگ

- مصنوعات

- خالص

- دھکیل دیا

- دھکیلنا

- رینج

- بلکہ

- اصلی

- کو کم کرنے

- نقل تیار

- نقل

- ذمہ داری

- نتیجہ

- سواری

- جڑ

- سیفٹی

- سیمکولیٹر

- اہم

- بعد

- ایک

- سست

- سست

- چھوٹے

- So

- سافٹ ویئر کی

- ویرل میٹرکس

- خصوصی

- کے لئے نشان راہ

- معیار

- شروع

- مرحلہ

- ابھی تک

- بند کرو

- ذخیرہ

- پتہ چلتا ہے

- حمایت

- کے نظام

- سسٹمز

- کاموں

- ٹیموں

- تکنیک

- ٹیکنالوجی

- بتاتا ہے

- کہ

- ۔

- یہ

- کے ذریعے

- تھرو پٹ

- وقت

- کرنے کے لئے

- آج

- آج کا

- کل

- رجحان

- رجحانات

- ٹریلین

- بھروسہ رکھو

- ٹرننگ

- اقسام

- کے تحت

- یونٹ

- کی طرف سے

- وزن

- اچھا ہے

- جس

- وسیع

- وسیع رینج

- گے

- جیت

- ساتھ

- کے اندر

- کام کر

- سال

- سال

- زیفیرنیٹ