A technical paper titled “WWW: What, When, Where to Compute-in-Memory” was published by researchers at Purdue University.

Анотація:

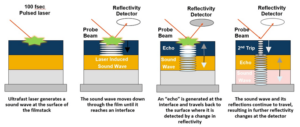

“Compute-in-memory (CiM) has emerged as a compelling solution to alleviate high data movement costs in von Neumann machines. CiM can perform massively parallel general matrix multiplication (GEMM) operations in memory, the dominant computation in Machine Learning (ML) inference. However, re-purposing memory for compute poses key questions on 1) What type of CiM to use: Given a multitude of analog and digital CiMs, determining their suitability from systems perspective is needed. 2) When to use CiM: ML inference includes workloads with a variety of memory and compute requirements, making it difficult to identify when CiM is more beneficial than standard processing cores. 3) Where to integrate CiM: Each memory level has different bandwidth and capacity, that affects the data movement and locality benefits of CiM integration.

In this paper, we explore answers to these questions regarding CiM integration for ML inference acceleration. We use Timeloop-Accelergy for early system-level evaluation of CiM prototypes, including both analog and digital primitives. We integrate CiM into different cache memory levels in an Nvidia A100-like baseline architecture and tailor the dataflow for various ML workloads. Our experiments show CiM architectures improve energy efficiency, achieving up to 0.12x lower energy than the established baseline with INT-8 precision, and upto 4x performance gains with weight interleaving and duplication. The proposed work provides insights into what type of CiM to use, and when and where to optimally integrate it in the cache hierarchy for GEMM acceleration.”

Знайти технічний документ тут. Опубліковано грудень 2023 р. (препринт).

Sharma, Tanvi, Mustafa Ali, Indranil Chakraborty, and Kaushik Roy. “WWW: What, When, Where to Compute-in-Memory.” arXiv preprint arXiv:2312.15896 (2023).

Пов'язане читання

Підвищення енергоефективності ШІ за допомогою обчислень у пам’яті

Як обробляти робочі навантаження zettascale і залишатися в межах фіксованого бюджету електроенергії.

Моделювання обчислень у пам’яті з біологічною ефективністю

Generative AI змушує виробників чіпів використовувати обчислювальні ресурси більш розумно.

SRAM In AI: The Future Of Memory

Why SRAM is viewed as a critical element in new and traditional compute architectures.

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- PlatoData.Network Vertical Generative Ai. Додайте собі сили. Доступ тут.

- PlatoAiStream. Web3 Intelligence. Розширення знань. Доступ тут.

- ПлатонЕСГ. вуглець, CleanTech, Енергія, Навколишнє середовище, Сонячна, Поводження з відходами. Доступ тут.

- PlatoHealth. Розвідка про біотехнології та клінічні випробування. Доступ тут.

- джерело: https://semiengineering.com/cim-integration-for-ml-inference-acceleration/

- : має

- :є

- :де

- $UP

- 1

- 2023

- a

- прискорення

- досягнення

- AI

- полегшувати

- an

- та

- Відповіді

- архітектура

- AS

- At

- ширина смуги

- Базова лінія

- корисний

- Переваги

- обидва

- бюджет

- by

- cache

- CAN

- потужність

- переконливий

- обчислення

- обчислення

- витрати

- критичний

- дані

- Грудень

- визначення

- різний

- важкий

- цифровий

- домінуючий

- кожен

- Рано

- ефективність

- елемент

- з'явився

- енергія

- енергоефективності

- встановлений

- оцінка

- Експерименти

- дослідити

- фіксованою

- для

- Війська

- від

- майбутнє

- прибуток

- Загальне

- даний

- тут

- ієрархія

- Високий

- Однак

- HTTPS

- ідентифікувати

- удосконалювати

- in

- includes

- У тому числі

- розуміння

- інтегрувати

- інтеграція

- в

- IT

- JPG

- ключ

- вивчення

- рівень

- рівні

- знизити

- машина

- навчання за допомогою машини

- Машинки для перманенту

- Робить

- масово

- Матриця

- пам'ять

- ML

- більше

- руху

- безліч

- необхідний

- Нові

- Nvidia

- of

- on

- відкрити

- операції

- наші

- Папір

- Паралельні

- виконувати

- продуктивність

- перспектива

- plato

- Інформація про дані Платона

- PlatoData

- позах

- влада

- Точність

- процес

- обробка

- запропонований

- Прототипи

- забезпечує

- опублікований

- питань

- про

- Вимога

- Дослідники

- ресурси

- Рой

- Показувати

- рішення

- standard

- залишатися

- придатність

- Systems

- технічний

- ніж

- Що

- Команда

- Майбутнє

- їх

- Ці

- це

- під назвою

- до

- традиційний

- тип

- університет

- використання

- різноманітність

- різний

- переглянуті

- з

- було

- we

- вага

- Що

- коли

- з

- в

- Work

- зефірнет