Дослідники Лундського університету опублікували технічну статтю під назвою «Сегнетоелектричні тунельні мемристори для обчислювальних прискорювачів у пам’яті».

Анотація:

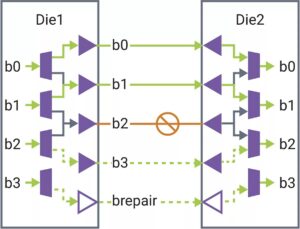

«Нейроморфні обчислення викликали великий інтерес, оскільки стрибки в додатках штучного інтелекту (ШІ) виявили обмеження через важкий доступ до пам’яті з обчислювальною архітектурою фон Неймана. Паралельні обчислення в пам’яті, що забезпечуються нейроморфними обчисленнями, можуть значно зменшити затримку та енергоспоживання. Ключем до аналогового нейроморфного обчислювального обладнання є мемристори, що забезпечують енергонезалежні рівні провідності в багатьох станах, високу швидкість перемикання та енергоефективність. Мемристори із сегнетоелектричним тунельним переходом (FTJ) є основними кандидатами для цієї мети, але вплив конкретних характеристик на їх продуктивність при інтеграції у великі поперечні масиви, основний обчислювальний елемент як для висновків, так і для навчання глибоких нейронних мереж, вимагає ретельного дослідження. У цій роботі W/Hf x Zr1-x O2/TiN FTJ з 60 програмованими станами провідності, динамічним діапазоном (DR) до 10, щільністю струму >3 А м-2 at V зчитування = 0.3 В і сильно нелінійний струм-напруга (I–V) характеристик (>1100) експериментально продемонстровано. За допомогою макромоделі схеми оцінюється продуктивність справжнього поперечного масиву на системному рівні та досягається 92% точності класифікації модифікованого набору даних Національного науково-технічного інституту (MNIST). Нарешті, низька провідність у поєднанні з високою нелінійністю I–V характеристики дозволяють реалізувати великі масиви поперечних панелей без селекторів для нейроморфних апаратних прискорювачів».

Знайти технічний документ тут. Опубліковано грудень 2023 р.

Атл, Р. і Борг, М. (2023), Сегнетоелектричні тунельні мемристори для обчислювальних прискорювачів у пам’яті. Adv. Intell. сист. 2300554. https://doi.org/10.1002/aisy.202300554

Пов'язане читання

Підвищення енергоефективності ШІ за допомогою обчислень у пам’яті

Як обробляти робочі навантаження zettascale і залишатися в межах фіксованого бюджету електроенергії.

Моделювання обчислень у пам’яті з біологічною ефективністю

Generative AI змушує виробників чіпів використовувати обчислювальні ресурси більш розумно.

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- PlatoData.Network Vertical Generative Ai. Додайте собі сили. Доступ тут.

- PlatoAiStream. Web3 Intelligence. Розширення знань. Доступ тут.

- ПлатонЕСГ. вуглець, CleanTech, Енергія, Навколишнє середовище, Сонячна, Поводження з відходами. Доступ тут.

- PlatoHealth. Розвідка про біотехнології та клінічні випробування. Доступ тут.

- джерело: https://semiengineering.com/ferroelectric-tunnel-junctions-in-crossbar-array-analog-in-memory-compute-accelerators/

- : має

- :є

- $UP

- 10

- 1100

- 2023

- 60

- a

- прискорювачі

- доступ

- точність

- досягнутий

- AI

- та

- застосування

- архітектура

- ЕСТЬ

- масив

- штучний

- штучний інтелект

- Штучний інтелект (AI)

- AS

- At

- обидва

- бюджет

- але

- by

- кандидатів

- характеристика

- класифікація

- близько

- поєднання

- обчислення

- обчислення

- споживання

- Core

- Поточний

- Грудень

- глибокий

- глибокі нейронні мережі

- продемонстрований

- Щільність

- цифровий

- dr

- два

- динамічний

- ефективність

- елемент

- включіть

- енергія

- енергоефективності

- оцінюється

- піддаватися

- в кінці кінців

- фіксованою

- для

- Війська

- великий

- апаратні засоби

- Мати

- важкий

- тут

- Високий

- дуже

- HTTPS

- ідентифікатор

- Impact

- удосконалювати

- in

- Інститут

- інтеграція

- Інтелект

- інтерес

- в

- дослідження

- ключ

- великий

- Затримка

- стрибки

- рівень

- рівні

- недоліки

- низький

- пам'ять

- модифікований

- більше

- народ

- мереж

- Нейронний

- нейронні мережі

- Нові

- об'єкт

- of

- on

- відкрити

- Папір

- Паралельні

- приватність

- продуктивність

- plato

- Інформація про дані Платона

- PlatoData

- потенціал

- влада

- Prime

- процес

- програмований

- за умови

- забезпечення

- опублікований

- мета

- R

- діапазон

- реалізація

- Вимагається

- Дослідники

- ресурси

- наука

- Наука і технології

- бачив

- істотно

- швидкість

- Штати

- залишатися

- система

- технічний

- Технологія

- Команда

- їх

- це

- під назвою

- до

- Навчання

- правда

- тунель

- університет

- на

- використання

- використання

- з

- було

- з

- в

- Work

- зефірнет